# MONOLITHIC INTEGRATION OF JUNCTION FIELD EFFECT TRANSISTOR AND NANOELECTROMECHANICAL SYSTEMS

# A Dissertation

Presented to the Faculty of the Graduate School of Cornell University

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

by

Kwame Amponsah

January 2014

# MONOLITHIC INTEGRATION OF JUNCTION FIELD EFFECT TRANSISTOR AND NANOELECTROMECHANICAL SYSTEMS

#### KWAME AMPONSAH, Ph. D.

# Cornell University 2014

The mechanical motion of most NEMS/MEMS devices has to be transduced to electrical domain by using active or passive components. In passive transduction, resistors, capacitors and inductors are used to sense the motional current which is then converted to voltage. In active sensing, transistors are also used for the conversion process. Since transistors can offer enhanced gain through transconductance, they can increase small signals into larger signals that can be less susceptible to systematic and innate noise sources.

The active components can be integrated into the NEMS device either by monolithic integration or through a two chip solution. In monolithic integration, both the active device and the NEMS devices are fabricated on the same substrate, using short thin film interconnects, minimizing parasitics. In the two-chip solution, the active and NEMS components are fabricated on separate wafers and the individual dices are wire-bonded, or flip chip bonded which can have higher parasitics and generate mismatches in the system. One of the goals of this thesis is to monolithically integrate JFETs into N/MEMS components to enhance signal transduction.

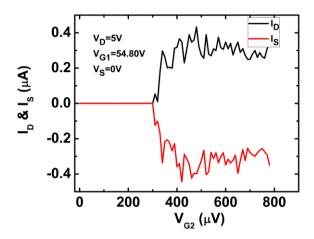

The dissertation begins with the characterization of an SOI pre-biased NEMS electrostatic switch with a pre-biased voltage of 54.8 V and a switching voltage as low as 300  $\mu$ V. The contact resistance of the switch was 4.3 M $\Omega$  due to the Si-to-Si contact used in the switch. Later, to reduce the contact resistance, MoSi<sub>2</sub> was used as a

structural layer and Cr and Pt were sputtered on the switch to produce Pt-to-Pt contact. The measured contact resistance was reduced to 1  $K\Omega$ .

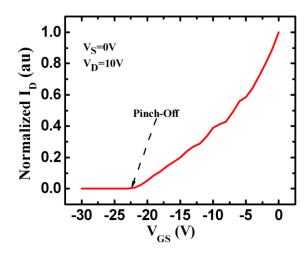

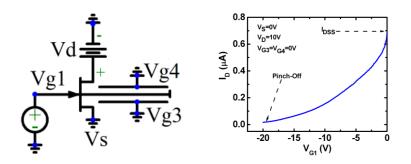

A Junction Field Effect Transistor (JFET) was integrated into the switches to enable the sensing of the displacement of the moving structure. The JFETs had a pinch-off voltage of -19 V (at  $V_{DS}$ =10 V) and a transconductance parameter of 1.9 mA/V² (at  $V_{DS}$ =10 V). These JFETs were monolithically integrated into the switch to minimize parasitics. The JFET was then incorporated into a nanoscale multiple-tip prober which was used for atomic imaging of Highly Ordered Pyrolytic Graphite (HOPG) as well as performing conductance measurements of HOPG. The JFET along with capacitive sensing was used to sense the motion of the movable tip. The resonating tip had a resonance frequency of 293 kHz and the tip radius of <50 nm. Currently, commercial Scanning Probe Microscopes (SPM) such as STM and AFM use a single tip for scanning which limits its use to static electrical measurements. This dissertation presents the development of a novel SPM that uses the multiple tips for scanning and performing dynamic transport measurements.

## **BIOGRAPHICAL SKETCH**

Kwame Amponsah was born on April 18<sup>th</sup> 1981 in Sekondi, a small city located in the Western Region of Ghana. However, he grew up in Takoradi, a few minutes' drive from Sekondi, with his seven siblings. Kwame did high school at Mfantsipim School which is an all-boy boarding school located in Cape Coast in the central region of Ghana. After graduating from high school, he worked with his dad, who was then involved in the export industry, and subsequently decided to pursue an undergraduate education in the United States of America. He started his undergraduate education at Cornell University in 2003 and quickly fell in love with Ithaca. Ithaca has since been his home away from home where he has enjoyed the eateries, the beautiful sceneries, the locals and frequenting the Commons. At Cornell, he worked as a research assistant at the Cornell Nanoscale Facility and it was this exposure to undergraduate research that motivated him to pursue graduate school. He joined Prof. Edwin Kan's group for his Masters of Engineering degree in 2007 for which he investigated the use of flash memory technology for biological sensing. In 2008, he began his doctoral education under the supervision of Prof. Amit Lal. He has since been researching the monolithic integration of Junction Field Effect Transistors into MEMS/NEMS platforms.

To My Dada and Mama

## **ACKNOWLEDGMENTS**

Ithaca...my home away from home. I have benefited vastly from the people I have met and the generosity of various funding institutions and agencies. I remember back home in Ghana, I could only dream of travelling to the land of opportunity to pursue a college degree and let alone an advanced degree. Yet, the dream became reality the moment I received my offer from Cornell University to pursue my undergraduate degree. In that regards, the International Students Office was very generous in offering me a full tuition scholarship for which I am very grateful. I quickly assimilated to the American culture thanks to my undergraduate friends (Shawn Darrah, Alex O'Day, my roommate Soutrik Pramanik and many more).

My real interest in research started in the summer of 2004 when I wandered around the offices of the Cornell Nanoscale Facility looking for a summer job. I was hired by Dr. Mandy Esch to assist her in microfluidic research. Little did I know that my path forward would be engulfed with countless hours in the cleanroom, having midnight conversations with frustrated doctoral students who were waiting eagerly to jump on the equipment of individuals who had reserved spots, but had failed to show up. At that point, I realized I enjoyed research very much and decided to continue on that path. I am very grateful to Dr. Esch for offering me that opportunity which became a life changing event for me.

Being home away from home could sometimes be very lonely and that is when the Ghanaian community at Cornell was there to support me. Thank you Betsy Ampofo, Robert Mereku, David Agyeman-Budu, Obafemi Otelaja, Dela Kusi-Appouh, Nii Lante Amissah, Naa Lante Amissah, Oluranti Campbell, and David Korda for all the cooking and the good times we shared. I also enjoyed the pleasant company of Chimaobi Onuchekwuah, Majed Al-Mashad and Xiao Wang. We had fond memories and hopefully we will meet again on the Hill at subsequent reunion events. Special

thanks to Yamilet Echeverria for being there for me during the good and bad times. I enjoyed your delicious cooking, travelling together to conferences and spending quality time together. I appreciate all the love and support which made my graduate school experience less stressful and amazing one!

I would also like to extend my gratitude to Daniel Richter, Sue Bulkley and Scott Coldren for being patient with me and handling all my departmental paper work. I cannot forget Patty Gonyea and Penny Burke for always putting a smile on my face. Dan Stone, you are funny my friend!! Your morning jokes lightened my often hectic days and I look forward to getting a hunting license so that I can go deer hunting with you.

Additionally, many thanks go out to the awesome staff at the Cornell Nanoscale Facility. I would like to particularly thank Meredith Metzler and Vince Genova for helping me design various etching recipes. Where there is free food on campus, you are guaranteed to see poor graduate students...thanks Kathy Springer for constantly saving me some. The rest of the staff I would like to thank includes Mick Thomas, John L. Grazul, Jon Shu and Steve Kriske for all their help and support with TEM, FIB and XPS. I would also like to extend my appreciation to Prof. Muna Ndulo, Jackie Sayegh and Evangeline Ray who are all at the Institute for African Development (IAD) for their support.

Moreover, I would like to thank the previous and current members of SonicMEMS Laboratory; Hadi Hosseinzadegan, Jason Thomas Hoople, Joseph Patrick Miller, June Ho Hwang, Justin C Kuo, Po-Cheng Chen, Sachin Prakash Nadig, Sarvani Piratla, Ved Vishwas Gund, Yuerui Lu, Serhan Mehmet Ardanuc, Ramkumar Abhishek, Alper Yusuf Bozkurt, Muhammet Kursad Araz, Norimasa Yoshimizu, Steven Xiaoqiang Tin, Venkata Siva Prasad Pulla, Ching-Ping Janet Shen, Yue Shi and Shankar Radhakrishnan.

In addition, I also enjoyed my many interactions with the OxideMEMS group; Prof. Sunil Bhave, Tiffany Cheng, Sid Tallur, Benjamin Tang, Renyuan(Ryan) Wang, Ajay Bhat, Tanay Gosavi, Hengky Chandrahalim, Dana Weinstein, Eugene Hwang and Suresh Sridaran.

Throughout my time here, I have grown personally and professionally and the most important person attributable to this growth process was my academic advisor Prof. Amit Lal. I am forever grateful to you for serving as an amazing advisor and a great mentor, especially for exercising extreme patience in reviewing my publications and providing feedback. I would additionally like to thank you for all the personal advice and coaching you offered me which at times proved to be life changing. Your intelligence is unmatched and I am happy to have worked under your leadership. I would also like to thank my committee members, Prof. Sandip Tiwari, Prof. Clifford Pollock and Prof. Alyosha Molnar for their support and advice.

Furthermore, I would like to thank my funding agencies since without their support it would have been nearly impossible to pursue this advanced degree. Thanks to the Institute for African Development (IAD), Cornell Center for Materials Research (CCMR) and United States Army Research Laboratory (ARL).

Finally, I would like to thank my dad, mom and siblings for their unwavering love and support throughout the years. Irene and Eric, I am eternally grateful for all the Ghanaian food that you provided when I got home-sick. Mama, thank you for the spiritual support and I would like you to know that I am still holding on to the Biblical verse:

"Finally, brothers and sisters, whatever is true, whatever is noble, whatever is right, whatever is pure, whatever is lovely, whatever is admirable—if anything is excellent or praiseworthy—think about such things."

# **Table of Contents**

| Chapter 1                                                             | 1  |

|-----------------------------------------------------------------------|----|

| 1.1 Integration of Transistors into Nano-Electro-Mechanical-Systems   | 1  |

| 1.2 Passive Sensing (two-chip Solution: Sensing of micro transducers) | )2 |

| 1.3 Active Sensing: Transistor Level Motion Transduction              | 6  |

| 1.4 Scope of Dissertation                                             | 9  |

| Chapter 2                                                             | 11 |

| 2.1 Introduction                                                      | 11 |

| 2.2 Non-Pull-In Nano-Electro-Mechanical Switch                        | 12 |

| 2.3 Fabrication of Switch                                             | 15 |

| 2.4 Measurement Results                                               | 16 |

| 2.4.1 Full-Contact Voltage                                            | 17 |

| 2.4.2 Switching Voltage                                               | 18 |

| 2.5 Energy Consumption in Switch                                      | 21 |

| 2.6 MoSi <sub>2</sub> Based NEMS Switches                             | 26 |

| 2.6.1 Drain Voltage Modulation of Turn-on Voltage                     | 30 |

| 2.6.2 Endurance Test                                                  | 32 |

| 2.6.3 Pt Coated Electrostatic Switches                                | 33 |

| 2.7 Conclusions                                                       | 35 |

| Chapter 3                                                             | 36 |

| 3.1 Introduction                                                      | 36 |

| 3.2 Integrated Junction Field Effect Transistor with NEMS             | 36 |

| 3.2.1 Device Modeling of JFET                             | 39 |

|-----------------------------------------------------------|----|

| 3.2.2 Device Modeling of NEMS                             | 41 |

| 3.3 JFET/NEMS Fabrication                                 | 44 |

| 3.4 Measurements                                          | 46 |

| 3.4.1 DC Measurements                                     | 46 |

| 3.4.2 Motion Sensing                                      | 47 |

| 3.5 Noise in JFET                                         | 53 |

| 3.5.1 Noise Measurement                                   | 55 |

| 3.6 f <sub>T</sub> of the JFET                            | 60 |

| 3.7 Conclusions                                           | 63 |

| Chapter 4                                                 | 64 |

| 4.1 Introduction                                          | 64 |

| 4.2 Nanogap Multi-Electrode Atom and Conductivity Prober  | 66 |

| 4.2.1 JFET Current Contribution due to Floating Potential | 68 |

| 4.2.2 Current Contribution due to Strain                  | 69 |

| 4.2.3 Mechanical Actuation Simulation                     | 71 |

| 4.3 Prober Fabrication                                    | 72 |

| 4.4 Prober Characterization                               | 73 |

| 4.4.1 Resonance Frequency Measurement                     | 73 |

| 4.4.2 Inter-Tip Gap Modulation                            | 76 |

| 4.4.3 IV Characteristics of the JFET                      | 77 |

| 4.4.4 Sensing the Motion of the Moving Probe through the JFET79          |

|--------------------------------------------------------------------------|

| 4.4.5 Atomic Imaging                                                     |

| 4.4.6 Conductance Measurement                                            |

| 4.5 Conclusions                                                          |

| Chapter 5                                                                |

| 5.1 Scanning Probe System (SPS)                                          |

| 5.1.1 Overview of the Scanning Probe System                              |

| 5.1.2 Hardware                                                           |

| 5.1.3 Operation of SPS                                                   |

| 5.1.4 Software                                                           |

| 5.1.5 Results                                                            |

| 5.2 Future Work94                                                        |

| 5.3 Conclusions95                                                        |

| Chapter 6 Appendix 96                                                    |

| 6.1 Energy Consumed in the Switching Process of a NEMS Switch96          |

| 6.2 Newton Method for Solving the Floating Potential on the Cantilever98 |

| 6.3 Newton Method for Solving a System of >=n Nonlinear Equations for r  |

| Variables by Kyle J. Drerup                                              |

| 6.4 Resonance Frequency of the STM Probe Tip102                          |

| Chapter 7 References                                                     |

# LIST OF FIGURES

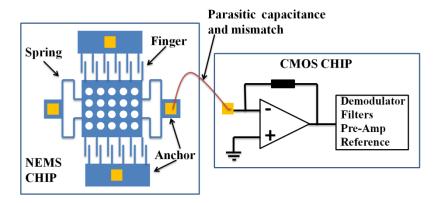

| Figure 1.1. Two-chip solution resulting in the integration of NEMS and ASIC. The wire bond introduces capacitive parasitic as well as mismatch at the input port of the amplifier.                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

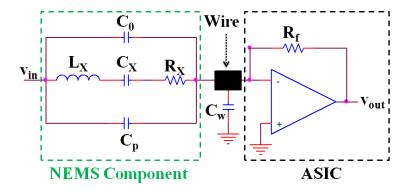

| Figure 1.2. Schematic of the two-chip solution where the NEMS component is wire-bonded to an off-chip transimpedance amplifier                                                                                                                                                                                                                                                                                                 |

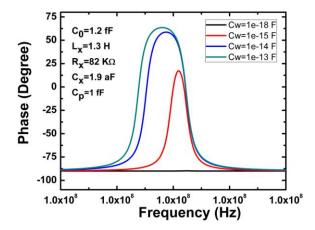

| Figure 1.3. Plot of phase vs. frequency illustrating the effect of the parasitic capacitance on the resonance frequency of the NEMS resonator. The parasitic capacitance tends to shift the resonance frequency as well as decreases the phase shift at resonance of the resonator.                                                                                                                                            |

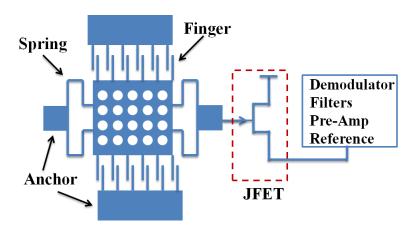

| Figure 1.4. Monolithic integration of MEMS accelerometer structure with FETs results in the elimination of the wire-bond parasitic, replaced by the much smaller interconnect parasitic capacitance                                                                                                                                                                                                                            |

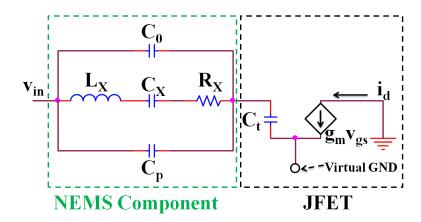

| Figure 1.5. Small signal electrical equivalent of the JFET integrated with the NEMS resonator                                                                                                                                                                                                                                                                                                                                  |

| Figure 1.6. The JFET gate voltage results from the voltage divider between the JFET and NEMS impedances.                                                                                                                                                                                                                                                                                                                       |

| Figure 2.1. Schematic of the switch architecture demonstrated by Yang et al. The gate electrode was pre-charged and the voltage that is applied to the substrate increases the charge on the pre-charge electrode [18].                                                                                                                                                                                                        |

| Figure 2.2. (a) and (b) show the side and top views of the nanoswitch with a contact gap of about 300 nm                                                                                                                                                                                                                                                                                                                       |

| Figure 2.3. The schematic of the NEMS switch which shows the source, drain and gate terminals as well as the air gaps                                                                                                                                                                                                                                                                                                          |

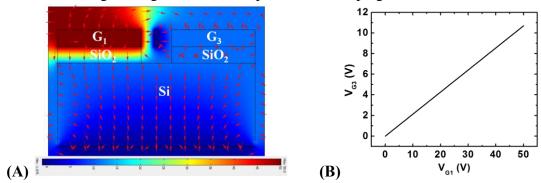

| Figure 2.4. (A) $COMSOL^{\otimes}$ electrostatics simulation of the feedthrough effect that is generated when voltage ramps are applied to $G_1$ . The electric field lines couple through air and the $SiO_2$ layer to terminate on $G_3$ . The acquired floating potential on $G_3$ provides additional restoring force to the cantilever. (B) As $V_{G1}$ is ramped, electrode $G_3$ acquires a floating potential $V_{G3}$ |

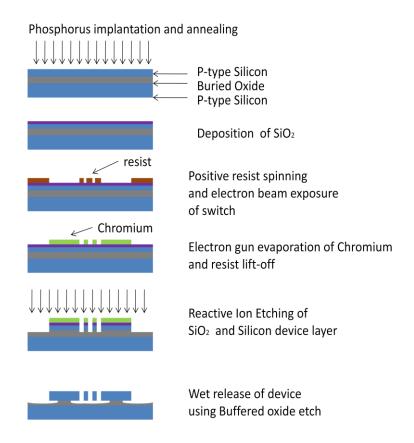

| Figure 2.5. Fabrication steps for the Si-Si switch which involves e-beam patterning, metal lift-off, etching and CPD. The phosphorus implantation of the p-type device layer forms a PN-junction in the device layer of the SOI wafer                                                                                                                                                                                          |

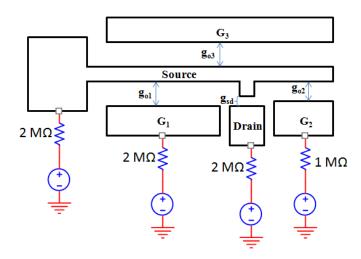

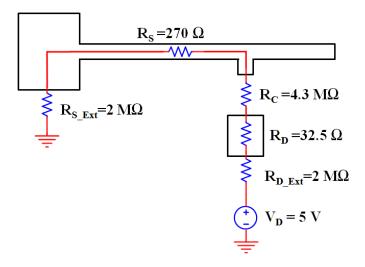

| Figure 2.6. Testing scheme for the nanoswitch which shows the biasing of the terminals with current limiting resistors.                                                                                                                                                                                                                                                                                                        |

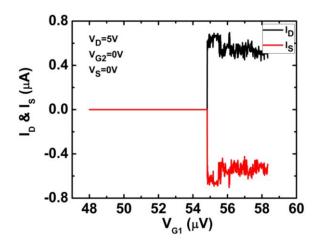

| Figure 2.7. $I_d$ versus $V_{G1}$ for device 2. $V_{G1,Contact}$ is measured to be 54.82 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.8. With $V_{G1,prebias} = 54.80$ V and switch contacts at $V_{G2} = 300$ $\mu$ V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 2.9. Resistive model used to evaluate the contact resistance of the switch 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 2.10. When $V_{G1}$ is applied, there is a distributed load on the cantilever just opposite to the electrode $G_1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

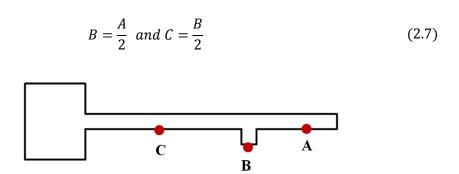

| Figure 2.11. The displacement values at G <sub>2</sub> (A), at the contact dimple (B) and at G <sub>1</sub> (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

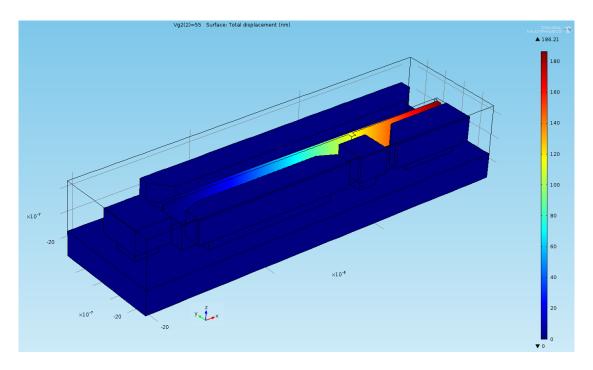

| Figure 2.12. 3D COMSOL® simulation to evaluate the displacement of the cantilever with applied voltage to G <sub>1</sub> . The device layer of the switch is silicon and it sits on a SiO <sub>2</sub> layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 2.13. The displacement relationship between the tip of the cantilever and the contact dimple.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

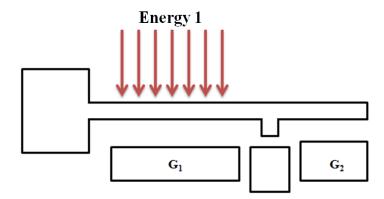

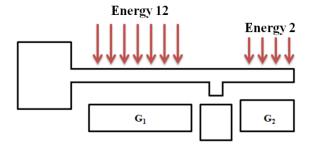

| Figure 2.14. Energy distribution along the cantilever. As $V_{G2}$ is applied, there is additional energy, Energy 12, generated at electrode $G_1$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

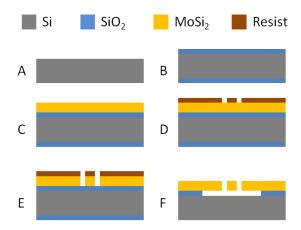

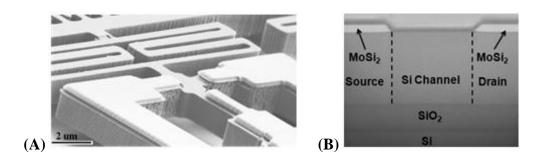

| Figure 2.15. Fabrication of the MoSi <sub>2</sub> NEMS switch. A) n-type silicon wafer By LPCVD oxide was grown on each side of the wafer at a temperature of 1100 °C with 5% HCL. C) MoSi <sub>2</sub> was sputter deposited on the wafer at a chamber pressure of 2 mTorr and DC power of 1.5 KW. Ar gas was introduced during the deposition. Dy Negative tone resist was spun and exposed with ASML 300C DUV stepper. E) The MoSi <sub>2</sub> layer was dry etched with Cl <sub>2</sub> /O <sub>2</sub> chemistry. F) Resist strip and device release was carried out using Buffered Oxide Etch (BOE 6:1) and after rinsing in de-ionized water, the device was dried in a critical point dryer |

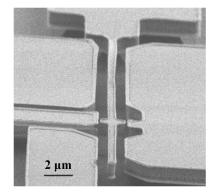

| Figure 2.16. SEM image of the fully released free standing MoSi <sub>2</sub> switch. As seen in the image, there is minimal stress gradient in the source cantilever                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

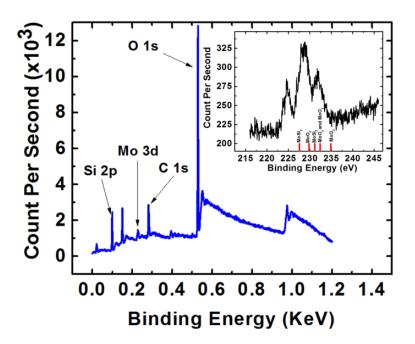

| Figure 2.17. XPS scan of the MoSi <sub>2</sub> surface shows peaks for silicon, Mo 3d, oxygen and the adventitious hydrocarbon. The 2.95 eV shift in the O 1s peak was used to compensate for this measured results. The inset is a high resolution scan which shows the presence of the Mo 3d <sub>5/2</sub> and Mo 3d <sub>3/2</sub> of the consolidated MoSi <sub>2</sub>                                                                                                                                                                                                                                                                                                                         |

| Figure 2.18. Increasing the drain voltage generates additional electric field that attracts the source to contact the drain terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

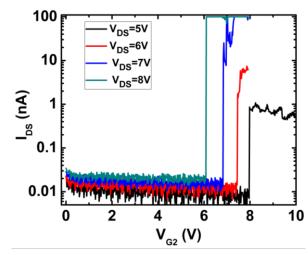

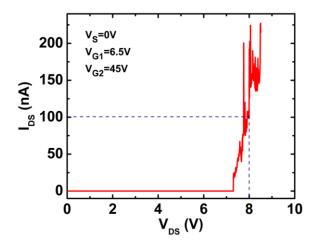

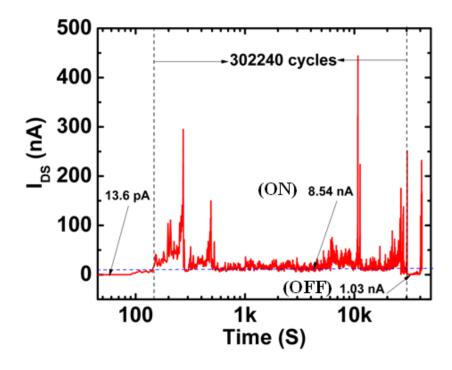

| Figure 2.19. Current-Voltage measurement of the source-drain terminals of the closed switch shows that active current conduction begins at V <sub>DS</sub> =7.3 V31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 2.20. Endurance test of the switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 2.21. SEM image of the MoSi <sub>2</sub> switch which is coated with 10nm/200nm of Cr/Pt                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

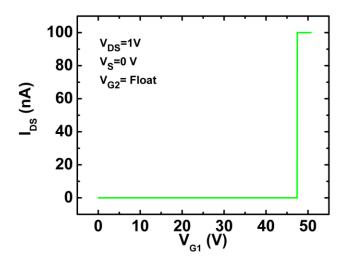

| Figure 2.22. Voltage ramps were applied to $G_1$ until the source was in full contact with the drain. The $G_1$ contact voltage was 47.5 V and the OFF state drain current was 1.4 pA. The current compliance was set to 100 nA                                                                                                                                                                                                                                                                                                                                 |

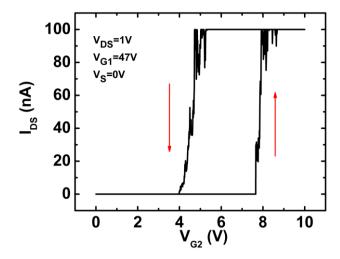

| Figure 2.23. With the device pre-biased at 47 V, voltage ramps were applied to G <sub>2</sub> to fully bring the source in contact with the drain. The current compliance was set to 100 nA                                                                                                                                                                                                                                                                                                                                                                     |

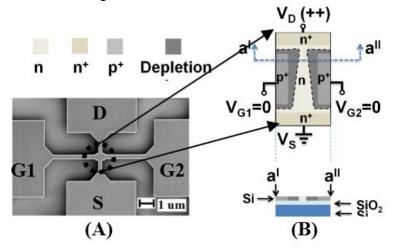

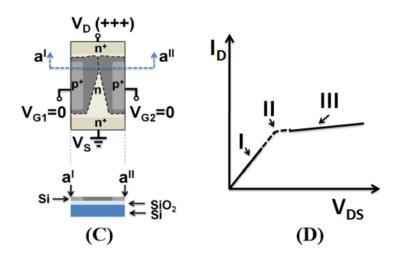

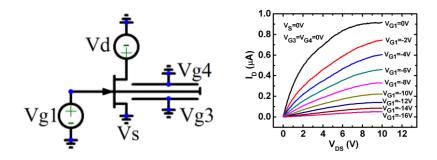

| Figure 3.1. (A) SEM image of 4-terminal JFET. (B) As a lager V <sub>DS</sub> is applied, the gate-channel depletion region gets wider and pushes into the channel as a result increasing the channel resistance. (C) Pinch-off is reached when the area around the drain is fully depleted and further increase in V <sub>DS</sub> has insignificant change in the drain current. The drain current saturates. (D) IV characteristics for zero gate voltage. Region I is for case (A), region II is for case (B) and region III represents the situation in (C) |

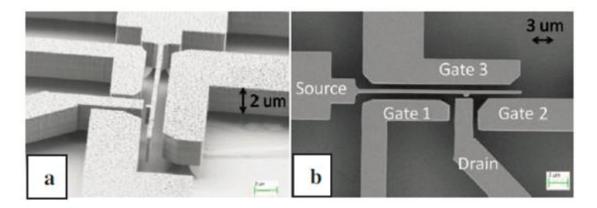

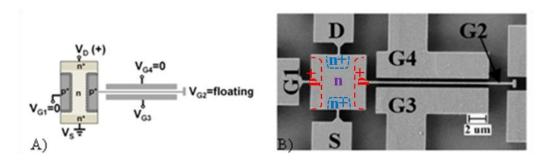

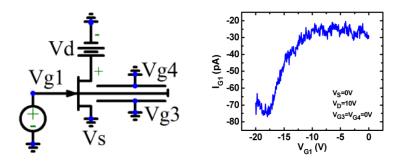

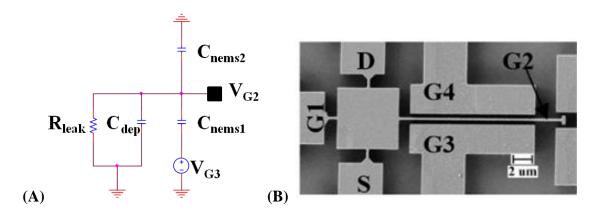

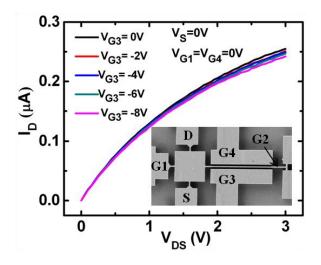

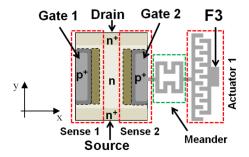

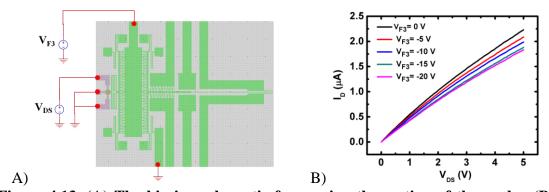

| Figure 3.2. (A) Schematic of the JFET-MEMS device. With applied V <sub>G3</sub> , G <sub>2</sub> (cantilever) acquires a floating potential, which is able to modulate the channel conductance of the JFET. (B) SEM image of the device.                                                                                                                                                                                                                                                                                                                        |

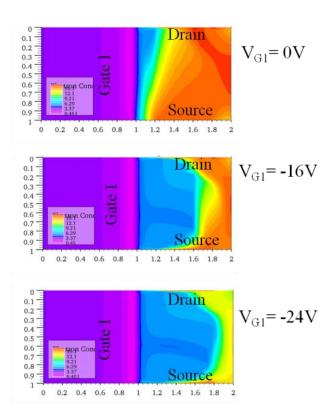

| Figure 3.3. Atlas <sup>®</sup> software was used to evaluate the pinch-off voltage of the JFET. The channel area was 1 $\mu$ m by 1 $\mu$ m with an n-type channel doping of 4.16x10 <sup>14</sup> ions/cm <sup>3</sup> . The source, drain and gate doping were degenerate (1x10 <sup>20</sup> ions/cm <sup>3</sup> ) 40                                                                                                                                                                                                                                       |

| Figure 3.4. The pinch-off voltage was simulated to be -22.5 V which is close to the measured value of -19 V                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

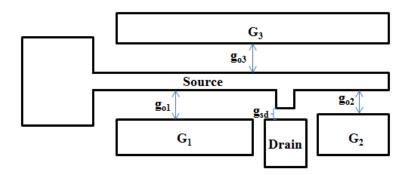

| Figure 3.5. Schematic of the NEMS switch showing the gates, source, drain and air gaps                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

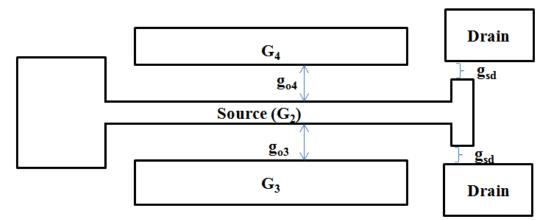

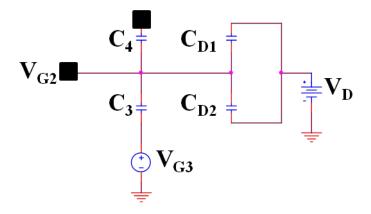

| Figure 3.6. Capacitive model for the NEMS component of the device. The cantilever and electrode G <sub>4</sub> are electrically floating                                                                                                                                                                                                                                                                                                                                                                                                                        |

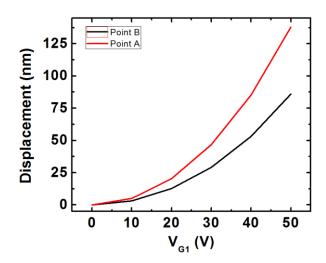

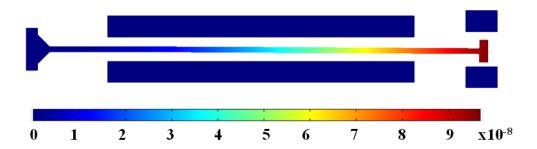

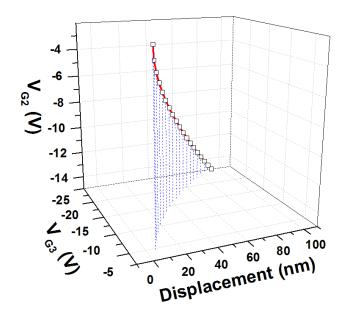

| Figure 3.7. COMSOL <sup>®</sup> multiphysics software was used to simulate the bending of the cantilever as voltage ramps were applied to $G_3$ . With $V_{G3}$ = -16 V, the free tip of the cantilever displaces 60 nm                                                                                                                                                                                                                                                                                                                                         |

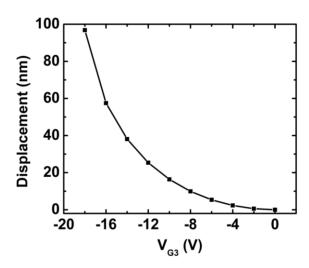

| Figure 3.8. A plot of cantilever tip displacement vs. V <sub>G3</sub> as voltage ramps are applied to G <sub>3</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                            |

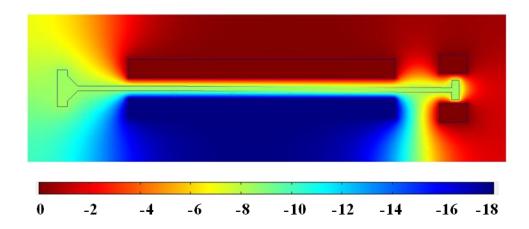

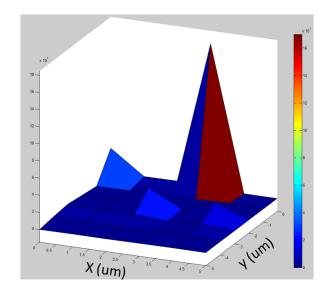

| Figure 3.9. The electrostatic potential distribution surrounding the switch when voltage ramps were applied to $G_3$                                                                                                                                                                                                                                                                                                                                                                                                                                            |

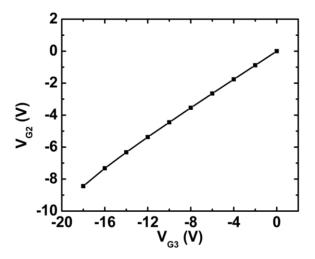

| Figure 3.10. A plot of the floating potential on the cantilever as voltage ramps were applied to G <sub>3</sub>                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

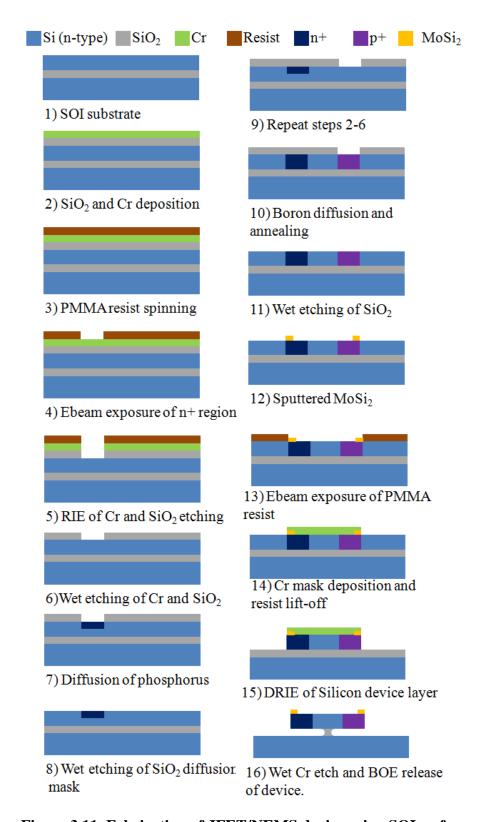

| Figure 3.11. Fabrication of JFET/NEMS device using SOI wafer                                                                                                                                                                                                                                                                                                                                        |

| Figure 3.12. Measured $I_{DS}$ vs. $V_{DS}$ output curves for JFET/NEMS device. The measured low current is due to the high drain and source resistances                                                                                                                                                                                                                                            |

| Figure 3.13. Transfer curve for the JFET/NEMS device biased at V <sub>DS</sub> =10 V46                                                                                                                                                                                                                                                                                                              |

| Figure 3.14. The gate leakage current when the JFET was turned off was ~70 pA47                                                                                                                                                                                                                                                                                                                     |

| Figure 3.15. (A) Equivalent electrical model of JFET-NEMS device. The gate potential at JFET G <sub>2</sub> is due to capacitive divider from G <sub>3</sub> to JFET source (B) SEM micrograph for the JFET-NEMS device                                                                                                                                                                             |

| Figure 3.16. The applied voltage $V_{G3}$ generates an electrostatic force of attraction between the cantilever and $G_3$ . This electrostatic force causes the cantilever to displace and the capacitive coupling in the air gaps produces a floating potential $V_{G2}$ . As $V_{G3}$ increases, the displacement of the cantilever also increases and the floating potential $V_{G2}$ increases. |

| Figure 3.17. The JFET-NEMS device is able to sense the motion of the clamp-free cantilever as voltage ramps are applied to G <sub>3</sub>                                                                                                                                                                                                                                                           |

| Figure 3.18. The JFET-NEMS device is able to sense the motion of clamp-clamp cantilever                                                                                                                                                                                                                                                                                                             |

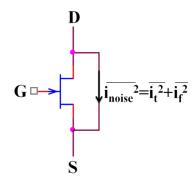

| Figure 3.19. Equivalent noise circuit for the JFET                                                                                                                                                                                                                                                                                                                                                  |

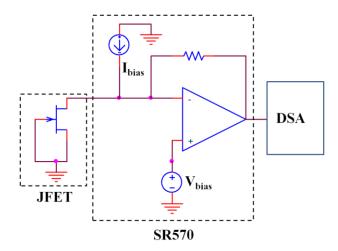

| Figure 3.20. Schematic showing the connection of the JFET to the SR570 and finally to the Digital Spectrum Analyzer (DSA). The source and gate terminals of the JFET were shorted to the ground terminal of the Keithley 4200.                                                                                                                                                                      |

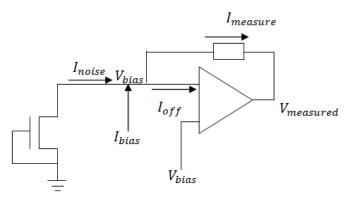

| Figure 3.21. Schematic that shows the various currents from the JFET to the SR570. The bias current cancels the current offset                                                                                                                                                                                                                                                                      |

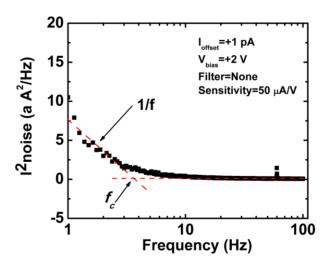

| Figure 3.22. The JFET noise spectrum with the background noise subtracted from the measured noise.                                                                                                                                                                                                                                                                                                  |

| Figure 3.23. The total output current noise of the JFET when it is operating in the saturation region                                                                                                                                                                                                                                                                                               |

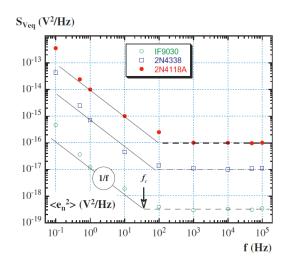

| Figure 3.24. Equivalent input noise voltage of JFETs 2N4338, 2N4118A and IF9030.                                                                                                                                                                                                                                                                                                                    |

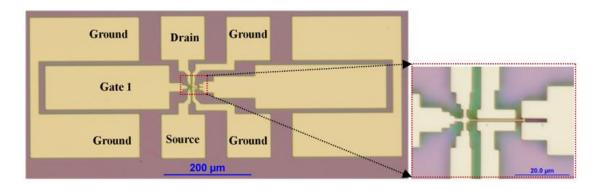

| Figure 3.25. Optical image of the device showing the GSG probing pads                                                                                                                                                                                                                                                                                                                               |

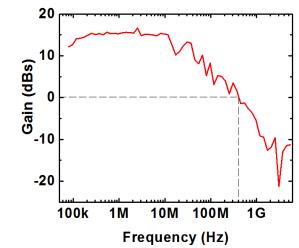

| Figure 3.26. Plot of current gain $(f_T)$ vs. frequency of the JFET62                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

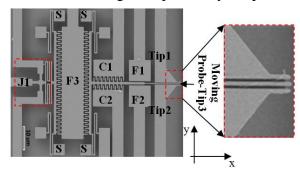

| Figure 4.1. Top view of the device with the probe, JFET (J1), meander and stoppers (S). The stoppers restrict motion of the probe and JFET                                                                                                                                                                                                                                      |

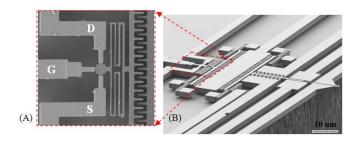

| Figure 4.2. (A) SEM micrograph of the suspended JFET with meander (B) Side view SEM micrograph of device                                                                                                                                                                                                                                                                        |

| Figure 4.3. (A) SEM micrograph of the suspended JFET with MoSi <sub>2</sub> source, drain and gate metallization. (B) SEM cross-sectional view of the region between the source and drain of the JFET. Focused Ion-Beam (FIB) was used to cut the beam to obtain the cross sectional view                                                                                       |

| Figure 4.4. Schematic of the actuation and sensing of displacement by the JFET 69                                                                                                                                                                                                                                                                                               |

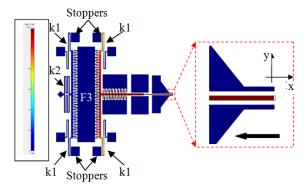

| Figure 4.5. COMSOL® simulation of displacement of probe tip and JFET meander spring (k2). The probe tip can move in both the x and y directions71                                                                                                                                                                                                                               |

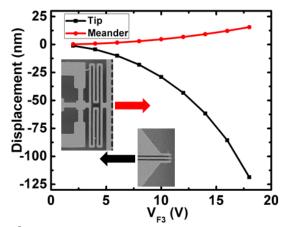

| Figure 4.6. COMSOL® simulation results for the model in Figure 4.5. Actuation voltage of 18 V at F3 generates a displacement of 120 nm at the probe tip and 15.5 nm at the transistor meander. The meander and probe move in opposite directions72                                                                                                                              |

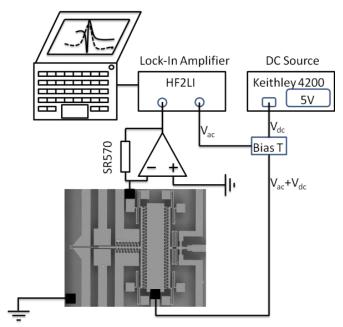

| Figure 4.7. Electrical setup for resonance frequency measurement of the middle tip. 73                                                                                                                                                                                                                                                                                          |

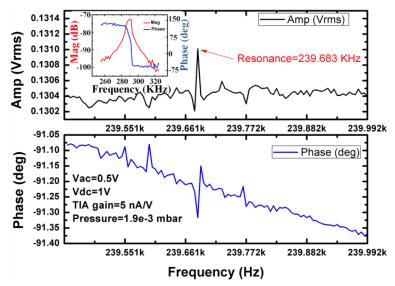

| Figure 4.8. Resonance frequency measurement of the moving tip in vacuum at a pressure of 1.9x10 <sup>-3</sup> mbar                                                                                                                                                                                                                                                              |

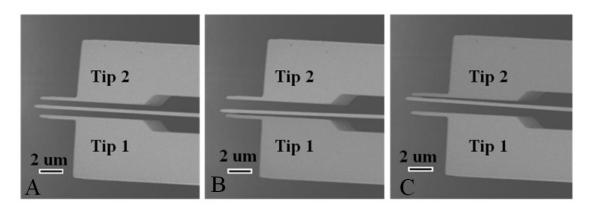

| Figure 4.9. (A) All tips are grounded. (B) +3.5 V applied to tip 1. (C) +3.5 V applied to tip 2                                                                                                                                                                                                                                                                                 |

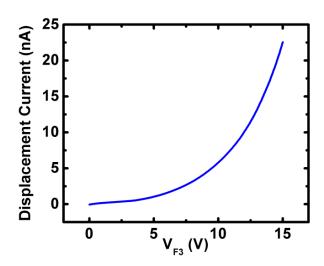

| Figure 4.10. Sweeping the voltage applied at F3 in ramps, the displacement current due to motion is measured between the moving probe and F3                                                                                                                                                                                                                                    |

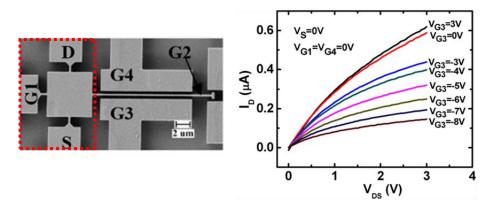

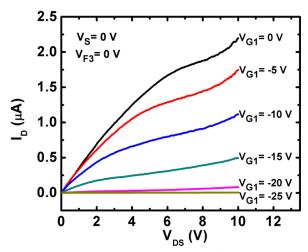

| Figure 4.11. Measured $I_{DS}$ vs. $V_{DS}$ output curves for the JFET. $V_{G2}$ was floating, while $V_{G1}$ was varied                                                                                                                                                                                                                                                        |

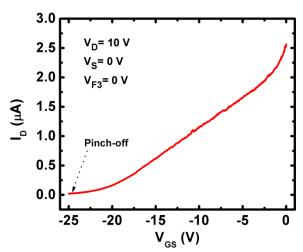

| Figure 4.12. Transfer curve for the JFET biased at $V_{DS}$ =10 V. The $I_{on}/I_{off}$ ratio was 126                                                                                                                                                                                                                                                                           |

| Figure 4.13. (A) The biasing schematic for sensing the motion of the probe. (B) Both the probe and transistor moved as an actuation voltage was applied and the JFET was able to sense the motion of the probe. The induced floating potential and strain on the JFET modulated the drain current. For these experiments $V_{\rm G1}$ and source terminals were set at 0 volts. |

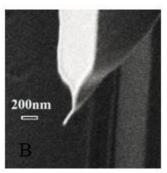

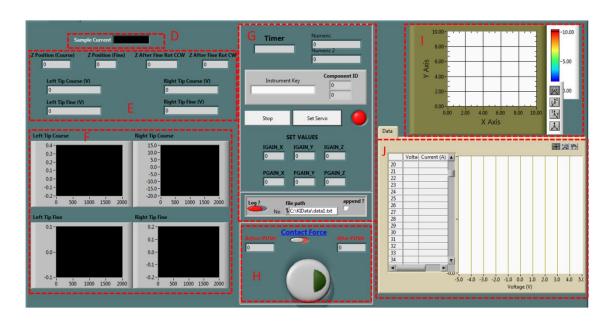

| Figure 4.14. (A) Top view of the sharpened tip to sub 50 nm radius. (B) Side-view of the sharpened tip                                                                                                                                                                                                                                                                          |

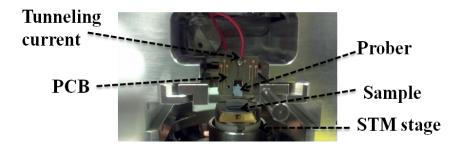

| Figure 4.15. Assembled NEMS-prober on PCB board that is finally mounted in JEOL SPM system. The HOPG sample sits below the NEMS-prober                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

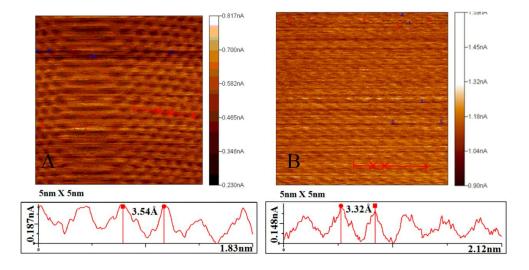

| Figure 4.16. (A) Using a commercial Pt-Ir tip to scan HOPG sample. (B) The NEMS-prober is used to scan HOPG                                                                                                    |

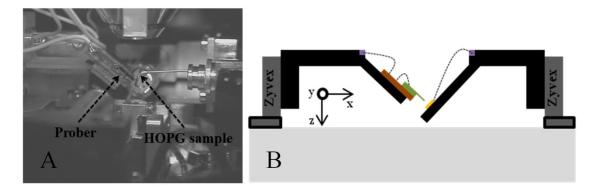

| Figure 4.17. (A) The prober and HOPG sample were mounted in SEM for in-situ conductance analysis of HOPG. (B) Schematic of the testing assembly in the SEM using the Zyvex <sup>®</sup> nanopositioners        |

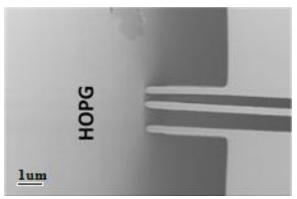

| Figure 4.18. SEM micrograph of the tips in soft contact with HOPG sample84                                                                                                                                     |

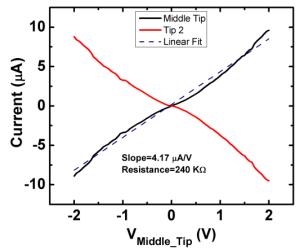

| Figure 4.19. The conductance characteristics of HOPG sample. The dashed line is a linear fit to the middle tip current and the resistance of the HOPG sheet is determined from the inverse slope of this line. |

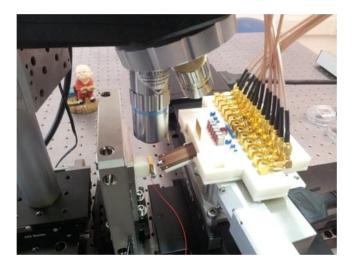

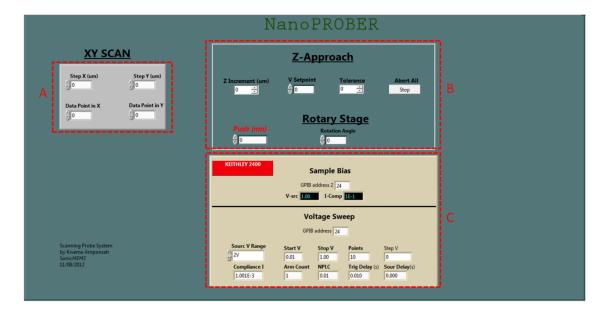

| Figure 5.1. Hardware of the SPS.                                                                                                                                                                               |

| Figure 5.2. Input panel of the GUI.                                                                                                                                                                            |

| Figure 5.3. Output panel of the GUI                                                                                                                                                                            |

| Figure 5.4. Spring compliant double-tip for resistance mapping HOPG film92                                                                                                                                     |

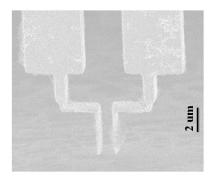

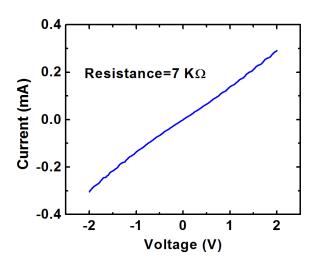

| Figure 5.5. Current-voltage characteristic of a continuous region of HOPG93                                                                                                                                    |

| Figure 5.6. A 5 $\mu$ m by 5 $\mu$ m resistance map of HOPG film. The measured resistance values range from 7 k $\Omega$ for continuous regions and 170 M $\Omega$ for non-continuous regions                  |

# LIST OF TABLES

| Table 1.1. Previous transistor integration efforts                               | 2    |

|----------------------------------------------------------------------------------|------|

| Table 2.1. Parameters used to calculate the switching energy of the NEMS switch  | . 22 |

| Table 3.1. NEMS switch parameters                                                | . 42 |

| Table 3.2. Capacitance values of the JFET-NEMS device.                           | . 50 |

| Table 3.3. JFET/NEMS device parameters                                           | . 53 |

| Table 3.4. Noise performance of JFETs at 1 Hz                                    | . 60 |

| Table 4.1. Parameters used to calculate the resonance frequency of the probe tip | .75  |

| Table 4.2. Device parameters of prober                                           | .77  |

| Table 5.1. State machine for the alignment of the side tips                      | . 89 |

## Chapter 1

#### INTRODUCTION

# 1.1 Integration of Transistors into Nano-Electro-Mechanical-Systems

Most commercial MEMS sensor solutions use the two-chip solution for electrical interface and signal conditioning. The two-chip solution is often justified as a way to reduce complexity of CMOS integration with SOI-NEMS. Although the hybrid technique offers the advantage of independent optimization of the integrated circuit and NEMS fabrication process flows, the cost for assembly and packaging can be higher than the monolithic integration [1]. Especially as the critical gate length of CMOS gets smaller and CMOS only gets less expensive, the two chip solution is more commercially viable. However, for higher performance, monolithic approaches may prove to be better than the two chip solution. The two-chip solution introduces parasitics and mismatches during the assembly and packaging of the ASIC and NEMS components due to the wire bonds that connects the two dies and prevents the SOI-NEMS/MEMS from fully realizing its highest performance.

To sense small signals such as the motion of a NEMS/MEMS device, JFETs are preferred over other transistors such as MOSFETs and BJTs because of their low 1/f noise, low-mask count, no parasitic diodes in isolation junctions, and insensitivity to electrostatic discharge [2], [3]. Furthermore, the yield issues with CMOS-oxide-silicon interfaces are eliminated in JEFTs. However, JFETs have the disadvantage of lower transconductance, higher process variations and higher gate leakage current.

Previously, various research groups have monolithically integrated MOSFETs into NEMS/MEMS devices for signal transduction [4]-[7] but this dissertation is focused on monolithic integration of JFETS and NEMS for motion sensing.

**Table 1.1. Previous transistor integration efforts**

|                            | Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Resonant<br>Frequency | Quality<br>Factor | MEMS<br>Material                         |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------|------------------------------------------|

| H. Luo et.al [4]           | spring series right frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6.1 KHz               |                   | Composite of metal and dielectric layers |

| D. Grogg et al. [5]        | 20 µm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32 MHz                | 4000              | Silicon                                  |

| H. C. Nathanson et al. [6] | The state of the s | 1KHz to 100 KHz       | 500               | Gold                                     |

| D. Weinstein et al. [7]    | Resonant Body Transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11.72 GHz             | 1830              | Silicon                                  |

# 1.2 Passive Sensing (two-chip Solution: Sensing of micro transducers)

Passive sensing, also known as the two-chip solution is when the NEMS and front end electronics are not fabricated on the same wafer die. Wire-bonds are used to connect the two dice as shown in Figure 1.1. Some of the advantages of this form of integration are the independent scaling of the NEMS and CMOS electronics with lithography scaling, its potentially lower cost, and its design simplicity. However, the wire-bonds that are introduced during packaging cause parasitic feedthrough, lower signal-to-noise ratio and higher packaging cost.

Figure 1.1. Two-chip solution resulting in the integration of NEMS and ASIC.

The wire bond introduces capacitive parasitic as well as mismatch at the input port of the amplifier.

Figure 1.2. Schematic of the two-chip solution where the NEMS component is wire-bonded to an off-chip transimpedance amplifier.

Capacitive coupling and low signal-to-noise ratio leads to passive NEMS devices generally having lower performance. Figure 1.2 shows the small signal electrical equivalent circuit of the NEMS structure that is wire-bonded to an off-chip transimpedance amplifier. The resonator can be modeled as a typical Butterworth–Van Dyke equivalent circuit as shown in Figure 1.2 where  $L_x$ ,  $C_x$ , and  $R_x$  represent the

motional inductance, capacitance and resistance respectively.  $C_0$  is the parasitic DC capacitance of the resonator and  $C_p$  represents the total parasitic capacitance introduced from the wirebonds, circuit board and packaging. If  $C_p$  is large, it will generate large amounts of current that will obscure the motional current from the NEMS component [8]. There is also a parasitic capacitor  $(C_w)$  from the bonding wire (at the negative input of the operational amplifier) to ground. This capacitor in most cases is assumed to have negligible effect on the transduction process because it is connected from a virtual ground to the earth ground. In reality, the operational amplifier is non-ideal and there is a Common Mode Rejection Ratio (CMRR). Small voltages differences between the (+) and (-) terminals is amplified. Hence and noise coming through the wirebond (i.e., 60 Hz noise) will leak into the signal chain.

Since the gate of the TIA is held at a virtual ground, the effect of the gate capacitance is ideally nullified. The admittance of the NEMS component with the parasitic capacitance  $(C_p)$  is given by:

$$Y = SC_p + SC_0 + \frac{SC_X}{S^2 L_X C_X + SR_X C_X + 1}$$

(1.1)

The impedance including the effect of C<sub>w</sub> is:

$$Z = \frac{1}{SC_w} + \frac{1}{S(C_P + C_0 + C_X)} \left[ \frac{S^2 L_X C_X + SR_X C_X + 1}{S^2 L_X C_Z + SR_X C_Z + 1} \right]$$

(1.2)

$$C_Z = \frac{C_X(C_P + C_0)}{C_P + C_0 + C_X} \tag{1.3}$$

As  $C_w$  becomes large, it will change the phase of the impedance and resonance frequency detection becomes difficult. Using typical resonator parameters [9],  $C_x$ = 1.9 aF,  $L_x$ = 1.3 H,  $R_x$ = 82 K $\Omega$ , and  $C_0$ = 1.2 fF,  $C_w$  was swept to investigate its effect on the phase angle of the resonator. From Figure 1.3, the phase of the impedance changes from -88 degrees to +63 degrees at which point the resonance is non-detectable [10].

Figure 1.3. Plot of phase vs. frequency illustrating the effect of the parasitic capacitance on the resonance frequency of the NEMS resonator. The parasitic capacitance tends to shift the resonance frequency as well as decreases the phase shift at resonance of the resonator.

The output current which is a combination of the motional current and the parasitic current through  $C_p$ , is given by Equation (1.4) while the transfer function is given by Equation (1.5):

$$i_d = \frac{v_{in}}{Z} = -\frac{v_{out}}{R_f} \tag{1.4}$$

$$\frac{v_{out}}{v_{in}} = -R_f [S(C_P + C_0 + C_X)] \frac{S^2 L_X C_Z + S R_X C_Z + 1}{S^2 L_X C_X + S R_X C_X + 1}$$

(1.5)

# 1.3 Active Sensing: Transistor Level Motion Transduction

To improve the signal integrity during the transduction process, it is recommended that the front-end transistor or electronics be monolithically integrated with the NEMS component as shown in Figure 1.4. In this way, the front-end transistor will serve as a current buffer offering current amplification as well as improving noise immunity at the output node. Capacitive transduction is mostly favored due to its temperature stability, lack of 1/f noise, and ease in fabrication and its repeatability as compared to resistive transduction [9]. Piezoelectric, piezoresistive, thermal and magnetostrictive are other modes of transduction that are less commonly used.

Figure 1.4. Monolithic integration of MEMS accelerometer structure with FETs results in the elimination of the wire-bond parasitic, replaced by the much smaller interconnect parasitic capacitance.

There are many advantages to using a single front-end transistor to transduce the motional current of the M/NEMS component as compared to using an operational amplifier [8]. It is not only lithographically simple to do this form of integration, but it is also less insensitive to process variation.  $C_t$  represents all the capacitances connecting the resonator to the gate of the JFET and it includes the gate-to-source capacitance, gate-to-drain capacitance and any substrate capacitances [8].  $g_m$  is the transconductance of the JFET.

Figure 1.5. Small signal electrical equivalent of the JFET integrated with the NEMS resonator.

The movement of the NEMS component produces a motional current that is converted into gate voltage ( $V_{gs}$ ) by the capacitor  $C_t$ . The JFET then converts this gate voltage into output current ( $i_d$ ) and in the process provides current amplification. Figure 1.5 can be simplified into a voltage divider circuit as shown in Figure 1.6.  $Z_1$  and  $Z_2$  represent the total NEMS impedance and input impedance at the gate of the JFET respectively.

$$V_{in}$$

$\overline{Z_1}$   $\overline{Y_{gs}}$   $\overline{Z_2}$   $\underline{\bot}$

# Figure 1.6. The JFET gate voltage results from the voltage divider between the JFET and NEMS impedances.

The impedance of the NEMS component is given by:

$$Z_1 = \frac{1}{S(C_0 + C_X)} \left[ \frac{S^2 L_X C_X + S R_X C_X + 1}{S^2 L_X C_{P1} + S R_X C_{P1} + 1} \right]$$

(1.6)

$$C_{P1} = \frac{C_0 C_X}{C_0 + C_X} \tag{1.7}$$

The impedance at the gate of the JFET is given by:

$$Z_2 = \frac{1}{SC_T} \tag{1.8}$$

Using a voltage divider at the gate:

$$Z_T = \frac{Z_2}{Z_1 + Z_2} \tag{1.9}$$

$$Z_T = \frac{S^2 L_X C_{P1} + S R_X C_{P1} + 1}{\frac{C_0 + C_X + C_T}{C_0 + C_X} \left( S^2 L_X C_{p2} + S R_X C_{p2} + 1 \right)}$$

(1.10)

$$C_{P2} = \frac{C_X(C_0 + C_T)}{C_0 + C_X + C_T} \tag{1.11}$$

$$I_d = g_m \left( \frac{(C_0 + C_X)(S^2 L_X C_{P1} + SR_X C_{P1} + 1)}{(C_0 + C_X + C_T)(S^2 L_X C_{P2} + SR_X C_{P2} + 1)} \right) V_{in}$$

(1.12)

The amplified current  $(I_d)$  could then be put into a transimpedance amplifier that converts the motional current into appreciable voltage.

# 1.4 Scope of Dissertation

This dissertation presents a novel monolithic integration of JFET into MEMS and NEMS based systems. The JFET is used to sense the motion of the NEMS component. The simulation, fabrication and electrical characterization of both the JFET and the NEMS structures will be explored. Details will also be given on a new multiple-tip Scanning Probe Microscope that was developed to use the JFET-NEMS devices for atomic imaging and charge transport measurement experiments. The dissertation is organized as follows:

Chapter 2 will provide research effort into the design and characterization of NEMS switches for digital computation using SOI structures. The two main types of NEMS switches are the series and shunt capacitive switches [11]. This dissertation will focus on DC ohmic switches for ultra-low switching voltage applications. For ohmic switches, a figure of merit (FOM) is the contact resistance and lifetime. To improve the FOM, a new generation of all-metal switches were developed using Molybdenum Disilicide (MoSi<sub>2</sub>) as the structural material and coating the switches with a layer of Cr and Pt.

Chapter 3 will delve into the monolithic integration of JFET into the SOI NEMS switches. As voltage ramps were applied to close the switch, the JFET was used to sense the motion of the cantilever. The device was fabricated onto an SOI platform and to reduce the JFET source and drain resistances, MoSi<sub>2</sub> was used as the contact metal and Rapid Thermal Annealed (RTA) to enhance good ohmic contact.

Chapter 4 will demonstrate an application of the JFET-NEMS integration technology where the JFET was further integrated into a multiple-tip NEMS device for scanning probing measurements. The nanoprober has two fixed side tips and the middle tip is capable of being displaced in both the x and y directions using electrostatic comb actuators. The JFET was used to sense the motion of the movable tip. The nanoprober was used to image atomic arrangement of carbon atomic lattices in Highly Ordered Pyrolytic Graphite (HOPG) as well as perform in-situ SEM conductance measurement of the HOPG film. For applications where the JFET was not required, MoSi<sub>2</sub> tips were fabricated and used for mapping the conductance of the surfaces at nanoscale.

Chapter 5 will detail the development and assembly of a *Sonic*MEMS Scanning Probe Microscope. This instrument accepts the multiple tips and was used to perform resistance map measurements of HOPG film.

# Chapter 2

# NON-PULL-IN PRE-BIASED NANO-ELECTRO-MECHANICAL SWITCH WITH PRE-BIASING

#### 2.1 Introduction

Nanomechanical switches in series with transistor technologies (BJTs, CMOS, or MESFETs) can facilitate ultra-low-power circuits by eliminating leakage current in transistor circuits [12]. Furthermore, NEMS switches could facilitate all-mechanical digital logic that might consume even less power than hybrid solutions, and the switches are naturally radiation hard.

Nano and micro electromechanical switches are making entry into areas such as mechanical computation, telecommunication, automotive and biomedical fields [13], [14]. NEMS switches, with gas or vacuum in the gaps between the source and drain offer the ideal zero standby leakage power, important for ultra-low power circuits [15], [16]. This is particularly important as deeply scaled transistors have high leakage currents. However, NEMS switches suffer from stiction, arcing, and high switching and pull-in voltages [17].

Generally, MEMS switches have a finite lifetime not capable of trillions of cycles needed for computation. For example, a CMOS switch operating at 1 GHz for 1 year should go through a total number of  $\sim 3 \times 10^{16}$  cycles. The best switching cycle lifetime for MEMS switches is around  $10^{10}$  cycles. One exception is the mirrors in Digital Light Processing (DLP) displays by Texas Instruments that can operate for tens of years at kHz switching rates.

It is important to design NEMS switches to increase contact lifetime. Previous work by Yang et al., demonstrated the maneuvering of pull-in voltage in a

microswitch by pre-charging the gate electrode and modulating the pull-in voltage by charging a floating gate potential through the body bias. With their technique, they were able to greatly reduce the pull in voltage from 48 V to 3 V [18].

Figure 2.1. Schematic of the switch architecture demonstrated by Yang et al. The gate electrode was pre-charged and the voltage that is applied to the substrate increases the charge on the pre-charge electrode [18].