# **Reconfigurable Architectures for Chip Multiprocessors**

by Matthew Ace Watkins

This thesis/dissertation document has been electronically approved by the following individuals:

Albonesi,David H. (Chairperson) Manohar,Rajit (Minor Member) Martinez,Jose F. (Minor Member)

# RECONFIGURABLE ARCHITECTURES FOR CHIP MULTIPROCESSORS

A Dissertation

Presented to the Faculty of the Graduate School

of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by Matthew Ace Watkins August 2010 © 2010 Matthew Ace Watkins ALL RIGHTS RESERVED

# RECONFIGURABLE ARCHITECTURES FOR CHIP MULTIPROCESSORS Matthew Ace Watkins, Ph.D.

Cornell University 2010

Prior research in chip-level reconfigurable computing has involved augmenting a single processor core with reconfigurable logic. Despite significant performance gains for some applications, the area and power costs can easily outweigh the benefits, especially when considering the breadth of applications run on a general purpose processor and the benefit they receive from reconfigurable logic, from orders of magnitude benefit to no benefit at all. Moreover, this prior work focused almost exclusively on uniprocessor systems and did not address the unique requirements of parallel applications.

This dissertation proposes novel reconfigurable architectures for chip multiprocessors (CMPs). In our approach, the reconfigurable fabric is shared among multiple threads from both sequential and parallel applications to amortize the area and power costs and increase fabric utilization. To further reduce the overhead, we propose a heterogeneous CMP where different regions are optimized for different tasks, including regions with shared reconfigurable fabrics, and other regions with only conventional cores. Within a reconfigurable region, the architecture dynamically manages the use of the shared fabric and includes mechanisms that accelerate parallel applications and enable parallelization of otherwise sequential applications.

We first identify a number of features from previous proposals that enable efficient sharing of reconfigurable logic. With these features in mind we design Specialized Programmable Logic (SPL), a reconfigurable fabric specially tailored for sharing among multiple cores, and evaluate and optimize the SPL under a range of both single- and multi-threaded applications.

As with other shared structures, shared SPL must be intelligently controlled in order to achieve optimal performance. We propose a number of sharing schemes and find that, with proper management, shared SPL achieves performance similar to providing each core with its own large, private fabric, while substantially reducing area and peak power costs.

When multiple single- and multi-threaded applications are running on multiple SPL clusters, the assignment of threads to clusters and the dynamic partitioning of the fabric significantly impact performance. To address these issues, we propose a number of management algorithms that control both thread scheduling and SPL sharing.

Finally, the shared nature of the SPL makes it well suited for communicating among the attached cores. We propose modifications to the baseline SPL design that allow it to provide a means of fine-grained interthread and barrier communication among cores sharing the fabric. Performing communication through the SPL provides the additional benefit of allowing computation to be performed on the data while it is in-flight to the recipient. When incorporated into a heterogeneous CMP, the combined computation and communication abilities of the SPL provide significant benefits over a CMP with only traditional cores.

#### **BIOGRAPHICAL SKETCH**

Matthew Watkins was born in Youngstown, Ohio and spent most of his childhood growing up in Saratoga Springs, New York. He graduated as Valedictorian from Saratoga Springs High School in 2001. He attended the University at Buffalo as a Distinguished Honors Scholar and graduated in 2005 with dual degrees in Computer Engineering and Electrical Engineering. He was active in the university's jazz ensemble and served as president of the Tau Beta Pi and Golden Key chapters on campus.

Matt has been interested in computers from an early age. As a child he enjoyed playing on his family's Commodore and early IBM computers. This interest in computers, coupled with his strength in math and science, led him to pursue a degree in computer engineering. Of all of the courses he took as an undergraduate, his favorites were digital logic, computer organization, and computer architecture. Although Buffalo had no active research in computer architecture, Matt decided to pursue this area for his graduate studies.

Out of a number of prestigious universities that accepted him, Matt chose to attend Cornell for his graduate work due to the professors' sincere interest in working with him and their active efforts to recruit him. During his first year and a half he worked on leveraging on-chip optical interconnects to enhance power and performance of large scale CMPs. For his thesis he concentrated on reconfigurable computing. In particular, focusing on how the move to chip multiprocessors allows more efficient integration of reconfigurable logic into a general purpose processor.

In his limited free time Matt enjoys playing the trumpet and piano and swing and ballroom dancing. Matt has been involved with music for most of his life, but prior to arriving at Cornell, had almost no dance experience. Despite this,

iii

when the dance bug bit him, it bit him hard. He joined the ballroom team at the beginning of his second semester, unsure if he wanted the time commitment it involved. By the end of the semester, the nearly daily ballroom practices were the highlight of his day (and still are to this day). He found he had an affinity for the standard/smooth style of dances and by the time of his graduation he was dancing those styles at one of the highest levels in collegiate ballroom dancing.

After graduating, Matt hopes to find a position in academia. He is especially interested in the teaching side of university life where he looks forward to passing on his knowledge and interest in computers to future students. He also looks forward to mentoring students both in their research and as they decide on their future career path. To my parents,

for their never-ending love and support.

#### ACKNOWLEDGEMENTS

First and foremost, my thanks to my advisor, Prof. David Albonesi, for his guidance and direction throughout the last five years. Working for a Ph.D. is a challenging experience under any circumstances. Your advisor, however, can make the difference between a difficult, but rewarding experience, and some of the most unpleasant years of your life. I could not have asked for a better advisor than Prof. Albonesi. In addition to caring about my professional success, he was also concerned with my life outside of work, understanding, and even encouraging, my pursuit of activities outside of office life.

I would also like to thank the other members of my committee, Rajit Manohar and José Martínez, for their input on my thesis and their help in general over the years. Thanks also to the other faculty of Cornell CSL, past and present, especially Sally McKee for helping me turn a class project into a real paper, getting that paper published, and supporting me in my first (and third) overseas conference.

To the students of CSL, thank you for your advice and feedback and for keeping CSL a nice place to work. Special thanks to Mark, Paula, Basit, and Jonathan, my office mates throughout my tenure at Cornell, for keeping the office fun but productive.

Special thanks is also due to the people I interacted with outside of the office. These people where key to keeping me sane for the last five years and making sure I did something other than work all of the time. Of particular note are all of my friends from ballroom, especially my partners Julie, Ingrid, Margaret, Xiumin, and Jenn. It's amazing how far we progressed in the last four and half years. To my family, near and far, thank you for your support over the years and for your interest in my work and my progress (even if you didn't understand half of what I was doing). It was always nice to be able to talk to someone who could actually talk back (sadly, computers haven't mastered that ability yet). Special thanks to my grandparents, Greem and Pop-Pop, for their constant interest in what I was doing and how life was progressing, for celebrating my successes, supporting me through the difficult times, and in general for being my number one fans throughout my education.

Lastly, my unending thanks to my parents, Michael and Sarah, for providing constant support and encouragement throughout my years of schooling, for creating an environment at home that encouraged learning and achievement (and sometimes overachievment), for listening and encouraging when times where tough, for keeping me connected to the real world and making sure I stayed informed of family happening, and for just being the best parents anyone could ever hope for.

|   | Ded<br>Ack<br>Tabl<br>List | ication<br>nowled<br>e of Co<br>of Table | al Sketch     lgements     ntents <t< th=""><th>iii<br/>v<br/>vi<br/>viii<br/>x<br/>xi</th></t<> | iii<br>v<br>vi<br>viii<br>x<br>xi |

|---|----------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------|

| 1 | Intro                      | oductio                                  | on                                                                                               | 1                                 |

| 2 | Rela                       | ted Wo                                   | ork                                                                                              | 6                                 |

|   | 2.1                        | Recon                                    | figurable Computing                                                                              | 6                                 |

|   |                            | 2.1.1                                    | Fabric Design and Core Integration                                                               | 6                                 |

|   |                            | 2.1.2                                    | Fabric Characteristics for Sharing                                                               | 8                                 |

|   | 2.2                        | Thread                                   | d Scheduling                                                                                     | 9                                 |

|   | 2.3                        | Dynar                                    | mic Resource Sharing                                                                             | 10                                |

|   | 2.4                        | Fine-C                                   | Grained Interthread Communication                                                                | 11                                |

|   | 2.5                        | Fine-C                                   | Grained Synchronization                                                                          | 12                                |

| • | <b>C1</b>                  | 1 D                                      |                                                                                                  | 10                                |

| 3 | <b>Sna</b><br>3.1          |                                          | configurable Architectures for CMPs                                                              | <b>13</b><br>14                   |

|   | 5.1                        |                                          |                                                                                                  | 14                                |

|   |                            | 3.1.1<br>3.1.2                           | Motivating Example                                                                               | 14                                |

|   |                            | 3.1.2                                    | System Overview                                                                                  | 17                                |

|   |                            | 3.1.3<br>3.1.4                           | Core/Fabric Integration                                                                          | 17                                |

|   |                            | 3.1.4                                    |                                                                                                  | 10<br>24                          |

|   |                            | 3.1.5<br>3.1.6                           |                                                                                                  |                                   |

|   |                            |                                          | Software Interface                                                                               | 26                                |

|   | 2.2                        | 3.1.7                                    | Sharing Policies                                                                                 | 28                                |

|   | 3.2                        |                                          | ation Methodology                                                                                | 32                                |

|   |                            | 3.2.1                                    | Benchmarks                                                                                       | 33                                |

|   | 0.0                        | 3.2.2                                    | SPL Programming and Function Mapping                                                             | 34                                |

|   | 3.3                        |                                          |                                                                                                  | 36                                |

|   |                            | 3.3.1                                    | Characterization of CMPs with Private SPL                                                        | 36                                |

|   | ~ 1                        | 3.3.2                                    | Evaluation of Shared SPL                                                                         | 39                                |

|   | 3.4                        | Concl                                    | usion                                                                                            | 43                                |

| 4 | Mar                        | aging                                    | Multiprogrammed Workloads in Multiple SPL Clusters                                               | 44                                |

|   | 4.1                        |                                          | -Scale Cluster-Based CMPs                                                                        | 45                                |

|   |                            | 4.1.1                                    | SPL Hardware Microarchitecture                                                                   | 46                                |

|   |                            | 4.1.2                                    | Temporal Sharing and Spatial Partitioning                                                        | 47                                |

|   | 4.2                        |                                          | luster Management                                                                                | 48                                |

|   |                            | 4.2.1                                    | Per Interval Thread Assignment Policies                                                          | 50                                |

|   |                            | 4.2.2                                    | Composite Thread Assignment/Partitioning Policies                                                | 51                                |

# TABLE OF CONTENTS

|    |       | 4.2.3 Learning-Inspired SPL Cluster Management      | 52  |

|----|-------|-----------------------------------------------------|-----|

|    | 4.3   | Evaluation Methodology                              | 58  |

|    |       | 4.3.1 Phase Tracking                                | 59  |

|    |       | 4.3.2 Benchmarks                                    | 60  |

|    | 4.4   | Results                                             | 62  |

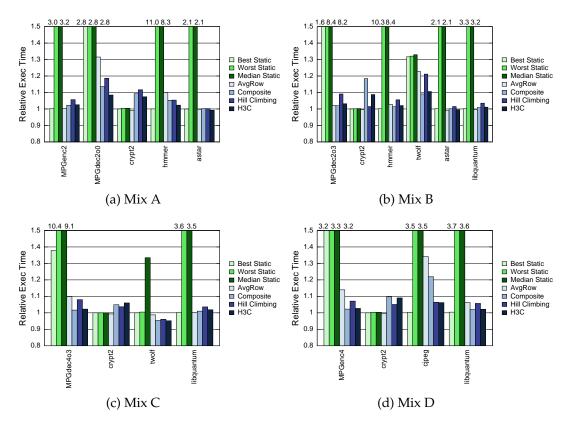

|    |       | 4.4.1 Static Assignment Performance                 | 63  |

|    | 4 -   | 4.4.2 Performance of Dynamic SPL Cluster Management | 65  |

|    | 4.5   | Conclusion                                          | 72  |

| 5  | Fine  | -Grained Communication in a Heterogeneous CMP       | 74  |

|    | 5.1   | RACM Architecture                                   | 76  |

|    |       | 5.1.1 SPL Organization                              | 77  |

|    |       | 5.1.2 RACM Communication                            | 78  |

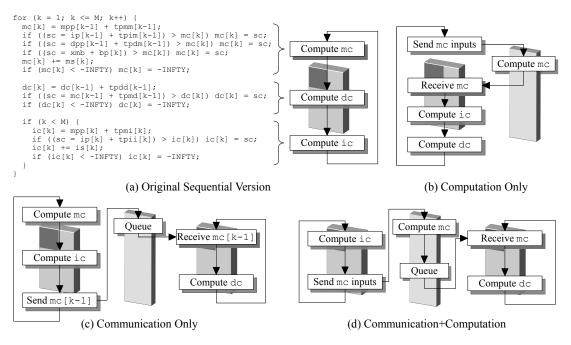

|    | 5.2   | Communication Examples                              | 86  |

|    |       | 5.2.1 Interthread Communication+Computation Example | 86  |

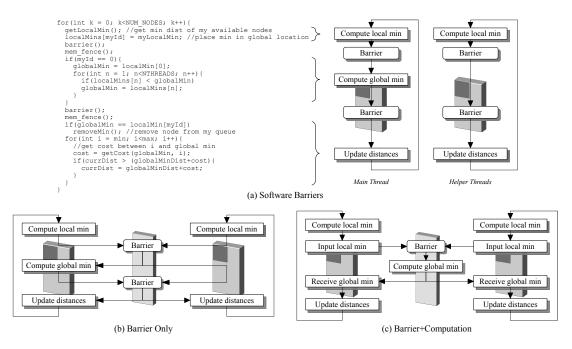

|    |       | 5.2.2 Barrier Synchronization+Computation Example   | 88  |

|    | 5.3   | Evaluation Methodology                              | 90  |

|    |       | 5.3.1 Benchmarks                                    | 91  |

|    |       | 5.3.2 RACM Programming                              | 93  |

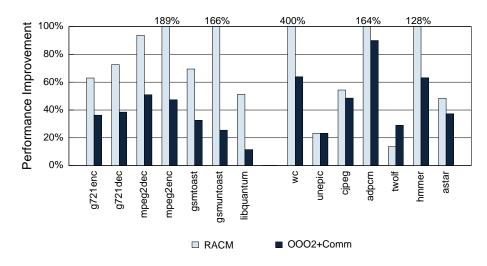

|    | 5.4   | Results                                             | 93  |

|    |       | 5.4.1 RACM in a Heterogeneous CMP                   | 93  |

|    |       | 5.4.2 Analysis of Optimized Regions                 | 96  |

|    |       | 5.4.3 Fine-Grained Barrier Synchronization          | 100 |

|    | 5.5   | Conclusion                                          | 105 |

| 6  | Con   | clusions and Future Work                            | 106 |

|    | 6.1   | Future Work                                         | 108 |

| Α  | Dyn   | amic Partitioning Manager                           | 110 |

|    | A.1   |                                                     | 110 |

|    |       | A.1.1 DPM Design                                    | 111 |

|    | A.2   | Results                                             | 114 |

|    |       | A.2.1 Multiapplication Workloads                    | 115 |

| Ri | bling | raphy                                               | 118 |

| וע | ~1108 | -nkì                                                | 110 |

## LIST OF TABLES

| 3.1 | Comparison of data from actual reconfigurable fabrics (scaled to                                                                                                                                                                                                                                              |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | 65nm) and the analytical model.                                                                                                                                                                                                                                                                               | 20 |

| 3.2 | Area and power of different core types and 26-row SPL normal-                                                                                                                                                                                                                                                 |    |

|     | ized to IO area and power.                                                                                                                                                                                                                                                                                    | 22 |

| 3.3 | SPL configurations and associated area and power costs                                                                                                                                                                                                                                                        | 23 |

| 3.4 | ISA extensions.                                                                                                                                                                                                                                                                                               | 26 |

| 3.5 | Architecture Parameters.                                                                                                                                                                                                                                                                                      | 32 |

| 3.6 | Benchmark, number of SPL functions, maximum rows used by<br>SPL functions, percentage of execution time of optimized regions,<br>percentage of SPL instructions executed relative to total commit-<br>ted instructions, and percentage of time with at least one SPL<br>instruction in flight for OOO1 cores. | 34 |

| 4.1 | Relative area and power of eight single-issue out-of-order cores, eight private SPLs, and two four-way shared SPLs.                                                                                                                                                                                           | 47 |

| 4.2 | Management policy considerations.                                                                                                                                                                                                                                                                             | 49 |

| 4.3 | Architecture parameters.                                                                                                                                                                                                                                                                                      | 58 |

| 4.4 | Parameters for dynamic management policies                                                                                                                                                                                                                                                                    | 59 |

| 4.5 | Benchmark description.                                                                                                                                                                                                                                                                                        | 61 |

| 4.6 | Workload composition.                                                                                                                                                                                                                                                                                         | 61 |

| 5.1 | Relative area and power of four single-issue out-of-order cores                                                                                                                                                                                                                                               |    |

|     | and four-way shared RACM fabric.                                                                                                                                                                                                                                                                              | 77 |

| 5.2 | Architecture parameters.                                                                                                                                                                                                                                                                                      | 91 |

| 5.3 | Benchmark details                                                                                                                                                                                                                                                                                             | 92 |

# LIST OF FIGURES

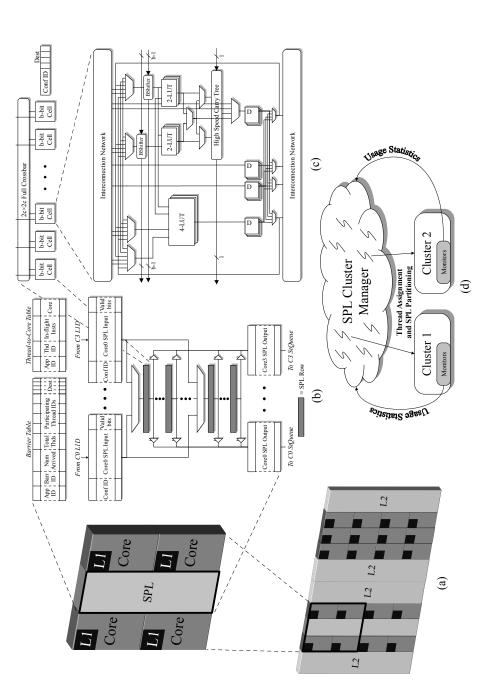

| 1.1  | Overview of a RACM CMP. (a) Depiction of overall chip, with<br>two SPL clusters and one conventional cluster, and blow-up of<br>one SPL cluster, (b) four-way shared SPL including tables re-<br>quired for communication, (c) design of SPL cell (unless other-<br>wise noted all data paths in the SPL are <i>b</i> bits wide, and (d) SPL<br>Cluster Manager. | 3  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

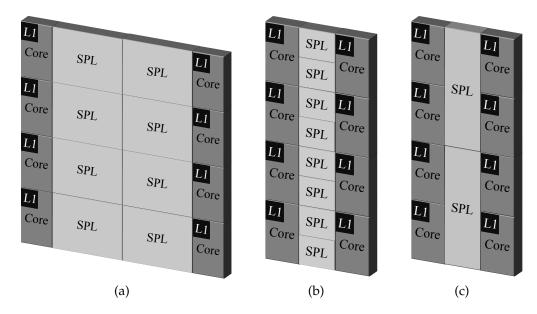

| 3.1  | Sample floor plans for a portion of a multicore chip with (a) 26-                                                                                                                                                                                                                                                                                                |    |

|      | row private, (b) 6-row private, and (c) 4-way shared SPL                                                                                                                                                                                                                                                                                                         | 15 |

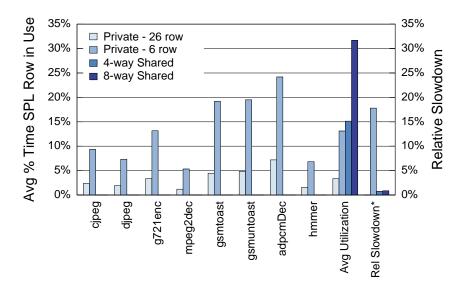

| 3.2  | SPL utilization for private and shared SPL organizations                                                                                                                                                                                                                                                                                                         | 15 |

| 3.3  | Comparison of latency and area predicted by analytical model to                                                                                                                                                                                                                                                                                                  |    |

|      | results reported in [95].                                                                                                                                                                                                                                                                                                                                        | 21 |

| 3.4  | Example of a six row configuration being executed on a three                                                                                                                                                                                                                                                                                                     |    |

|      | row SPL using virtualization [34]. Numbers inside each block                                                                                                                                                                                                                                                                                                     |    |

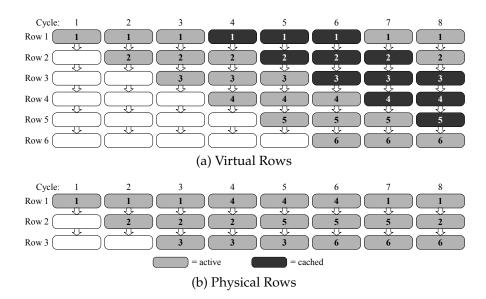

|      | indicate the configuration loaded in each row.                                                                                                                                                                                                                                                                                                                   | 25 |

| 3.5  | SPL assembly code for MPGenc dist1 function. The reference                                                                                                                                                                                                                                                                                                       |    |

|      | dist1 is a pointer to the SPL configuration information                                                                                                                                                                                                                                                                                                          | 27 |

| 3.6  | Example of spatial sharing.                                                                                                                                                                                                                                                                                                                                      | 30 |

| 3.7  | Example of temporal sharing                                                                                                                                                                                                                                                                                                                                      | 31 |

| 3.8  | Mapping SPEC2006 456.hmmer P7Viterbi to SPL                                                                                                                                                                                                                                                                                                                      | 35 |

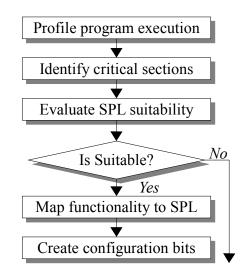

| 3.9  | Procedure of mapping functions to SPL.                                                                                                                                                                                                                                                                                                                           | 35 |

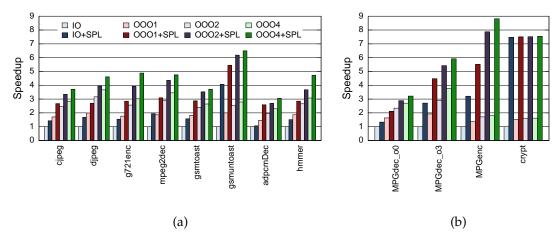

| 3.10 | Performance for (a) coarse-grain and (b) parallel workloads rel-<br>ative to IO cores without SPL.                                                                                                                                                                                                                                                               | 37 |

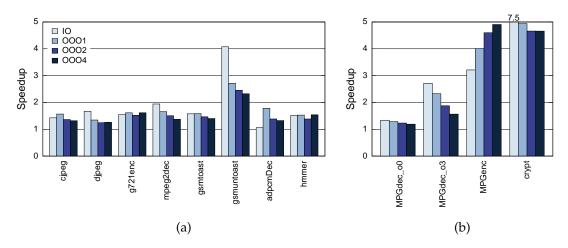

| 3.11 | Performance for (a) coarse-grain and (b) parallel workloads rel-<br>ative to the same core type without SPL.                                                                                                                                                                                                                                                     | 37 |

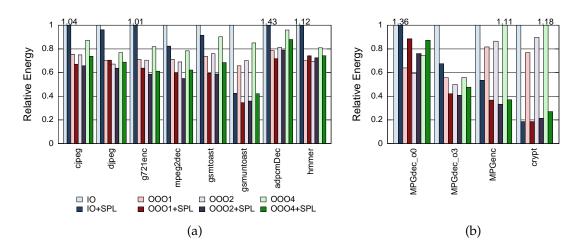

| 3.12 | Energy consumption for (a) coarse-grain and (b) parallel work-<br>loads relative to IO core without SPL.                                                                                                                                                                                                                                                         | 38 |

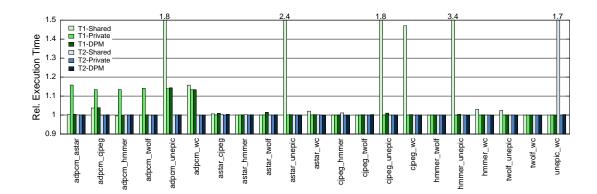

| 3.13 | Performance for (a) coarse-grain and (b) parallel workloads rel-                                                                                                                                                                                                                                                                                                 |    |

|      | ative to OOO1 + 26 row private SPL.                                                                                                                                                                                                                                                                                                                              | 41 |

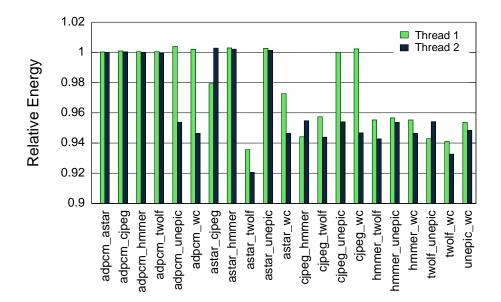

| 3.14 | Energy consumption for (a) coarse-grain and (b) parallel work-                                                                                                                                                                                                                                                                                                   |    |

|      | loads relative to OOO1 + 26 row private SPL.                                                                                                                                                                                                                                                                                                                     | 41 |

| 4.1  | Hash function for phase IDs.                                                                                                                                                                                                                                                                                                                                     | 54 |

| 4.2  | H3C Cluster Manager                                                                                                                                                                                                                                                                                                                                              | 57 |

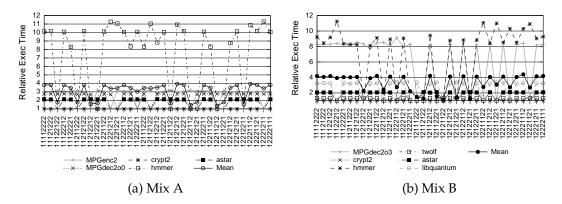

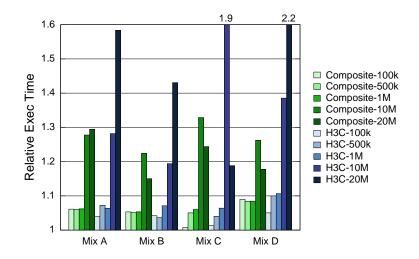

| 4.3  | Performance of (a) Mix A and (b) Mix B for shared SPL with all                                                                                                                                                                                                                                                                                                   |    |

|      | possible static schedules relative to private 12-row SPL.                                                                                                                                                                                                                                                                                                        | 63 |

| 4.4  | Performance of shared SPL with dynamic scheduling algorithms<br>and best, worst, and median static schedules relative to private                                                                                                                                                                                                                                 |    |

|      | 12-row SPL                                                                                                                                                                                                                                                                                                                                                       | 64 |

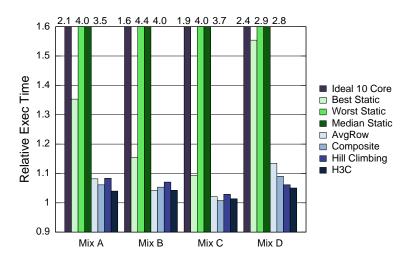

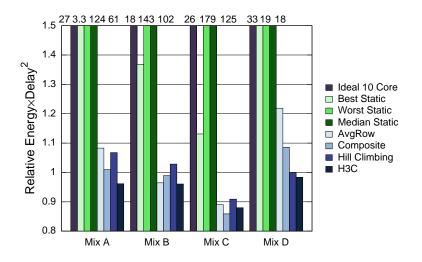

| 4.5  | Average execution time for each workload relative to 12-row pri-                                                                                                                                                                                                                                                                                                 |    |

|      | vate SPL                                                                                                                                                                                                                                                                                                                                                         | 65 |

| 4.6  | Average energy $	imes$ delay <sup>2</sup> for each workload relative to 12-row pri-                                                                                                                                                                                                                                                                              |    |

|      | vate SPL.                                                                                                                                                                                                                                                                                                                                                        | 67 |

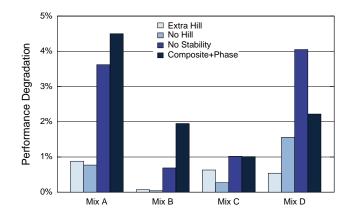

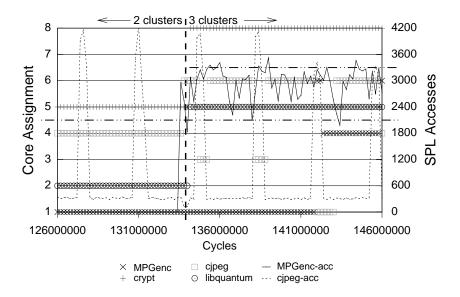

| 4.7<br>4.8 | Performance degradation relative to H3C                                                                                                                       | 68<br>69 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.9        | Average performance of Composite and H3C scheduling algo-<br>rithms with different scheduling intervals for all workloads rel-<br>ative to private 12-row SPL | 71       |

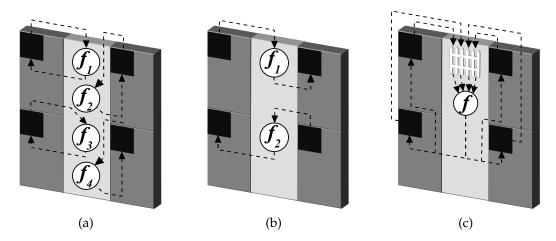

| 5.1        | Shared SPL being used for (a) individual computation, (b) produ-<br>cer-consumer communication with computation, and (c) barrier                              |          |

|            | synchronization with computation.                                                                                                                             | 75       |

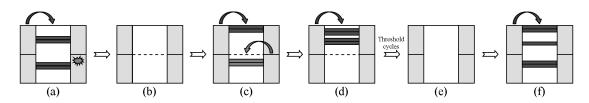

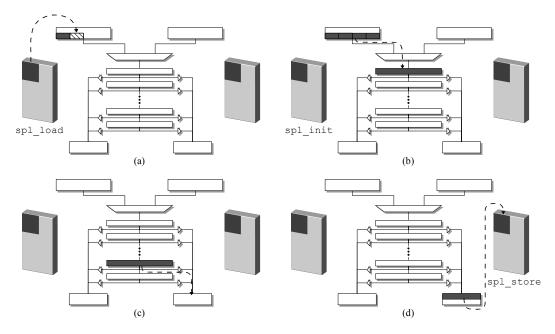

| 5.2        | Walk through of intercore communication.                                                                                                                      | 80       |

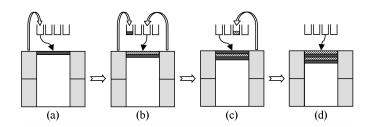

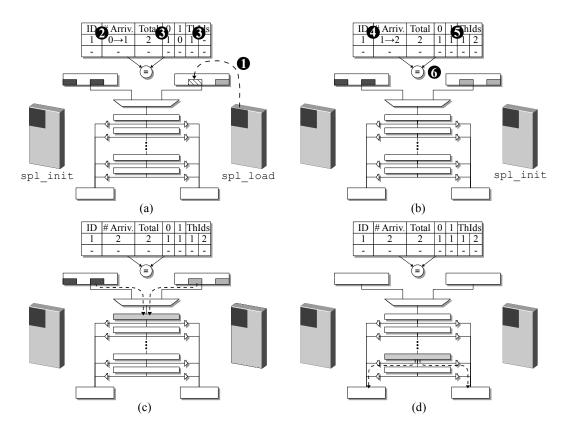

| 5.3        | Walk through of barrier synchronization.                                                                                                                      | 84       |

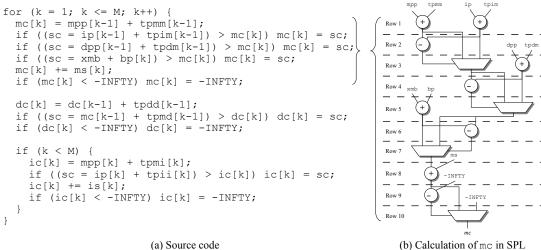

| 5.4        | Parallelization of SPEC 2006 456.hmmer P7Viterbi                                                                                                              | 87       |

| 5.5        | SPL mc calculation mapping                                                                                                                                    | 88       |

| 5.6        | Parallelization of Dijkstra's Shortest Path Algorithm                                                                                                         | 89       |

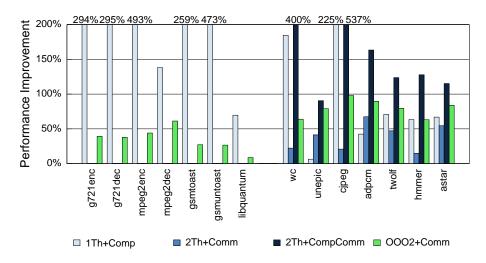

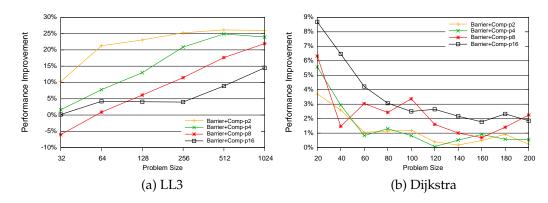

| 5.7        | Performance relative to single threaded baseline                                                                                                              | 94       |

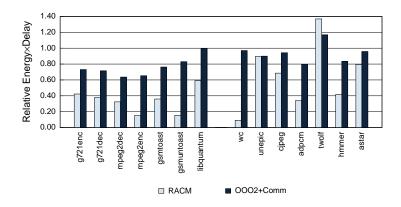

| 5.8        | Energy $\times$ delay relative to single threaded baseline                                                                                                    | 95       |

| 5.9        | Performance improvement of optimized functions relative to per-                                                                                               |          |

|            | formance of single threaded baseline                                                                                                                          | 96       |

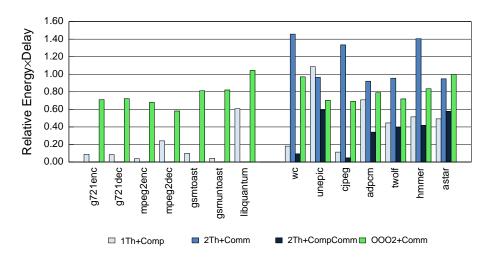

| 5.10       | Energy×delay relative to single threaded baseline                                                                                                             | 100      |

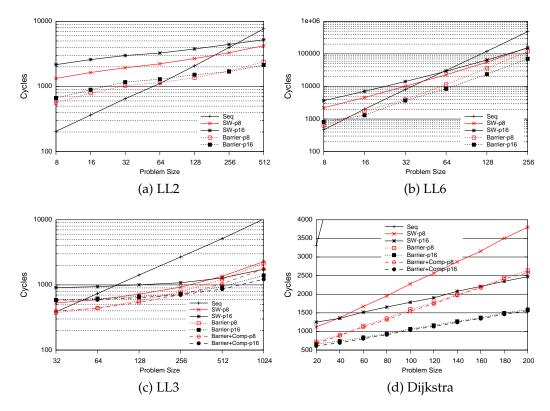

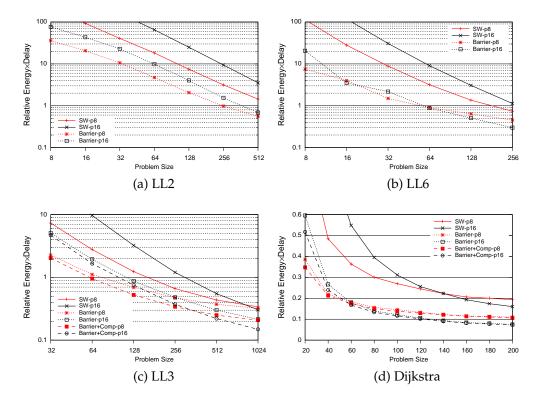

| 5.11       | Per iteration execution time for Livermore loops (a) 2, (b) 6, and                                                                                            |          |

|            | (c) 3 and (d) Dijkstra's Algorithm.                                                                                                                           | 101      |

| 5.12       | Performance improvement of barriers + computation over barri-                                                                                                 |          |

|            | ers alone for (a) <i>LL3</i> and (b) <i>dijkstra</i>                                                                                                          | 102      |

| 5.13       | Energy×delay for Livermore loops (a) 2, (b) 6, and (c) 3 and (d)                                                                                              |          |

|            | Dijkstra's Algorithm relative to sequential execution.                                                                                                        | 104      |

| A.1        | SPL row with power gating support.                                                                                                                            | 111      |

| A.2        | Operation of the Dynamic Partitioning Manager.                                                                                                                | 112      |

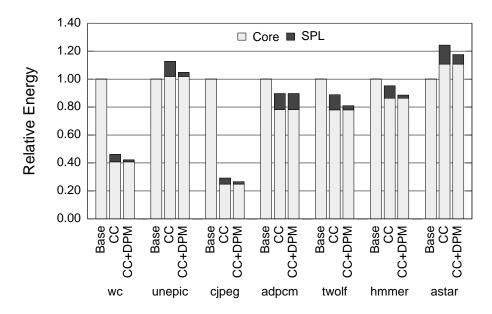

| A.3        | Energy consumption relative to single threaded baseline                                                                                                       | 115      |

| A.4        | Performance of two-application communication + computation                                                                                                    |          |

|            | workloads with 24-row shared, 12-row private, and 24-row dy-                                                                                                  |          |

|            | namically managed SPL, relative to 24-row private SPL per ap-                                                                                                 |          |

|            | plication                                                                                                                                                     | 116      |

| A.5        | Total energy consumption with DPM relative to best performing                                                                                                 |          |

|            | static partitioning per workload                                                                                                                              | 117      |

|            |                                                                                                                                                               |          |

# CHAPTER 1 INTRODUCTION

The microprocessor industry is rapidly transitioning to incorporating multiple processing cores on a single time. While the move away from single complex cores is indisputable, the most profitable way to organize these chip multiprocessors (CMPs) is a topic of ongoing debate. Given the variety of single- and multi-threaded applications that will run on a particular design, it will be extremely difficult to determine the optimal hardware/software system *a priori* at design time.

One attractive approach is to intermix conventional processing cores with reconfigurable logic that can be programmed to assume multiple specialized functions. This approach provides a form of *reconfigurable heterogeneity* that can be matched to changing workload characteristics at runtime. While the physical design may be homogeneous, with identical cores and attached programmable logic fabrics, each fabric can be configured at runtime to perform a different function according to the tasks assigned to the cores, or in the case of homogeneous threads from a parallel application, they may be configured identically.

Numerous proposals [6, 20, 22, 34, 39, 64, 65, 68, 91, 92] exist for integrating reconfigurable logic with general purpose cores. All of these proposals, however, were developed during the single core era and so the fabric was only attached to a single processor. As such, these designs typically suffered from a large area overhead and limited application coverage. The fabric might only speed up 50% of applications, yet consumed 50-75% of the chip area [34, 41, 68, 90, 91]. The recent move to chip multiprocessors, along with continued technology scaling, motivates us to reconsider the integration of reconfigurable logic on chip. Increased transistor density allows the integration of multiple cores and reconfigurable logic on the same die and provides the opportunity to share a single fabric among multiple cores. This amortizes the area overhead, increases the likelihood of use by at least some of the cores, and opens up optimization opportunities that are not possible with private fabrics. With this in mind, we propose RACM<sup>1</sup>, a Reconfigurable Architecture for Chip Multiprocessors designed for the multicore era. RACM tightly integrates reconfigurable logic with traditional general purpose cores. Unlike previous reconfigurable proposals, which were designed for single core processors, RACM, and its associated *Specialized Programmable Logic (SPL)*, is specifically designed with today's chip multiprocessors in mind.

Figure 1.1 provides an overview of RACM, including (a) the integration of the SPL in a heterogeneous multicore system, (b) a high level view of the SPL architecture, (c) the design of the SPL computation cells, and (d) the interaction between the SPL and the RACM cluster manager. As a whole, RACM provides:

- A tightly integrated, row-based reconfigurable fabric to accelerate computation (Chapter 3);

- Mechanisms to temporally and spatially share the fabric among multiple cores (Chapter 3);

- Dynamic cluster management policies to manage the assignment of threads to cores and the partitioning of the fabric (Chapter 4);

- Fine-grained intercore data communication (Chapter 5);

<sup>&</sup>lt;sup>1</sup>Pronounced "rack 'em."

Figure 1.1: Overview of a RACM CMP. (a) Depiction of overall chip, with two SPL clusters and one conventional cluster, and blow-up of one SPL cluster, (b) four-way shared SPL including tables required for communication, (c) design of SPL cell (unless otherwise noted all data paths in the SPL are b bits wide, and (d) SPL Cluster Manager.

- Fine-grained barrier synchronization (Chapter 5);

- The ability to perform computation on data that is being communicated (Chapter 5).

Each of these features will be discussed in the coming chapters.

The next chapter reviews literature related to all of these areas. We first discuss the numerous proposals for reconfigurable fabrics and architectures, focusing particularly on those that deal with the high level integration of a reconfigurable fabric with general purpose processors. Next, we examine prior work that has investigated thread scheduling and dynamic spatial partitioning as it relates to other shared structures, especially caches. Finally, we discuss proposals for fine-grained interthread communication and synchronization.

Chapter 3 details the design of the SPL and those features that we find to be particularly amenable to fabric sharing. Multiple dynamic sharing schemes are proposed and their performance is compared to the performance of providing each core with its own large, private fabric. We find that, with intelligent control policies, shared SPL is able to obtain the same performance as large private fabrics while providing a 4X reduction in fabric area and peak power.

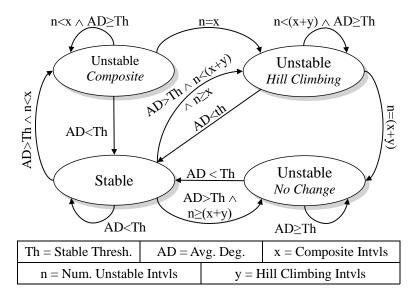

Due to contention and communication issues, the SPL should only be shared among a limited number of cores. As such, there will likely be multiple SPL clusters in future many-core CMPs. The mapping of threads to clusters and the dynamic partitioning of each cluster can play a significant role in the performance obtained by each application. A number of dynamic management schemes are developed in Chapter 4 which control the assignment of threads to clusters and the dynamic partitioning of the SPL in order to maximize performance. The best scheme, Hybrid Heuristic-Hill Climbing (H3C), combines elements of phase analysis, stability detection, and machine learning. Dynamic management with H3C outperforms both the per-workload oracle best static schedule and a system where the SPL is ideally replaced by additional cores.

In addition to reducing area and power overhead, sharing the SPL among multiple cores allows for optimizations not possible with private fabrics. In particular, the shared SPL provides a good platform for performing fine-grained communication between cores. Chapter 5 describes how RACM uses the fabric to allow fine-grained interthread communication and fine-grained barrier synchronization. This fine-grained communication allows parallelization of algorithms that might not otherwise realize a benefit from the additional cores provided in today's CMPs. Using the SPL for communication has the added benefit that computation can often be performed on the data while it is in flight to the consumer, providing performance enhancements not possible with dedicated hardware communication schemes. We show that, in the context of a heterogeneous CMP with both traditional and reconfigurable clusters, RACM can provide significant performance and energy benefits compared to what can be achieved with an area equivalent set of more powerful cores and idealized communication hardware.

5

# CHAPTER 2 RELATED WORK

## 2.1 Reconfigurable Computing

Several survey papers (e.g., [15, 37, 85]) provide an overview of the contributions of prior reconfigurable computing projects. We focus on those proposals that address the design of reconfigurable fabrics tailored to inclusion with general purpose cores, the characteristics of prior approaches that we find particularly amenable to shared fabrics, and the integration of the fabric within a CMP.

## 2.1.1 Fabric Design and Core Integration

Numerous proposals exist for integrating reconfigurable logic with a general purpose processor. Designs such as PRISC [63, 64], OneChip [92], Proteus [18, 19, 20], CoMPARE [68], Stretch [79], Chimaera [39, 93], and DPGA [21, 22] tightly integrate the fabric with the processor as a specializable execution unit. In DISC [90, 91] and NAPA [65] the fabric predominates with the processor serving largely to feed the reconfigurable hardware. Garp [6, 7, 41], PipeRench [34, 35, 69], and Tartan [56] fall in between.

Garcia and Compton [31] investigate a reconfigurable system in which the processor and reconfigurable fabric communicate via virtual memory. Carrillo and Chow [8] and Dales [18, 19, 20] evaluate the high level integration of a reconfigurable fabric with a single core processor and the overall system performance it provides. All of these, however, only investigate the integration with a

single core, although Garcia and Compton [31] state that their technique could be extended to a multicore system.

In [32], configuration data for a reconfigurable coprocessor is shared among multiple cores with the goal of increasing fabric utilization by allowing a larger number of configurations to concurrently exist in the fabric. Chen et al. [11] investigate the benefits of including reconfigurable ISA support in a multicore processor and find that combining program parallelization with custom ISA support provides larger speedups than the product of the two techniques applied in isolation.

The aforementioned designs have largely focused on accelerating certain application classes that see significant benefits from reconfigurable hardware. In addition to application acceleration, integrated reconfigurable hardware has been shown to be useful in other areas, such as aiding fault tolerance [74] and creating instruction path coprocessors to perform trace construction and optimization [14].

Reconfigurable computing has recently been gaining increasing attention from industry. Both Intel and AMD allow tighter integration of FGPAs with general purpose processors through HyperTransport, QuickPath, and licensing of front side bus technology [26, 27]. Convey Computer's HC-1 pairs an Intel processor with a reconfigurable coprocessor and allows different instruction sets to be loaded into the coprocessor [17].

#### 2.1.2 Fabric Characteristics for Sharing

Several efforts have developed reconfigurable fabrics whose characteristics – in particular *higher computation granularity, row based design,* and *virtualization* – we find to be highly amenable to efficient SPL sharing.

Multiple works utilize coarser computation granularities than the bit-level configurability supported by FPGAs. Garp [41] and PipeRench [34], for example, use two and eight bits, respectively, as the smallest computation granularity. Using larger granularities reduces power, area, and configuration information at the cost of flexibility and density in design mapping. Most general purpose applications, however, do not require bit-level manipulation and so the savings tend to outweigh the costs. While this does not directly ease sharing *per se*, it does significantly reduce area and power.

Row based reconfiguration is employed by a number of designs [34, 90, 93] for several reasons. The cycle time of the fabric is set by the row delay and thus remains constant for all configurations. Using row based fabrics makes hardware design and application mapping easier and significantly reduces the routing complexity over traditional FPGA architectures. It also makes partial reconfiguration of the fabric easier as designs occupy a certain number of rows; so long as that number of rows is available in the fabric, it can be reconfigured by reprogramming only those rows.

Virtualization, such as that employed by PipeRench [34, 35], allows the fabric to handle configurations that require more rows than are physically available in the fabric. The costs of virtualization are degraded throughput, since the design

can no longer be fully pipelined, and higher power. Despite these drawbacks, virtualization is a key component of efficient shared fabrics.

## 2.2 Thread Scheduling

The benefits of dynamic thread scheduling in small scale CMP/SMT systems has previously been explored for a number of purposes, including cache-aware scheduling [10, 25, 47, 82] and thermal and power management [16]. Most of these efforts deal with temporally scheduling threads between time slices where the number of threads is greater than the number of processor contexts.

Cache-aware scheduling aims to minimize contention or maximize sharing between threads scheduled in the same interval. Tam et al. [82] create sharing vectors based on performance monitoring unit (PMU) data to cluster threads that share data in order to minimize long latency cross-core or cross-chip cache accesses. Fedorova et al. [25] use balance-set scheduling to create L2 conscious schedules. Chen et al. [10] investigate a parallel depth first task scheduling algorithm to increase data locality for certain parallel algorithms.

Constantinou et al. [16] investigate the performance impact of saving different portions of the processor state, including cache and predictor state, when migrating threads at various scheduling granularities. Such migrations might be used to minimize thermal variations or, in a heterogeneous CMP, to improve power efficiency by placing a thread on the core best suited to its current needs.

Thread assignment for a shared reconfigurable fabric shares some similarity with SMT scheduling. Snavely and Tullsen [76] use a trial based technique of sample and "symbios" phases in which they sample the performance of a small number of possible schedules for a short period and choose the best performing of these schedules to run for the longer "symbios" phase. El-Moursy et al. [24] investigate continuous, on-the-fly thread scheduling based on a number of different possible metrics.

In the realm of reconfigurable computing, previous work has investigated the issue of configuration scheduling [2, 29]. Configuration scheduling tries to determine which implementation (either software or one of possibly many hardware implementations) should be employed for a particular function given current performance, area, and power restrictions. Our work is orthogonal to configuration scheduling and the two could be combined to further reduce conflicts for the SPL and improve performance.

### 2.3 Dynamic Resource Sharing

Previous research has proposed sharing other architectural components among multiple cores. L2 caches are likely the most prominent shared component with numerous works addressing how to best allocate cache space among multiple threads [12, 46, 80]. Sun's UltraSPARC T1 [81] shares a single floating point unit among its eight SMT cores. Kumar et al. [48] investigate sharing floatingpoint units, crossbar ports, and L1 instruction and data caches between two cores. Their work, however, focuses largely on temporal sharing, and does not consider dynamic spatial techniques such as splitting a cache in half if interthread conflicts are too high. Prior work that optimized resource allocation during different program phases [23, 73] focused solely on single, sequential applications. In our multithreaded environment, each thread has its own current phase and we must deal with optimizing thread assignment and resource allocation as phases change across multiple applications.

Our situation is more difficult than any of this previous scheduling and shared resource work as we must concurrently manage both the assignment of threads to clusters and the dynamic partitioning of the fabric.

#### 2.4 Fine-Grained Interthread Communication

StreamIt [36, 84] is a programming language and compiler infrastructure aimed at easing the use of pipeline parallelization. Decoupled Software Pipelining (DSWP) addresses hardware options for implementing fine-grain communication [61, 62], automatic extraction of streaming threads [57], data parallelization of pipeline stages [60], and speculative DSWP [87]. The Synchronized Pipelined Parallelism Model [88] parallelizes programs into a series of producing and consuming threads to keep data on-chip for as long as possible to minimize off-chip accesses.

SCORE [9] employs a stream computing model and targets reconfigurable systems. The design incorporates a single CPU and multiple reconfigurable blocks and streaming occurs between reconfigurable blocks over a dedicated interconnect. In our work, communication occurs between CPUs and the shared reconfigurable fabric is used to perform the communication. None of this prior work evaluates the energy efficiency implications of streaming. Energy usage is a non-trivial concern given the fact that streaming tends to provide less than ideal speedups.

## 2.5 Fine-Grained Synchronization

Beckmann and Polychronopoulos [3] and Shang and Hwang [72] both propose hardware mechanisms for performing barriers using dedicated interconnect and hardware tables. IBM's Cyclops architecture [5] provides dedicated hardware support for barriers through a special purpose register and wired-OR. Sampson et al. [67] propose barrier filters to eliminate the dedicated interconnect required in most barrier synchronization proposals. The Multi-ALU Processor [45] provides an explicit barrier instruction in the ISA and supports register to register communication between clusters.

#### CHAPTER 3

#### SHARED RECONFIGURABLE ARCHITECTURES FOR CMPS

Despite its potential, reconfigurable logic as an attached customizable unit has not yet been widely embraced by mainstream microprocessor manufacturers. One major impediment is the large power and area costs of FPGA technology relative to fixed functionality hardware [50]. While researchers have made significant progress in devising specialized fabrics to bridge this gap, many microprocessor architects still view the costs as too high to justify their mainstream adoption.

RACM addresses this gap by sharing a *Specialized Programmable Logic (SPL)* fabric among multiple cores. In this chapter, we describe the microarchitecture and low-level hardware control for shared SPL. In a multicore system where each core is coupled with its own fabric there are inevitably periods where one fabric is highly utilized while another lies largely or even completely idle. Thus, by *sharing* SPL fabric resources among multiple processor cores, programmable logic can be much more efficiently integrated – at far less power and area cost – into future multicore microprocessors.

In RACM, a number of standard cores share a common pool of SPL. Depending on the particular needs at any given point in time, each pool is dynamically partitioned among the cores, either *spatially*, where the shared fabric is physically partitioned among multiple cores, *temporally*, where the fabric is shared in a time multiplexed manner, or a combination of both. We show in Section 3.3 that pooled SPL configurations guided by effective control policies have little impact on performance for both parallel and coarse-grain multithreaded workloads – compared to private SPL attached to each core – while significantly reducing SPL area and energy costs.

#### **3.1 SPL Architecture**

In this section, we first motivate the need for research in more efficient SPL integration in CMPs, and quantitatively demonstrate the overall benefits of our approach. We then describe the RACM architecture, including high level system integration, the SPL microarchitecture, and our dynamic sharing control policies.

#### 3.1.1 Motivating Example

We motivate our work by demonstrating the drawbacks of a straightforward application of prior SPL approaches to a CMP and the substantial benefits of intelligent SPL sharing. Figure 3.1(a) depicts a floorplan – with the L2 omitted but remaining areas drawn to scale – for a portion of a large-scale multicore chip<sup>1</sup> with eight single-issue out-of-order cores, each of which is coupled with an SPL fabric. Each SPL contains 26 rows of programmable logic, just enough to avoid virtualization for all eight applications. (Application statistics and modeling methodology are described in Section 3.2.)

The SPL area is roughly twice that of each core. Granted, a more complex core would consume more area, and we explore such options later in this chapter. Still, from an area and utilization perspective, there is clearly room for improvement. Figure 3.2 shows the utilization (percentage of the total number

<sup>&</sup>lt;sup>1</sup>Other regions of the die may contain only cores and no SPL.

Figure 3.1: Sample floor plans for a portion of a multicore chip with (a) 26-row private, (b) 6-row private, and (c) 4-way shared SPL.

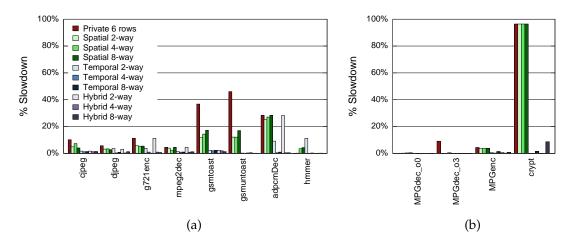

Figure 3.2: SPL utilization for private and shared SPL organizations. \*The last set of bars shows percentage slowdown relative to 26-row private SPL.

of rows that are in use on average) and performance of several SPL configurations for a coarse-grain multithreaded workload of eight single-threaded applications, each of which runs on one of the eight cores. The leftmost bars for the individual benchmarks show the utilization of the 26-row configuration of Figure 3.1(a). The utilization of all eight of the SPL fabrics is less than 10%, and the average SPL utilization is only 3.4%. Reducing each SPL to 6 rows (next set of bars) markedly increases SPL utilization for some benchmarks; moreover, the area is greatly reduced as shown in Figure 3.1(b). However, this comes at a high cost: an 18% overall performance loss, since all benchmarks use more than 6 rows.

By intelligently sharing the SPL among multiple cores, the average number of rows for each core *can* be reduced to six with little performance loss relative to the private 26-row configuration. Figure 3.1(c) shows a floorplan with two pools of SPL, each of which contains 24 rows and is shared – using control policies that we describe in Section 3.1.7 – among four cores. This configuration reduces the SPL area and peak power costs by over 4X. Furthermore, as shown by the third AvgUtilization bar<sup>2</sup> in Figure 3.2, the average utilization of the fabrics increases as well. These benefits come with virtually the same performance as the 26-row private configuration. The rightmost bars show that a single 48-row SPL shared among all eight cores further improves utilization, and also suffers negligible performance loss.

The contrast in performance between the private six-row and four-way shared SPL configurations – which have the same total number of SPL rows – motivates the need for good sharing policies. The six-row private configuration can be viewed as a spatially shared SPL organization with a naïve control policy that equally divides the SPL among all cores at all times. The shared configurations use a more intelligent policy that eliminates the 18% performance loss of the naïve approach.

<sup>&</sup>lt;sup>2</sup>We do not show utilization for individual benchmarks since the fabrics are shared among multiple benchmarks.

### 3.1.2 System Overview

Figure 1.1(a) shows an overall depiction of a 20 core CMP with three *clusters*<sup>3</sup>, with the external interface not shown for simplicity. Each of the two clusters on the left hand side consists of four single issue out-of-order processor cores<sup>4</sup> sharing a common pool of SPL. The SPL is a highly pipelined, row-based reconfigurable fabric and is described in more detail in Section 3.1.4. In the "conventional" cluster on the right hand side of Figure 1.1(a), each fabric has been replaced by two additional cores, giving 12 cores in total. Applications that are not compiled to use the SPL run on this conventional cluster, while those that exploit SPL run on one of the two left clusters.

#### 3.1.3 Core/Fabric Integration

As with a number of previous designs [20, 64, 79, 93], the SPL fabric is tightly integrated with the processor core as a reconfigurable functional unit. However, rather than consume additional register file ports, we use a queue-based decoupled architecture to interface the SPL to the memory system. The SPL input queue matches the row input width and special SPL load instructions place values into the queue at a particular data alignment. Likewise, instead of writing to the register file, the SPL writes to an output queue that is then written out to the Store Queue using special SPL store instructions. Since the normal LSQ/cache datapath is used for data transfer, no additional steps are needed to handle memory dependences with the processor core.

<sup>&</sup>lt;sup>3</sup>Although relative sizes of the cores and SPL are accurate, this is not intended to represent an actual floorplan.

<sup>&</sup>lt;sup>4</sup>An analysis of different complexity cores and the reasons for selection of single issue outof-order cores for the final design will be discussed in the following sections.

As discussed in Section 2.1, row-based designs employing virtualization are highly amenable to sharing. Figure 1.1(b) shows how our row-based SPL is modified to enable both spatial and temporal sharing between two cores. For spatial sharing, additional muxes select input bits at the entry point of the SPL and at each point where the SPL pool might be partitioned. Furthermore, an additional set of tristate drivers tap off of each row output to drive the sharer's output queue. Finally, there is additional wire overhead to get data to and from multiple cores. These wires can be pipelined if necessary to match the SPL clock frequency at the cost of additional pipeline initiation time. However, with deeply pipelined row-based fabrics, the cost is small and is outweighed by the efficiency gains.

For temporal sharing, all rows of the fabric are available to all cores in a time multiplexed fashion. Therefore, only the muxes at the head of the fabric are required.

### 3.1.4 Fabric Microarchitecture

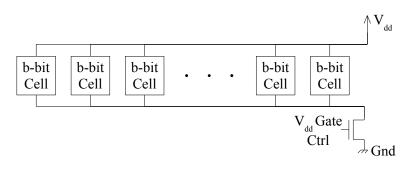

An SPL fabric consists of a collection of rows. Each row contains c cells, and each cell computes b bits of data. Figure 1.1(c) shows the cell and row design. The major cell components are a main 4-input look-up table (4-LUT), a group of 2-LUTs (equivalent to one 3-LUT) plus a fast carry chain to compute carry bits or other logic functions if carry calculation is not needed, barrel shifters to properly align data as necessary, flip-flops to store results of computations, and an interconnection network between each row. Within a cell, the same operation is performed on all b bits. These b-bit cells are arranged in a row to form a

$c \times b$ -bit row. Each cell can perform a different operation on its inputs and a number of rows are grouped together to execute an application function. The clock frequency is set such that the longest possible computation within a row completes in a single SPL clock cycle.

As shown previously [34], several trade offs dictate the optimal choice of cell width, row width, and number of rows. Increasing the cell bit width decreases area and power at the cost of less configuration flexibility. Increasing the row width allows more computation in a single cycle but also increases the likelihood of less than 100% resource utilization if not all of the cells in a row can be put to use. Furthermore, the fabric width should match the ability of the memory system to supply data at a fast enough rate. Finally, reducing the number of rows has linear area and power benefits but increases the number of functions that must be virtualized.

To quantitatively evaluate these trade offs, we create analytical area, latency, and power models for SPL in 65nm technology. The model combines estimates for the different components of the fabric. We use Cacti 4.2 [83] to model LUTs, Orion [89] for between row interconnect modeling, the models of [42] for local wiring and between cell wires (such as for the barrel shifter and carry logic not included in the Orion model), and the work of [40] for the carry chain logic implementation. Finally, various bit level components, such as transistor delay, area, and power, used to compute estimates for muxes and small SRAM cells, are taken from the ITRS [70].

To validate our model, we compare scaled values of area, latency, and power available from previous reconfigurable fabric designs [41, 69, 39] with predictions by our model for these fabric architectures. The results are given in Ta-

|                                             | Scaled Actual | Model | % Diff |  |

|---------------------------------------------|---------------|-------|--------|--|

| PipeRench - 8-bit, 16-cell, 16-row - 180 nm |               |       |        |  |

| Area (mm <sup>2</sup> )                     | 1.5           | 1.59  | 6.0%   |  |

| Frequency (MHz)                             | 350           | 460   | 31.4%  |  |

| Power (W)                                   | 0.929         | 0.832 | -10.5% |  |

| Chimaera - 1-bit, 32-cell, 32-row - 0.6 µm  |               |       |        |  |

| Area (mm <sup>2</sup> )                     | 0.805         | 0.751 | -6.7%  |  |

| Frequency (GHz)                             | 1.27          | 1.06  | -16.5% |  |

| Garp - 2-bit, 24-cell, 32-row - 0.5 μm      |               |       |        |  |

| Area (mm <sup>2</sup> )                     | 1.32          | 1.06  | -19.7% |  |

Table 3.1: Comparison of data from actual reconfigurable fabrics (scaled to 65nm) and the analytical model.

ble 3.1. The Scaled Actual Area values in this table are derived by scaling the fabric area of each design by the square of the ratio of the technology factors. For frequency, the reported values are linearly scaled by the technology ratio. The Scaled Actual Power value for PipeRench is derived by scaling the reported power value by the square of the ratio of the PipeRench voltage to the SPL voltage, by the ratio of the PipeRench frequency to the SPL frequency, and by the ratio of the technology factors (to account for capacitance scaling). The model achieves good correlation except for the frequency in PipeRench and Chimaera and the area of Garp. For PipeRench, the PipeRench paper notes that the circuit design was not highly optimized [69], and therefore we expect that a frequency closer to our higher value could be achieved in an industrial PipeRench design. Given the seven technology generations between our design and Chimaera, a 16% error is not unexpected. For the area disparity with Garp, the information available for Garp is limited, making good correlation with the Garp design difficult. Specifically, only the area of the entire Garp chip is provided and we determine the area consumed by the fabric by determining the ratio of fabric area to total chip area from the provided floorplan.

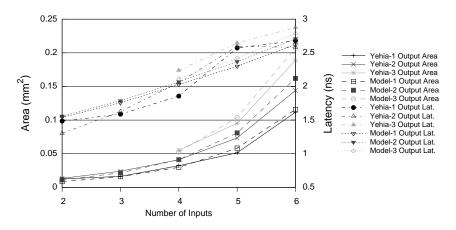

Figure 3.3: Comparison of latency and area predicted by analytical model to results reported in [95].

Yehia et al. [95] perform an area and latency design space exploration for programmable function units with varying number of inputs and outputs (among other parameters). Figure 3.3 shows area and latency comparisons between our model and the results presented by [95] for fabrics with different numbers of row inputs and outputs. The model error is within 15% in all but two cases.

We use our model to estimate the costs of different configurations for the various functions that we map to the SPL (discussed in Section 3.2). An 8-bit wide cell with 128-bit wide rows provides a good compromise between flexibility and area/power cost, and permits significant parallelization. Each SPL function can take in up to 512 bits of input and can produce up to 128 bits of output. This organization achieves a reasonably high frequency (500MHz) relative to the processor core frequency (assumed 2GHz at 65nm, the same as the Pentium Core2 Duo [43] and the AMD X2 Dual-Core [1], both of which are implemented in the same 65 nm technology). At this one-quarter clock speed differential, four quadword load instructions can supply 512 bits to the SPL pipeline every SPL clock period.

|      | Area | Dynamic Power | Leakage Power |

|------|------|---------------|---------------|

| IO   | 1.00 | 1.00          | 1.00          |

| 0001 | 1.19 | 1.06          | 1.05          |

| 0002 | 1.82 | 1.26          | 1.26          |

| 0004 | 4.87 | 1.66          | 1.63          |

| SPL  | 2.49 | 0.66          | 3.02          |

Table 3.2: Area and power of different core types and 26-row SPL normalized to IO area and power.

For the baseline 26-row private SPL, we include on-chip storage for eight configurations to allow for fast switching between different configurations. For our workloads, this permits all configurations for any phase to reside on-chip. Thus, reconfiguration latency is not an issue as all configurations are immediately available after the initial configuration overhead is paid.

To gauge the sensitivity of our evaluation to the exact details produced by our model we evaluated an SPL design where the SPL is 50% slower than described above (i.e., one SPL cycle is equivalent to six processor cycles). Despite this 50% increase in latency, our workloads experienced only an average 12-16% lower performance than the 4 cycle baseline depending on the complexity of the attached core. This confirms that our conclusions are not overly reliant on the exact results of our model. Even if the SPL opperates a little slower than predicted, similar performance benefits can still be achieved.

Table 3.2 shows the area and power of a 26-row SPL compared with four conventional core types: a single-issue in-order core (designated as IO), and one-, two-, and four-way issue out-of-order cores (OOO1, OOO2, and OOO4). Results are normalized relative to the IO core. Each core has separate 8 kB L1 instruction and data caches. We adopt the methodology of Kumar et al. [49] to calculate per-core area and power costs. We note that an OOO1 core augmented

|                   | Rows/<br>SPL | Configs/<br>Row | Total SPL<br>Area (mm <sup>2</sup> ) | Dynamic<br>Energy/<br>Row (nJ) | Total SPL<br>Leakage<br>Power (W) |

|-------------------|--------------|-----------------|--------------------------------------|--------------------------------|-----------------------------------|

| Eight Private     | 26           | 8               | 23.74                                | .0600                          | 4.59                              |

| Four 2-way Shared | 12           | 8               | 5.55                                 | .0601                          | 1.06                              |

| Two 4-way Shared  | 24           | 10              | 6.03                                 | .0601                          | 1.08                              |

| One 8-way Shared  | 48           | 12              | 6.62                                 | .0601                          | 1.10                              |

Table 3.3: SPL configurations and associated area and power costs.

with SPL has an area that falls between OOO2 and OOO4, while the area of OOO2 + SPL is slightly less than that of OOO4.

We create shared SPL configurations by pairing OOO1 cores with an SPL that consumes approximately half the area of the sharing cores. OOO1 cores are selected as, of the cores investigated, adding SPL to single-issue out-of-order cores provides the greatest relative benefit (see Section 3.3.1 for further details). A six row SPL consumes slightly more than half the area of an OOO1 core and the combination of the two is smaller than OOO2.