# BULK TITANIUM WAVEGUIDE – A NEW PLATFORM FOR UNIPLANAR MICROWAVE CIRCUITS AND RFMEMS

### A Dissertation

Presented to the Faculty of the Graduate School

Of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by Xiaojun Huang January 2008

# BULK TITANIUM WAVEGUIDE – A NEW PLATFORM FOR UNIPLANAR MICROWAVE CIRCUITS AND RFMEMS

Xiaojun Huang, Ph.D.

## Cornell University 2008

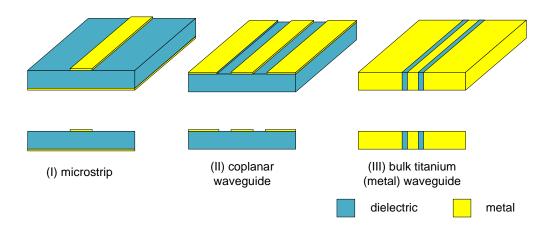

The majority of uniplanar circuits are based on transmission lines of two basic topologies: Microstrip and Coplanar Waveguide (CPW). Microstrip offers low loss, while suffering from large circuit size, high dispersion, poor design flexibility, and the necessity of large via holes. CPW improves upon microstrip by bringing the ground to the same level as the signal, therefore providing low dispersion, smaller circuit size, high design flexibility and no via holes. However, the fields in CPW concentrate on the thin edges and are therefore less confined. This translates into higher conductor loss, cross-talk and poor power handling capability.

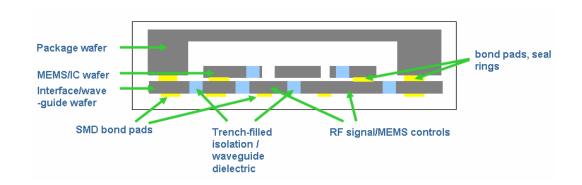

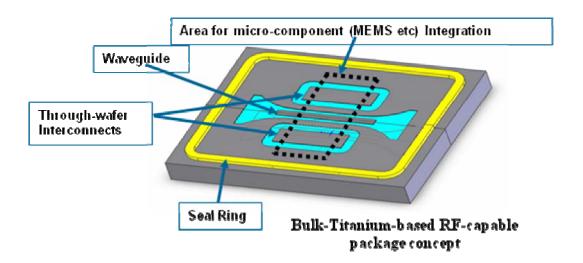

We present a new topology for uniplanar microwave circuitry: bulk titanium waveguide. The waveguide is formed by coplanar titanium segments separated by low-loss dielectric that is planarized to the same level as the titanium. Due to the high aspect ratio of the dielectric cross section, the electric field is confined primarily within the dielectric, therefore reducing losses due to radiation and parasitic coupling. This geometry distributes the surface current across the entire height of the structure, reducing conductor losses while enhancing power handling capabilities. The high aspect ratio in-plane electrical isolation also provides through-wafer interconnects with a high packing density. When integrated with a bulk titanium package, this waveguide provides a robust, compact, packaging solution for microwave subsystems as well as other microcomponents such as MEMS. We have successfully designed, fabricated and characterized packaged waveguides which measured, at 40GHz, ~0.7dB/mm insertion loss and the impact due to package < 0.1dB. Additionally, we

developed a quasi-static model based on conformal mapping that accurately describes the characteristics of the waveguide.

Titanium has one of the highest strength to weight ratio among metals. It is naturally resistant to corrosive environments and is a widely used as implants due to its bio-compatibility. Titanium is also one of the few materials with an endurance limit, which means that it can be deformed repeatedly without breaking. However, the current manufacturing processes for titanium sheets are not tailored for microfabrication. We developed a suite of technologies that overcome issues such as residual stress, thickness variation, embedded defects and surface roughness.

### BIOGRAPHICAL SKETCH

Xiaojun Trent Huang grew up in Luoyang, China, where he lived until the age of 15 when he moved to Hefei, China to attend the University of Science of Technology of China. After college, he entered the University of Virginia for graduate studies. Upon receiving a M.A. in physics, he entered Cornell University for his PhD. He paused his study at Cornell and joined the high-tech industry and worked for several years in areas of optics and RFMEMS, before joining UCSB as a post-graduate researcher, when he started his research on bulk-titanium RFMEMS. He received his PhD in 2008 and is currently working on RFMEMS and Micro-fluidics.

To my family

### ACKNOWLEDGMENTS

The road leading to my Ph.D. has not been a straight and easy one. A number of people have helped tremendously. First and foremost, I would like to thank Prof. MacDonald for his consistent support and guidance over the years, without which this work would not have been possible. I especially appreciate the freedom he gave me in pursuing innovations in my research. I am extremely grateful for the understanding and consideration from Prof. Pollock, Kan, and Spencer, who agreed to serve on my committee on short notices. I would also like to thank Prof. Bhave, who generously acted as proxy due to Prof. Spencer's absence at my defense.

Seven years' of departure from Cornell is a long time and that alone could have been an impassible hurdle, if not for the kind help from Barb at the Graduate School and Scott at the School of Electrical Engineering. I truly appreciate their consideration and professionalism.

I would like to thank Shane and Changsong for their significant contributions to the research. Special thanks to Masa and Dave for their continuous support and numerous insightful discussions.

Working with such an intelligent and dynamic group at UCSB has been a wonderful experience in my life. Payam, Marco, Emily, Yanting, Adam(s), Seth, Marcus, have all been very helpful and pleasurable researchers to work with. Last, I would also like to thank Prof. Kim Turner's group for their help and support.

# TABLE OF CONTENTS

| BIOGRAPHICAL SKETCH                                         | iii    |

|-------------------------------------------------------------|--------|

| DEDICATION                                                  | iv     |

| ACKNOWLEDGEMENTS                                            | v      |

| TABLE OF CONTENT                                            | vi     |

| LIST OF FIGURES                                             | viii   |

| LIST OF TABLES                                              | XV     |

| CHAPTER ONE: INTRODUCTION                                   |        |

| 1.1 Bulk metal waveguide concept and performance highlights | 2      |

| 1.2 Fabrication and associated issues                       | 5      |

| 1.3 Achievement highlights                                  | 6      |

| 1.4 Bulk titanium as MEMS material                          | 8      |

| 1.5 Current development in TiMEMS                           | 10     |

| 1.6 Dissertation organization                               | 12     |

| CHAPTER TWO: CONCEPT AND THEORETICAL ANALYSIS FOR           |        |

| PACKAGED BULK-TITANIUM WAVEGUIDE                            |        |

| 2.1 Concept and key features                                | 17     |

| 2.2 Microwave modeling                                      | 24     |

| CHAPTER THREE: TITANIUM PLANARIZATION PROCESS DEVELO        | PMENT  |

| 3.1 Background                                              | 44     |

| 3.2 Titanium stress-anneal flattening process               | 50     |

| 3.3 Titanium lapping and polishing process                  | 57     |

| CHAPTER FOUR: BULK TITANIUM WAVEGUIDE PROCESS DEVELO        | OPMENT |

| 4.1 Process overview                                        | 77     |

| 4.2 Titanium deep etch                                      | 81     |

| 4.3 Conductivity enhancement with sidewall Au deposition                | 86        |

|-------------------------------------------------------------------------|-----------|

| 4.4 Deep trench-filling process                                         | 88        |

| 4.5 Planarization and electrical interconnection formation              | 100       |

| 4.6 Packaging                                                           | 107       |

| CHAPTER FIVE: RF PERFORMANCE OF BULK TITANIUM WAVEGUII                  | DES       |

| 5.1 RF measurement setup                                                | 113       |

| 5.2 Waveguide design                                                    | 118       |

| 5.3 RF calibration                                                      | 122       |

| 5.4 Measurement/calibration errors                                      | 126       |

| 5.5 RF simulation                                                       | 127       |

| 5.6 Loss characterization                                               | 134       |

| 5.7 Effects due to processing imperfections                             | 138       |

| 5.8 Impact from packaging                                               | 140       |

| 5.9 Summary and technology comparison                                   | 142       |

| CHAPTER SIX: FUTURE DIRECTIONS: APPLICATIONS BASED ON                   | BULK-     |

| TITANIUM RF PLATFORM                                                    |           |

| 6.1 Discontinuities in bulk titanium waveguide                          | 148       |

| 6.2 Applications based on BTW RF platform                               | 153       |

| 6.3 Summary                                                             | 161       |

| APPENDIX                                                                |           |

| A Derivation for field equations for waveguides with an arbitrary cross | s-section |

|                                                                         | 166       |

| B Conformal mapping analysis of a finite parallel plate waveguide       | 168       |

| C De-embedding procedures for TRL calibration                           | 171       |

# LIST OF FIGURES

| Figure 1-1 Bulk titanium waveguide compared to conventional planar circuits          | 2    |

|--------------------------------------------------------------------------------------|------|

| Figure 1-2 Packaging for bulk titanium waveguide                                     | 3    |

| Figure 1-3 Packaged bulk-titanium-waveguide-based RFMEM-capable system               | 4    |

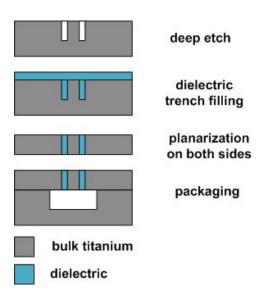

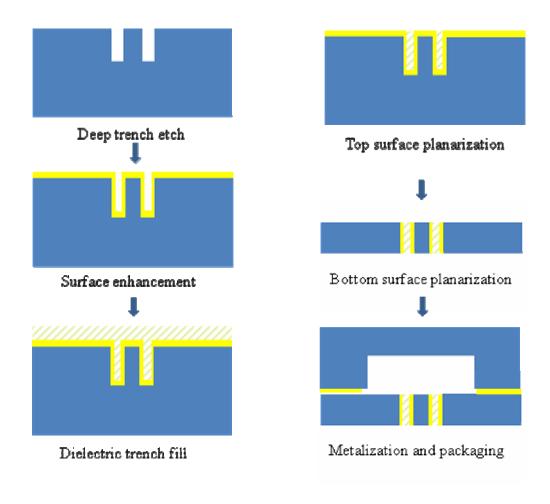

| Figure 1-4 Simplified fabrication sequence of packaged bulk titanium waveguide       | 5    |

|                                                                                      |      |

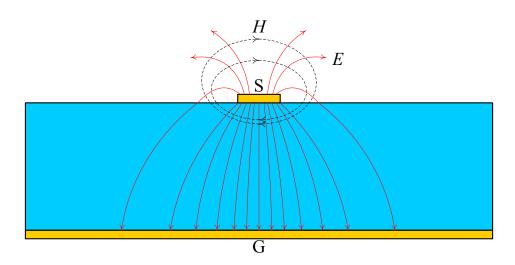

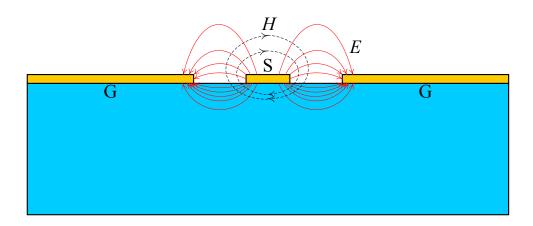

| Figure 2-1 Schematic of a microstrip waveguide                                       | 18   |

| Figure 2-2 Schematic of a CPW                                                        | 19   |

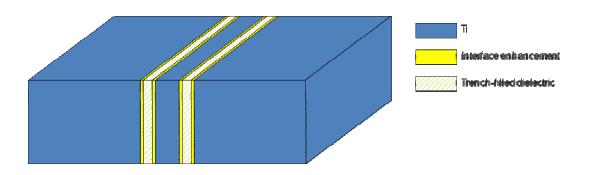

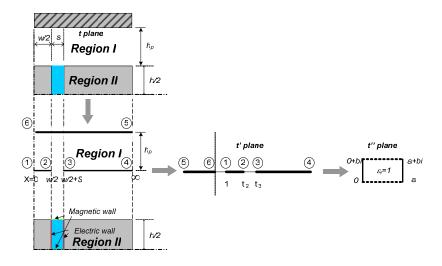

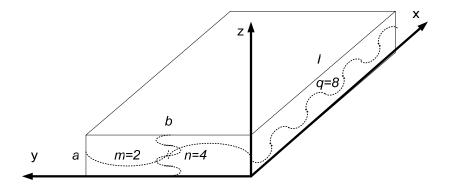

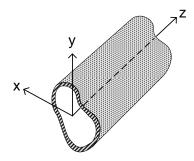

| Figure 2-3 3-dimensional schematic of bulk titanium waveguide                        | 21   |

| Figure 2-4 bulk-titanium packaged waveguide with interconnects and seal ring for     |      |

| packaging                                                                            | 22   |

| Figure 2-5 Fabrication process for bulk titanium waveguide                           | 23   |

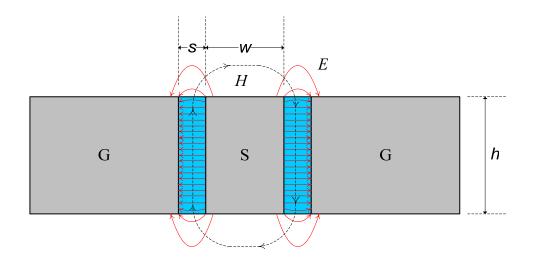

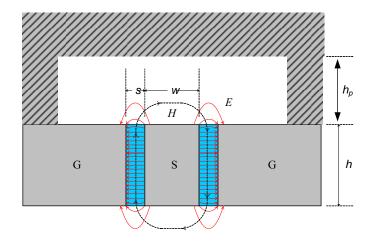

| Figure 2-6 Cross section of bulk titanium waveguide                                  | 27   |

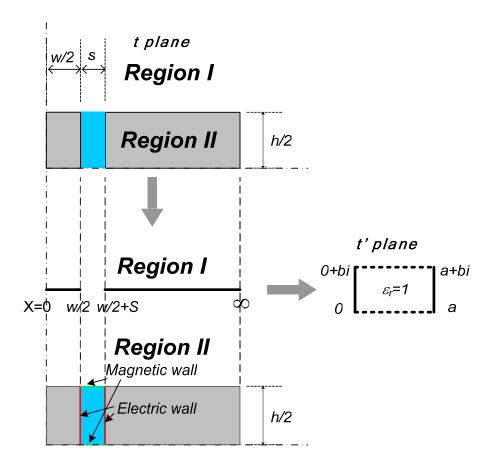

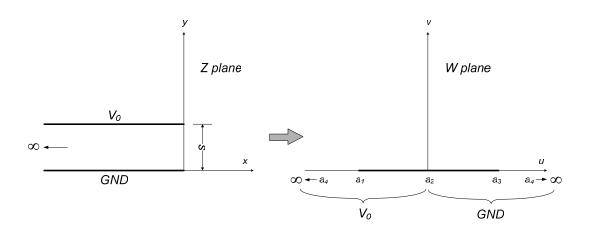

| Figure 2-7 Conformal map for bulk titanium waveguide analysis                        | 30   |

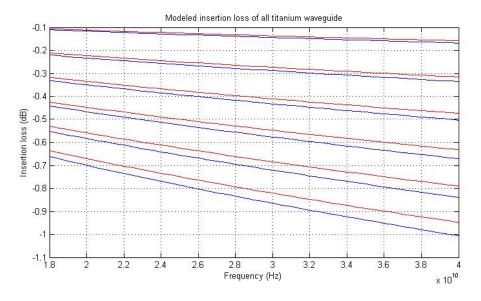

| Figure 2-8 Modeled insertion loss of titanium waveguides of different lengths        | 35   |

| Figure 2-9 Insertion loss vs. trench aspect ratio                                    | 36   |

| Figure 2-10 Schematic of bulk titanium waveguide packaged with a conductive cap      | ρ 37 |

| Figure 2-11 Conformal map for packaged bulk titanium waveguide                       | 38   |

| Figure 2-12 Comparison of current distributions in bulk titanium waveguide (top) a   | and  |

| conventional CPW (bottom)                                                            | 41   |

|                                                                                      |      |

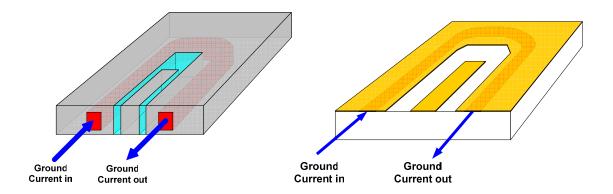

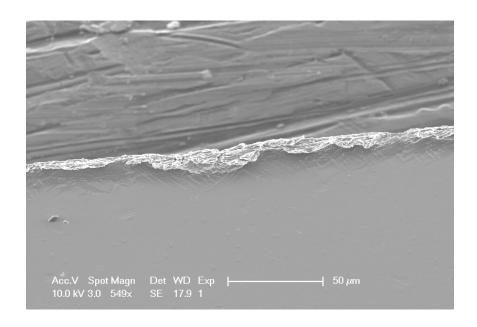

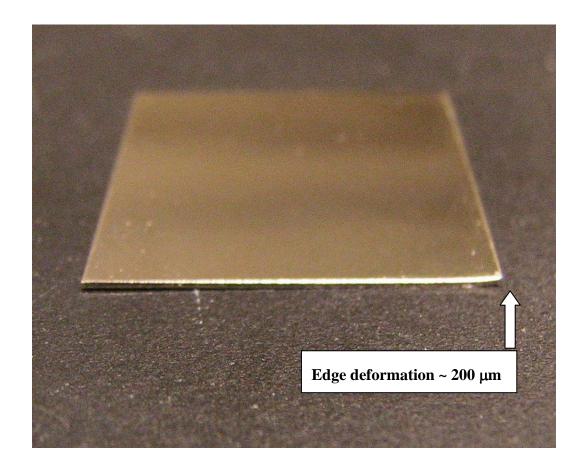

| Figure 3-1 Diced CP titanium sample edge burr                                        | 45   |

| Figure 3-2a Edge burr created by hydraulic press. Left: 1"x1"x50 $\mu m$ CP titanium |      |

| sample as cut from a flattened sheet. Right: 1"x1" sample after flattening anneal    | 45   |

| Figure 3-2b Edge burr on 1"x1"x200 µm CP titanium sample as cut by hydraulic p       | ress |

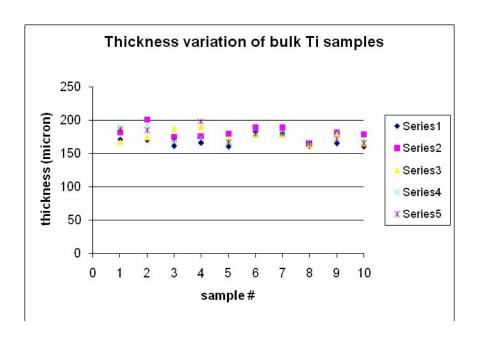

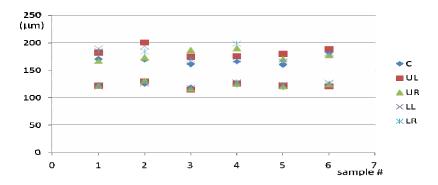

| Figure 3-3 Thickness variation of 10 bulk titanium samples. Different series number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ers   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| represent measurements taken at 5 locations on each sample: center and 4 corners                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47    |

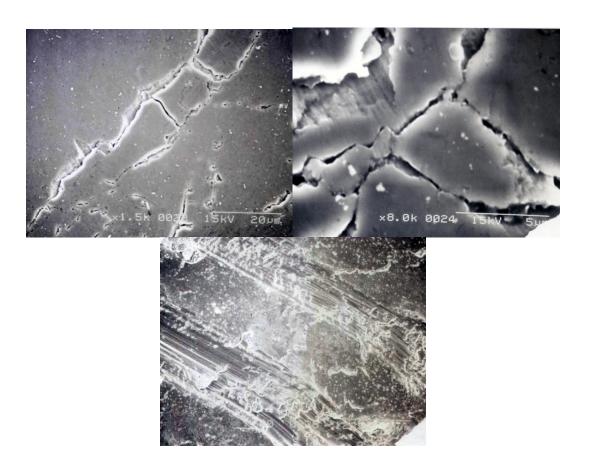

| Figure 3-4 Surface defects of bulk titanium substrates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48    |

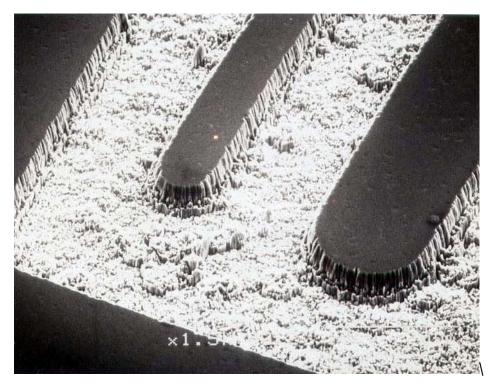

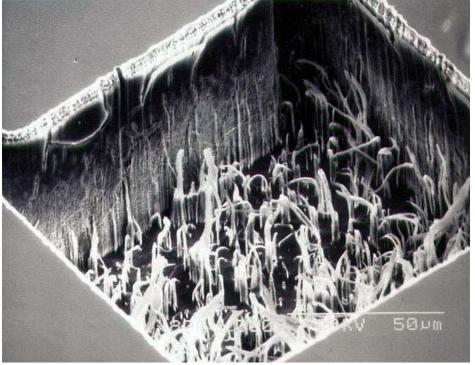

| Figure 3-5 Micromasking(grassing) from dry etching of bulk titanium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 49    |

| Figure 3-6 Gross deformation of as-obtained bulk titanium substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50    |

| Figure 3-1 CP titanium grain size vs. annealing temperature [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53    |

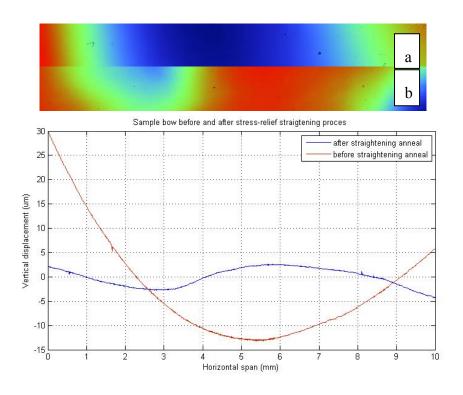

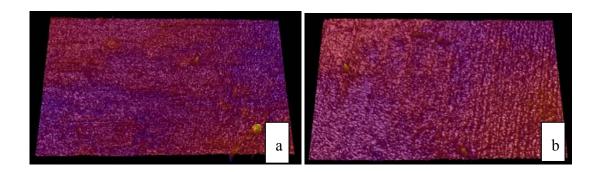

| Figure 3-2 Bulk titanium sample profile measurement in a 10 mm x 1 mm are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | a: a) |

| before stress-relief anneal: maximum bow ${\sim}42~\mu m;$ b) after stress-relief anneal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | neal: |

| maximum bow~6μm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54    |

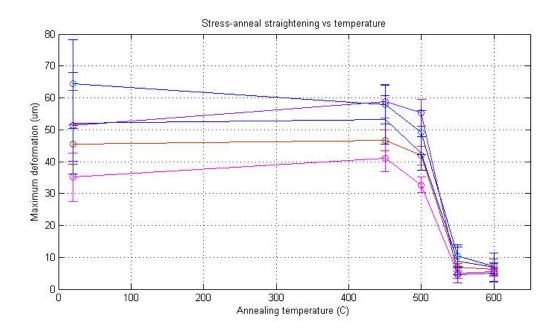

| Figure 3-3 Stress-anneal straightening of 5 1"x1", 200 $\mu m$ Ti samples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55    |

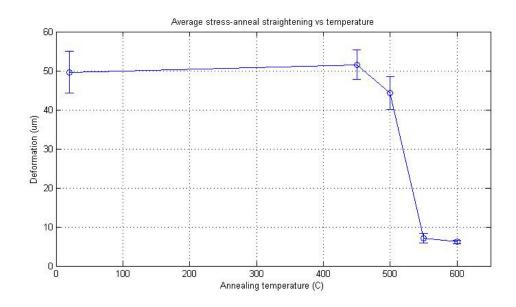

| Figure 3-10 Average deformation after stress-anneal straightening                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| Figure 3-11 Roughness measurement of bulk titanium samples before                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| lapping/polishing: a) before anneal: $R_a = 52.82$ nm; $R_t = 1.39$ µm; b) after anneal: $R_t = 1.39$ µm; b | a     |

| =55.96 nm; $R_t$ =1.31 $\mu$ m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56    |

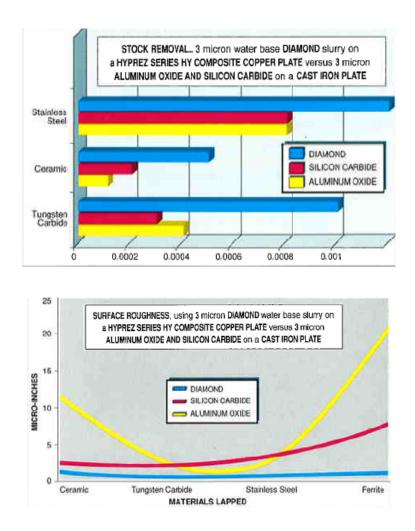

| Figure 3-12 Comparison of commonly used lapping slurries [6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 59    |

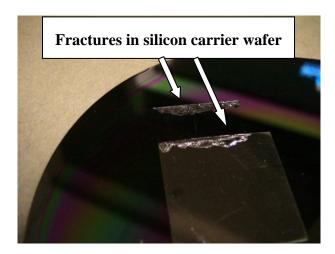

| Figure 3-13 Fractures in carrier SCS wafer due to excessive stresses in stress-an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | neal  |

| straightening process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60    |

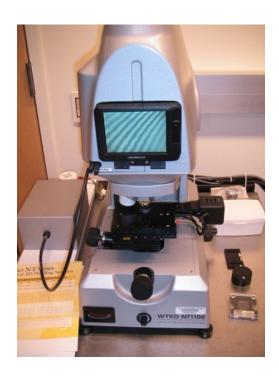

| Figure 3-14 Wyko NT1100 interferometer for roughness and deformation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 61    |

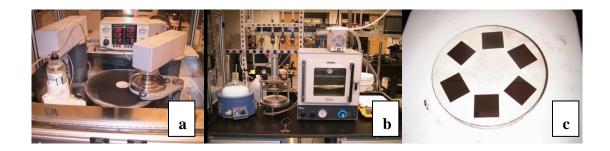

| Figure 3-15 a) Engis Hyprez computer controlled lapping/polishing machine; b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| hydraulic press and vacuum oven for bubble-free sample mounting; c) polished bu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | lk    |

| titanium samples before dismount                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62    |

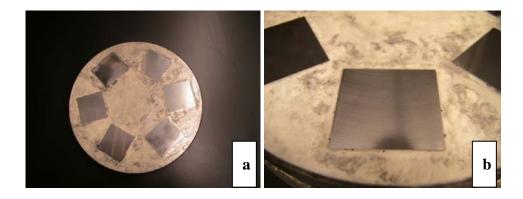

| Figure 3-16 Lapping started: a) before; b) after reaching long-range planarization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64    |

| Figure 3-17 Sample thickness variation before and after lapping on both sides       | 65     |

|-------------------------------------------------------------------------------------|--------|

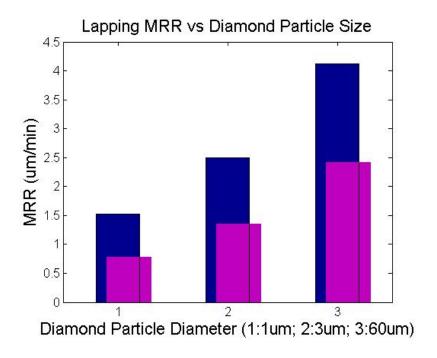

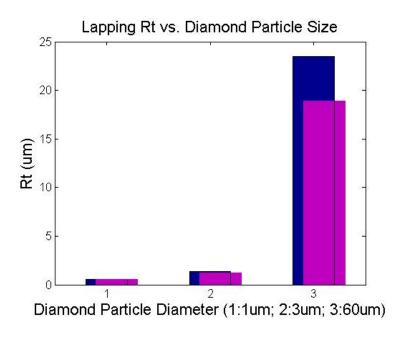

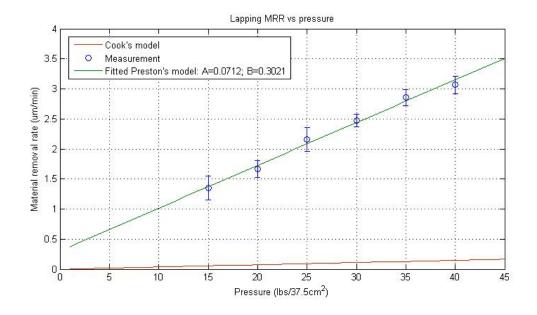

| Figure 3-18 Lapping MRR vs. diamond particle size (blue: 30 lb; purple: 15 lb)      | 66     |

| Figure 3-19 Lapping peak to valley roughness vs diamond particle diameter (blue     | e: 30  |

| lb; purple: 15 lb)                                                                  | 66     |

| Figure 3-20 Lapping average roughness vs. diamond particle size (blue: 30lb; p      | urple: |

| 15lb)                                                                               | 67     |

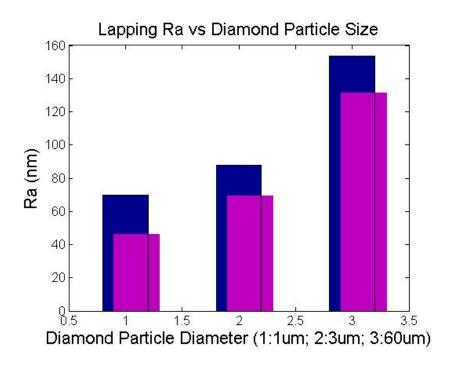

| Figure 3-21 Lapping MRR vs pressure                                                 | 67     |

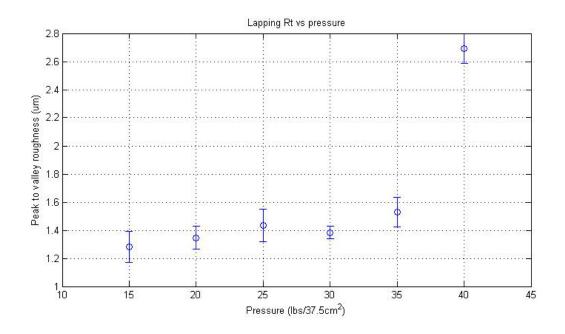

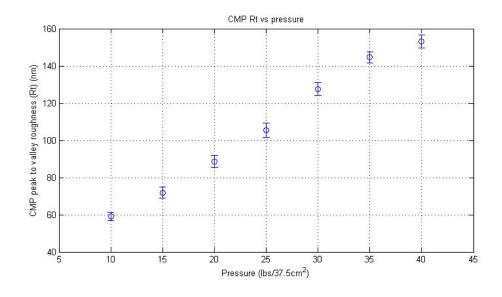

| Figure 3-22 Lapping peak to valley roughness (R <sub>t</sub> ) vs pressure          | 68     |

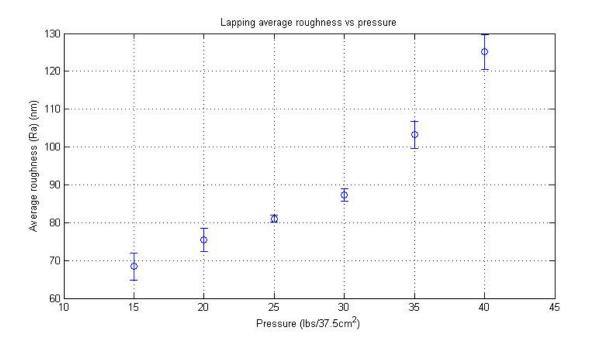

| Figure 3-23 Lapping average roughness (R <sub>a</sub> ) vs pressure                 | 68     |

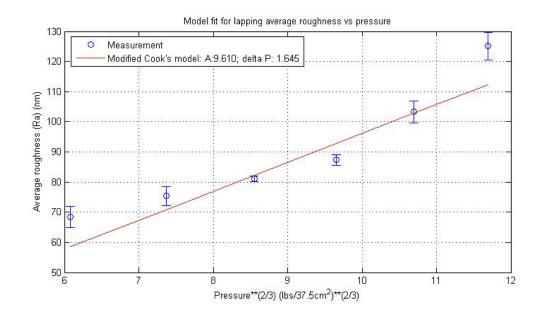

| Figure 3-24 Model fit for lapping average roughness vs pressure                     | 69     |

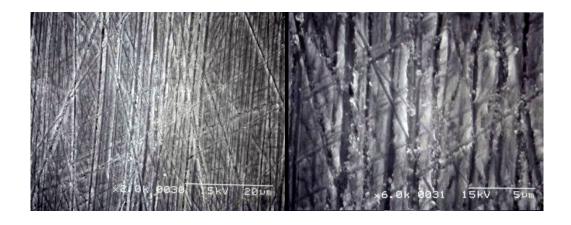

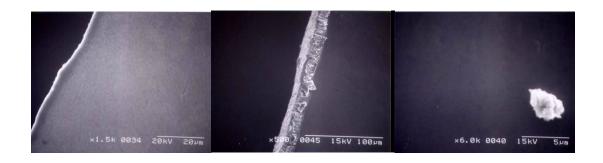

| Figure 3-25 Titanium surface after lapping process                                  | 69     |

| Figure 3-26 Compressive stress due to lapping damage                                | 71     |

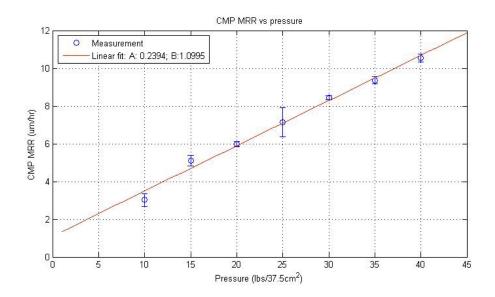

| Figure 3-27 CMP MRR vs pressure                                                     | 72     |

| Figure 3-28 CMP peak to valley roughness vs pressure                                | 72     |

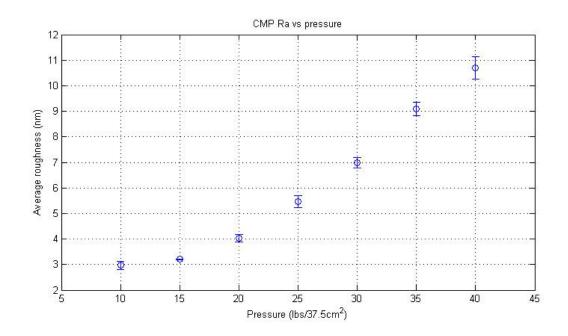

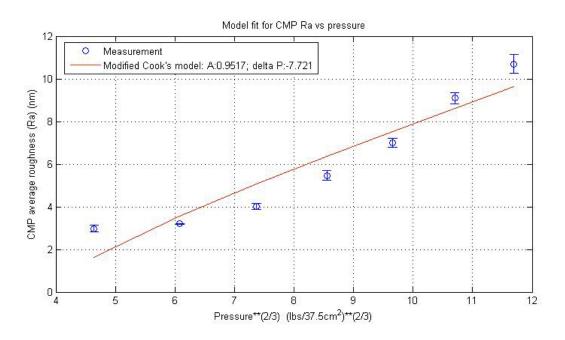

| Figure 3-29 CMP average roughness $(R_a)$ vs pressure                               | 73     |

| Figure 3-30 Model fit for CMP average roughness vs pressure                         | 73     |

| Figure 3-31 Titanium surface finish after CMP                                       | 74     |

| Figure 3-32 Residual stress due to insufficient polishing. a: concave shape showing | ng     |

| remaining damage; b: minimum curvature showing polish completion                    | 74     |

|                                                                                     |        |

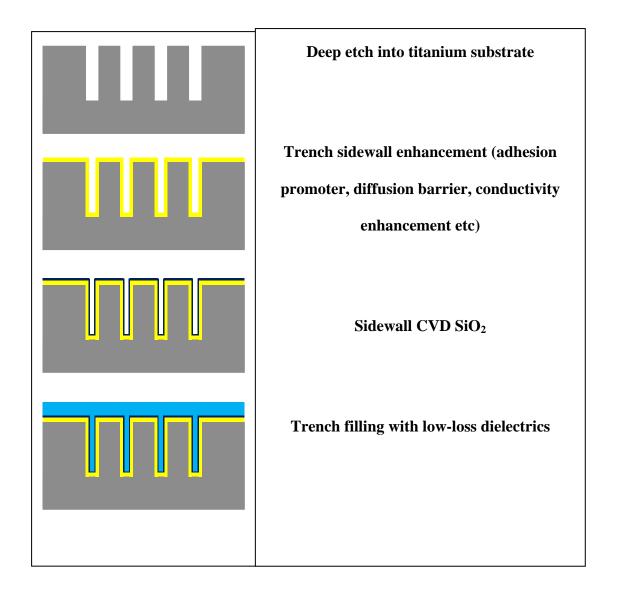

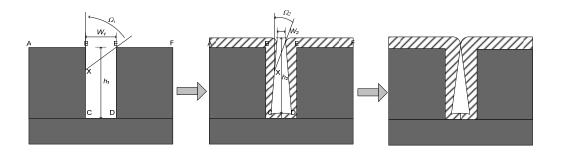

| Figure 4-1 Step I&II: Deep etch and trench-filling with low-loss dielectrics        | 78     |

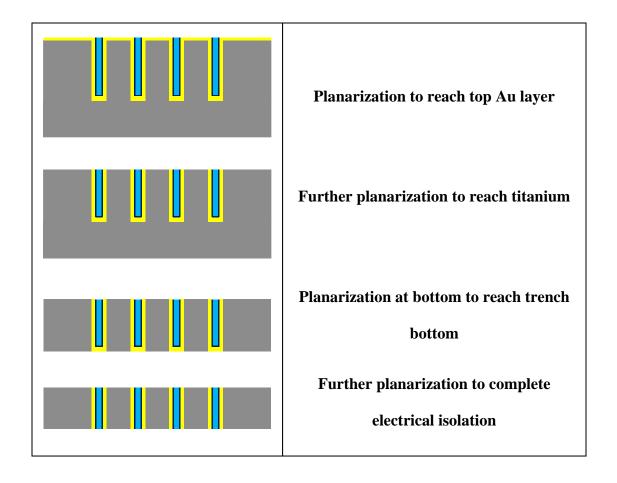

| Figure 4-2 Step III: waveguide and electrode formation through planarization        | 79     |

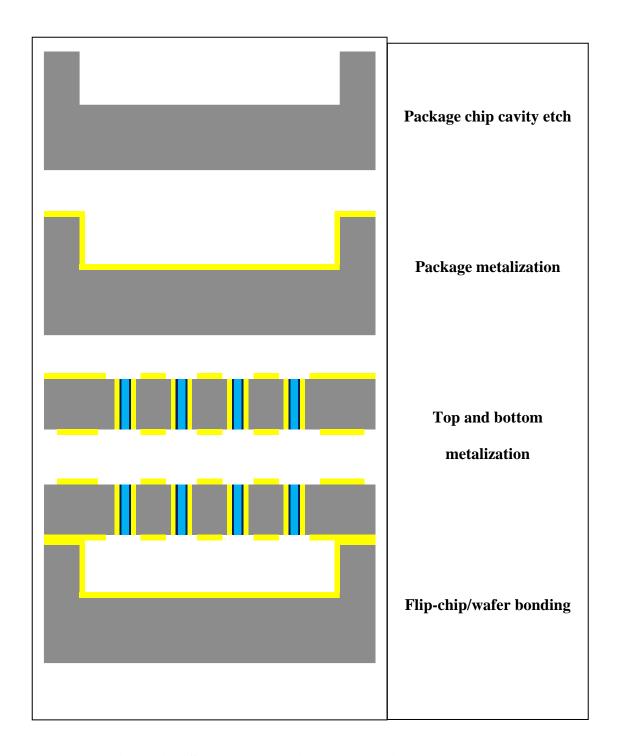

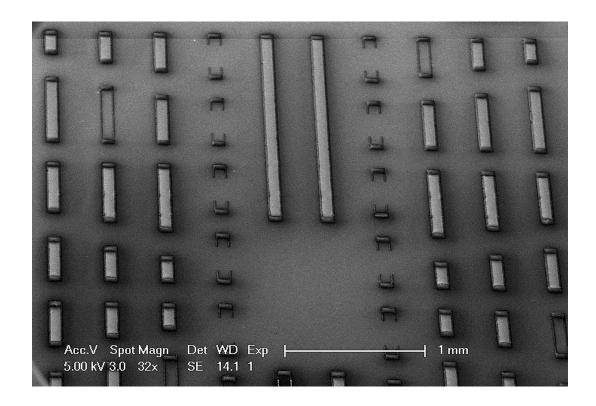

| Figure 4-3 Step IV: packaging and electrical interconnects                                 | 80    |

|--------------------------------------------------------------------------------------------|-------|

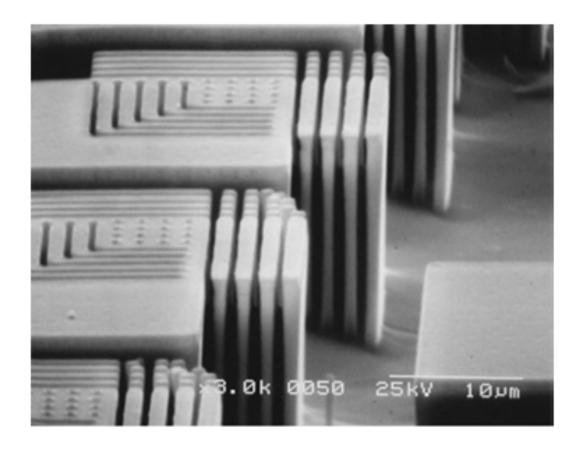

| Figure 4-4 High aspect ratio, bulk titanium structures created by the TIDE process         | s [9, |

| 10].                                                                                       | 82    |

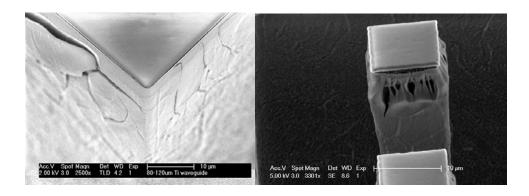

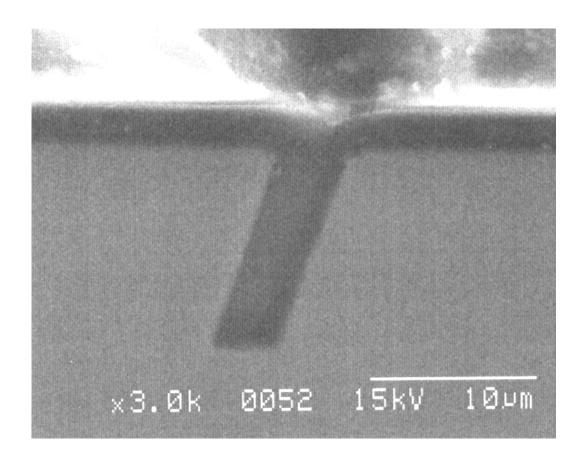

| Figure 4-5 Deep etch into bulk titanium substrate using a PECVD SiO <sub>2</sub> etch mark | 83    |

| Figure 4-6 Waveguide structure after sputtered Au sidewall enhancement                     | 87    |

| Figure 4-7 Zoomed in view of sputtered Au sidewall enhancement                             | 87    |

| Figure 4-8 Re-deposited film on trench sidewall after deep etch                            | 88    |

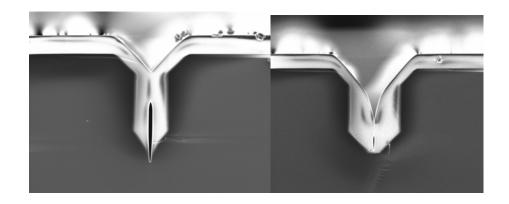

| Figure 4-9 Mechanism for CVD trench filling                                                | 91    |

| Figure 4-10 Molecular composition of TEOS                                                  | 92    |

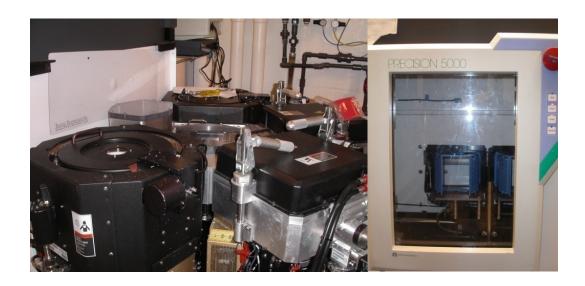

| Figure 4-11 Applied Materials PT5000 clustered deposition/etching tool                     | 93    |

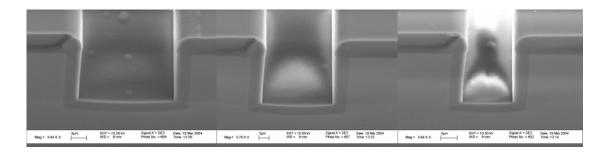

| Figure 4-12 Step coverage of PETEOS film on silicon samples                                | 94    |

| Figure 4-13 Key-hole formation in trenches with PETEOS                                     | 94    |

| Figure 4-14 Trench fill of PETEOS with alternating Ar sputtering                           | 95    |

| Figure 4-15 (DVS)-based monomer for BCB                                                    | 96    |

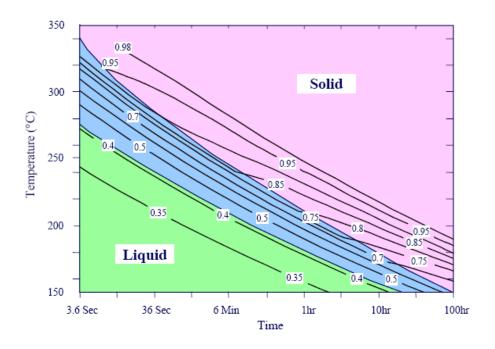

| Figure 4-16 Extend of BCB curing versus temperature and time [27]                          | 98    |

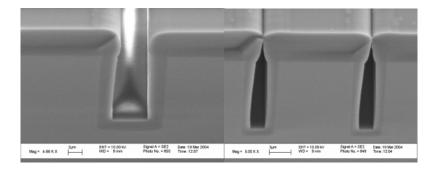

| Figure 4-17 5 $\mu$ m silicon trench (coated with 100nm sputtered Ti) filled with BCB      | 99    |

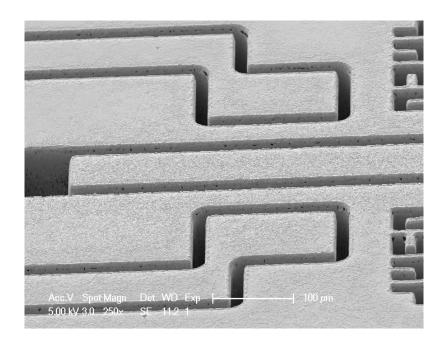

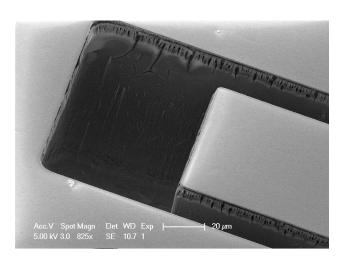

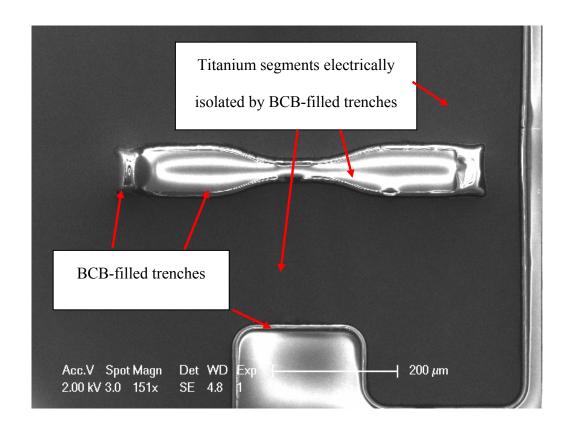

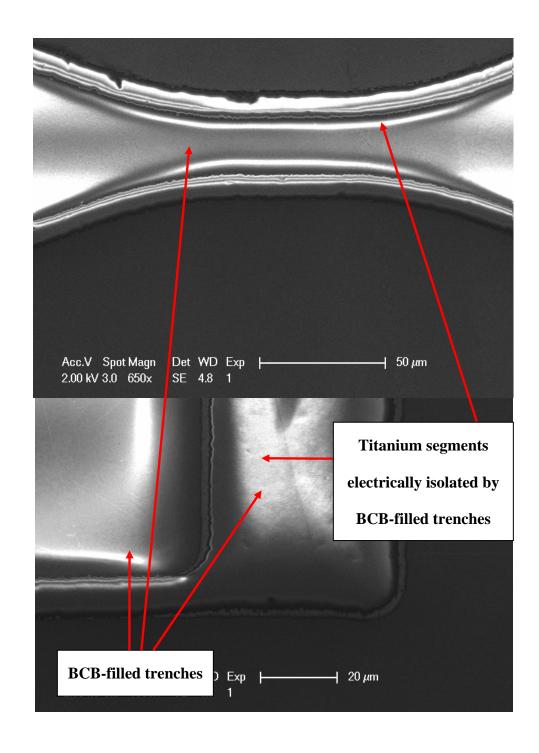

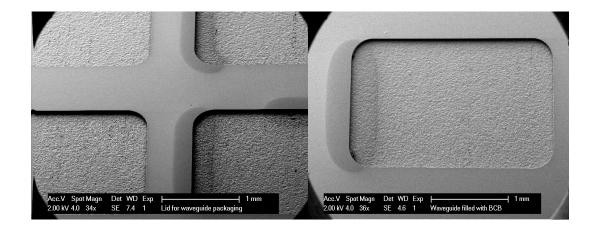

| Figure 4-18 Waveguide structures after top planarization                                   | 100   |

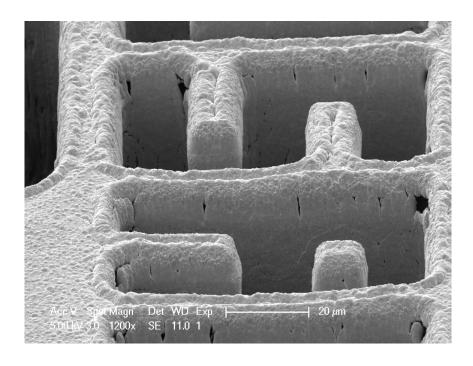

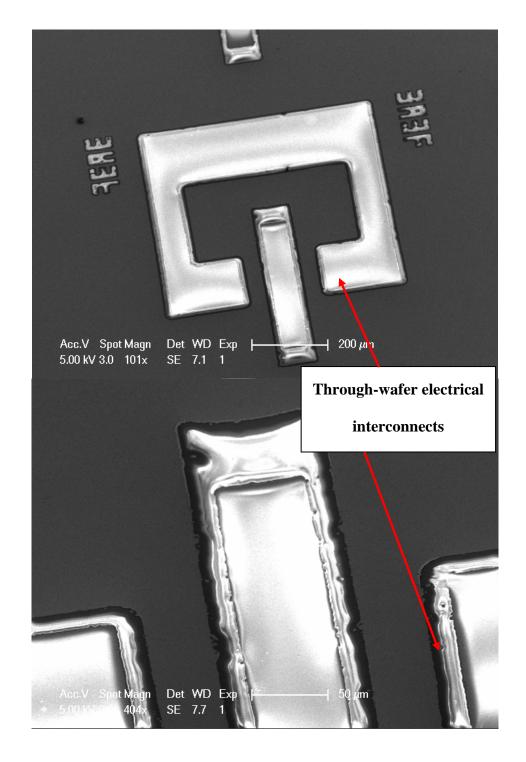

| Figure 4-19 Completed bulk titanium waveguide; Bright areas indicate charging in           | nside |

| SEM                                                                                        | 102   |

| Figure 4-20 Close-up views of completed bulk titanium waveguides                           | 103   |

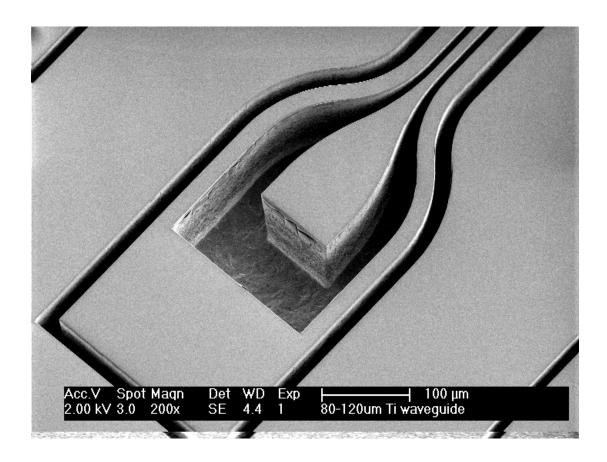

| Figure 4-21 Completed bulk titanium waveguides with through-substrate electrica            | 1     |

| interconnects                                                                              | 104   |

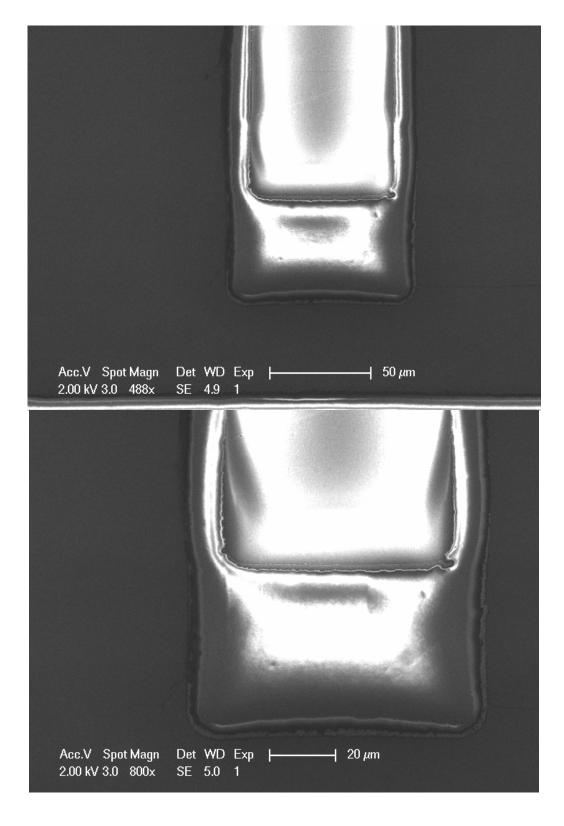

| Figure 4-22 Close-up views of trench-isolation                                             | 105   |

| Figure 4-23 Failed electrical isolation due to insufficient reverse-side planarization | n 106  |

|----------------------------------------------------------------------------------------|--------|

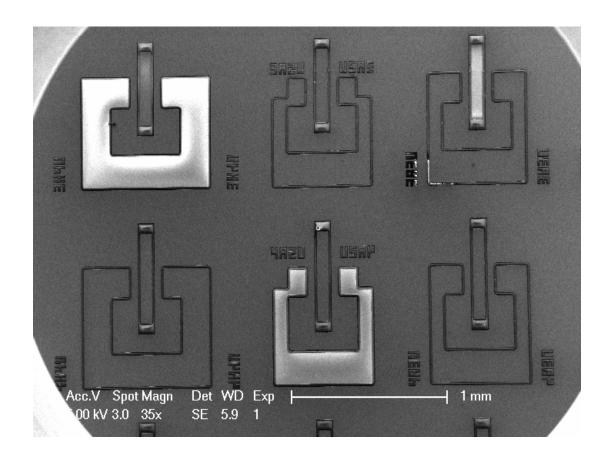

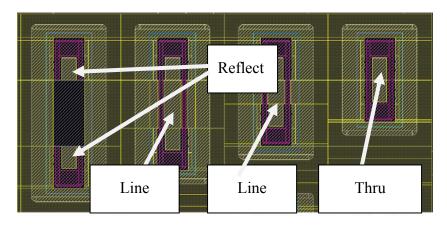

| Figure 4-24 Completed TRL calibration devices; Isolation verified electrically on      | all    |

| devices, although some devices do not charge up under SEM.                             | 107    |

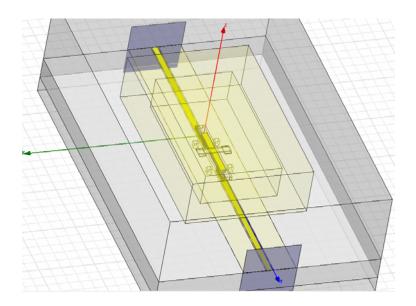

| Figure 4-25 New waveguide design with 800 $\mu$ m x 600 $\mu$ m lateral package        |        |

| dimensions                                                                             | 108    |

| Figure 4-26 Deep etched bulk titanium cavity for packaging                             | 109    |

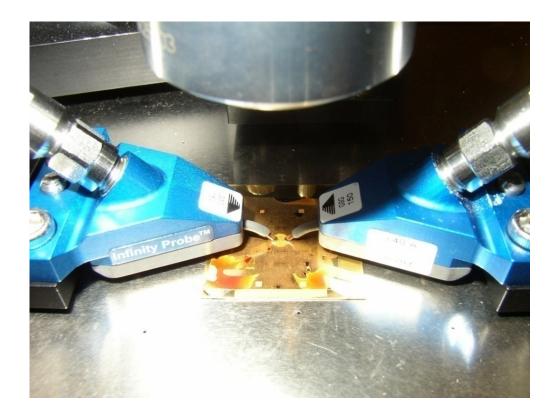

| Figure 4-27 Packaged bulk titanium sample under RF test                                | 109    |

|                                                                                        |        |

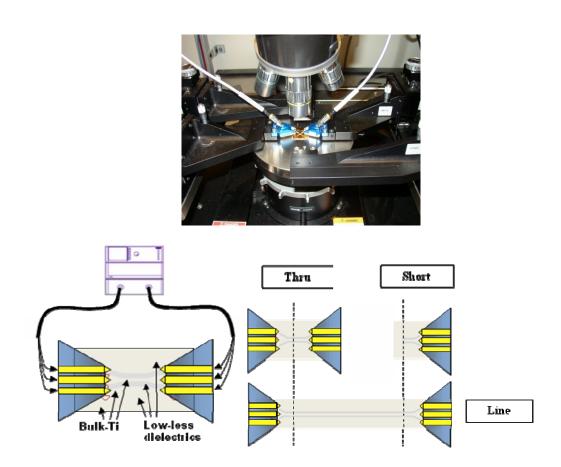

| Figure 5-1 Measurement setup for waveguide characterization                            | 113    |

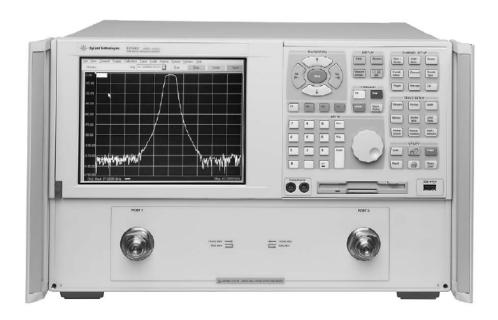

| Figure 5-2 Agilent E8363B network analyzer                                             | 114    |

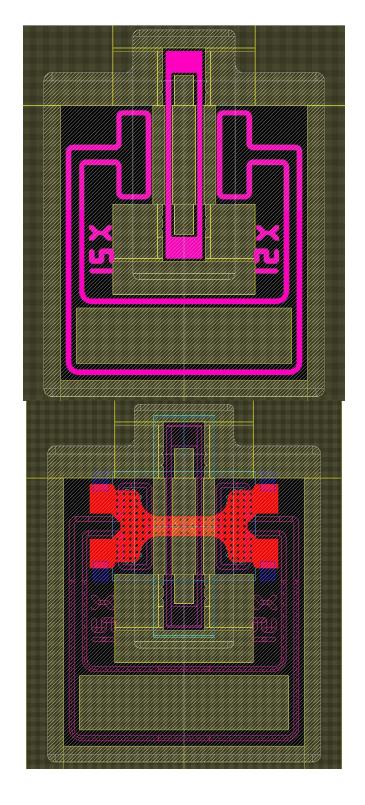

| Figure 5-3 Packaged waveguide layout                                                   | 115    |

| Figure 5-4 Cascade RF-I probe station (left) and Infinity probe (right)                | 116    |

| Figure 5-5 Design of probing area of waveguide                                         | 117    |

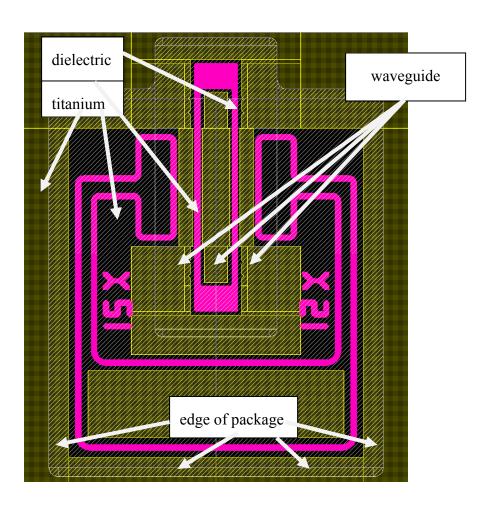

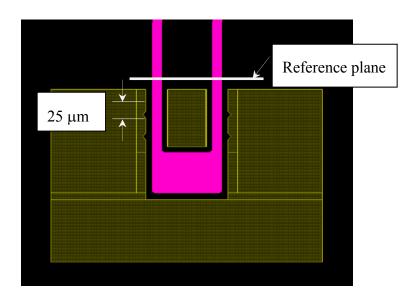

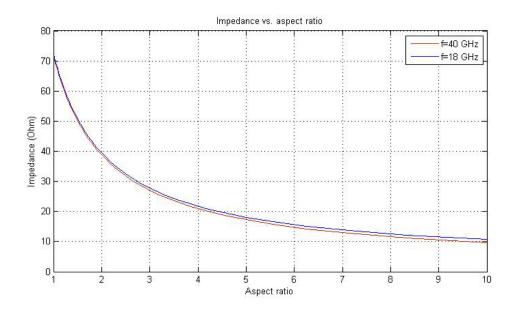

| Figure 5-6 Impedance vs. aspect ratio (h=50 $\mu$ m, W=30 $\mu$ m)                     | 118    |

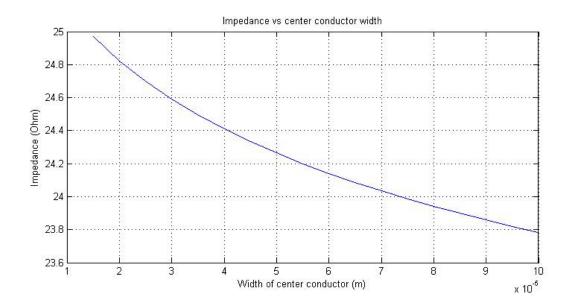

| Figure 5-7 Impedance @ 40GHz vs. center conductor width                                | 119    |

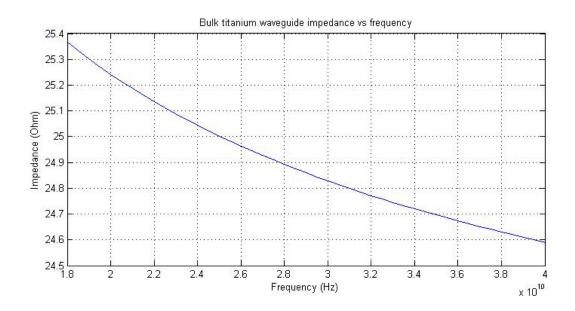

| Figure 5-8 Modeled bulk titanium waveguide impedance                                   | 120    |

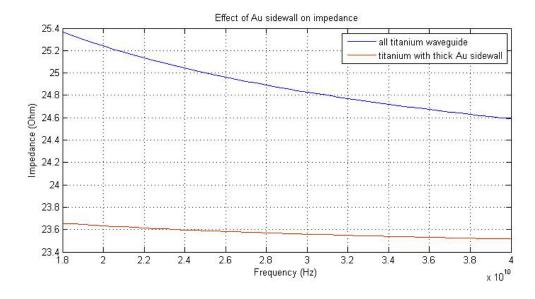

| Figure 5-9 Effect of Au sidewall on impedance                                          | 120    |

| Figure 5-10 Measurement schematic                                                      | 123    |

| Figure 5-11 Zoomed-in view of calibration standards                                    | 124    |

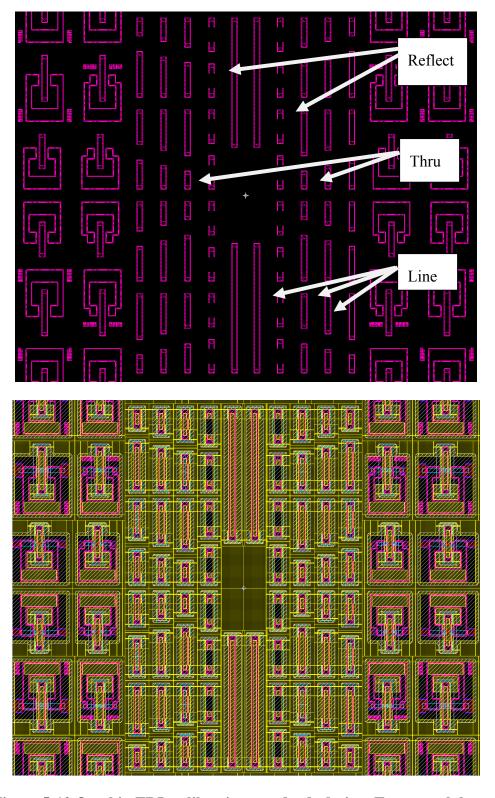

| Figure 5-12 On-chip TRL calibration standards design. Top: trench layer; bottom        | m: all |

| layers                                                                                 | 125    |

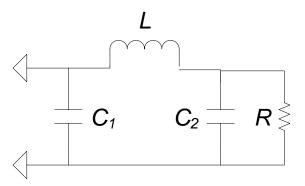

| Figure 5-13 Lumped model for calibration standards                                     | 126    |

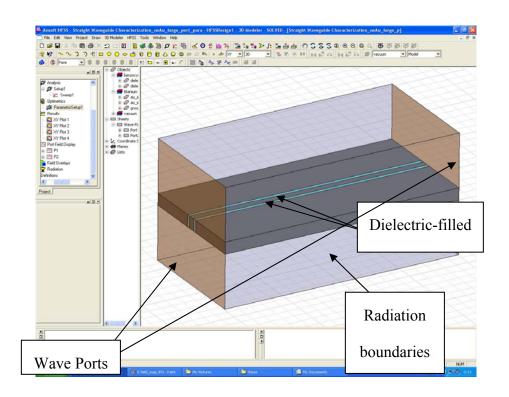

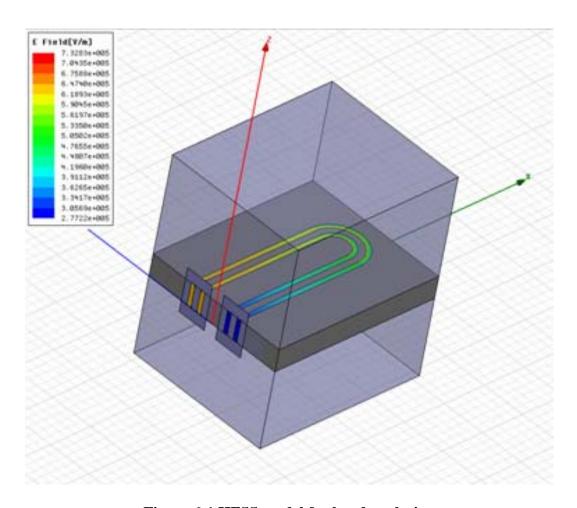

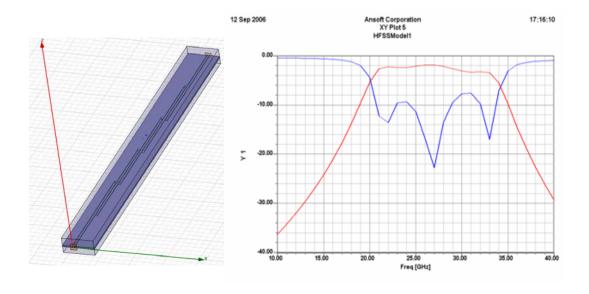

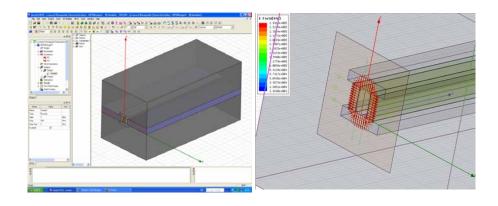

| Figure 5-14 3D model for waveguide simulations                                         | 130    |

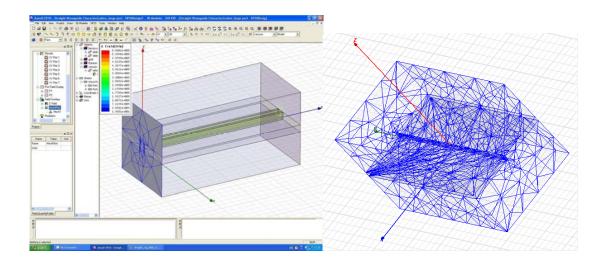

| Figure 5-15 Mesh model for bulk titanium waveguide simulation                          | 130    |

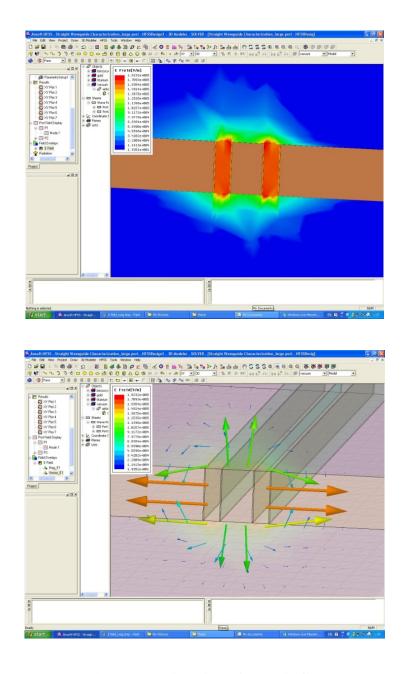

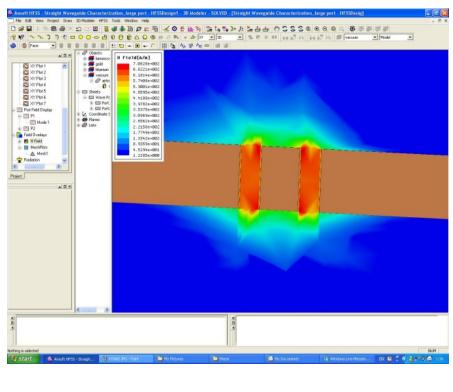

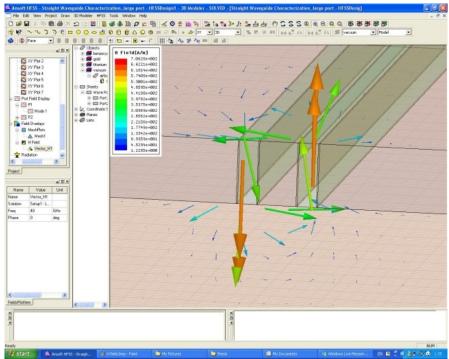

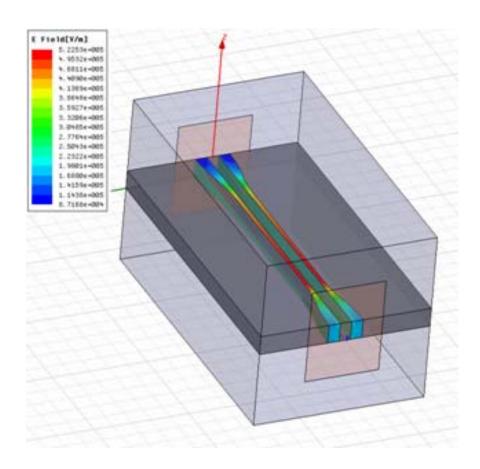

| Figure 5-16 Magnitude and direction of electric field at cross section                 | 131    |

| Figure 5-17 Magnitude and direction of magnetic field at cross section                 | 132    |

| Figure 5-18 Impedance characterization                                            | 133     |

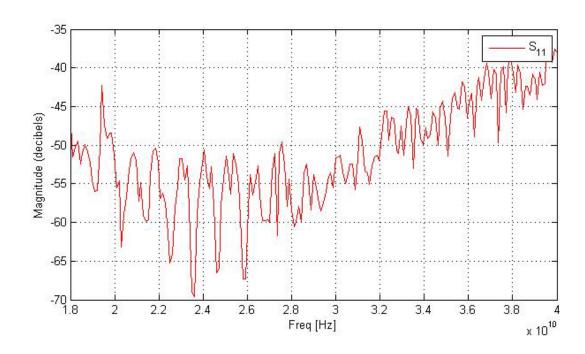

|-----------------------------------------------------------------------------------|---------|

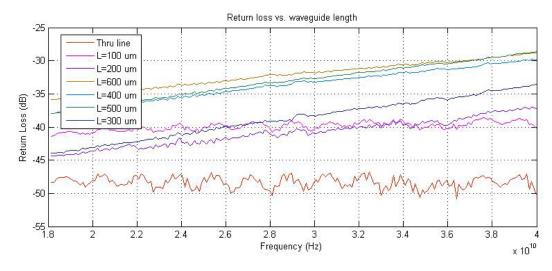

| Figure 5-19 Return loss of a packaged 400 μm waveguide                            | 135     |

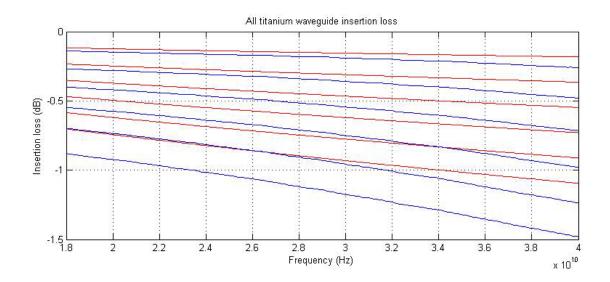

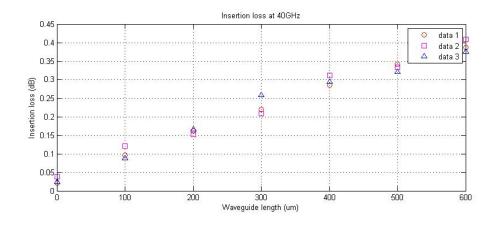

| Figure 5-20 Insertion loss of all-titanium waveguides. Red curves: theory; blue   | curves: |

| experiment. Top to bottom: 100 $\mu m$ to 600 $\mu m$ with 100 $\mu m$ increments | 136     |

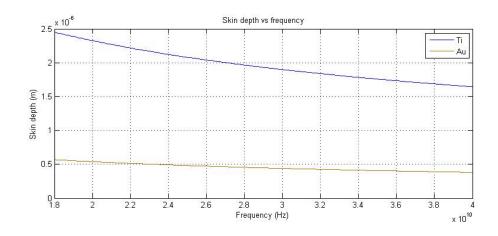

| Figure 5-21 Skin depth vs. frequency                                              | 137     |

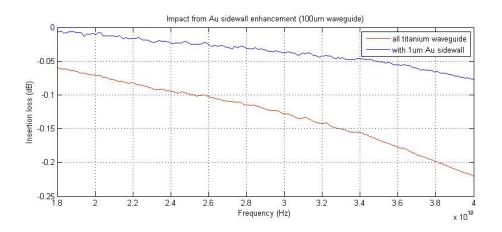

| Figure 5-22 Impact of Au sidewall enhancement on 100 μm long waveguide            | 137     |

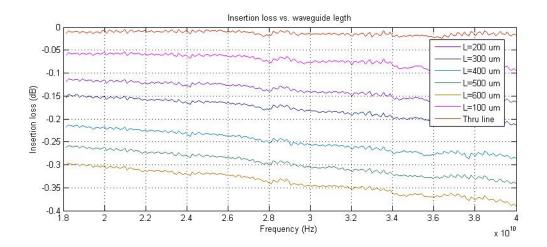

| Figure 5-23 Insertion loss vs. length for Au enhanced waveguides                  | 138     |

| Figure 5-24 Insertion loss at 40 GHz                                              | 138     |

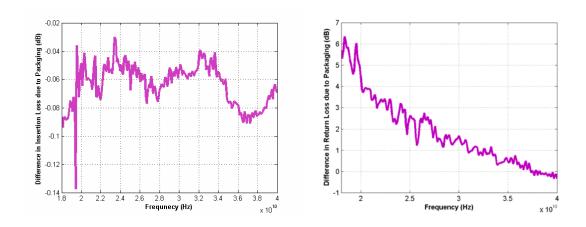

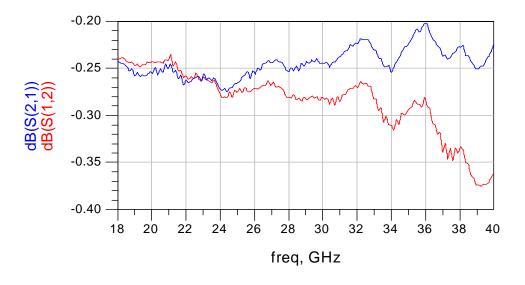

| Figure 5-25 Impact of package on loss characteristics. Left: Insertion loss;      | Right:  |

| Return loss                                                                       | 139     |

| Figure 5-26 Return loss vs. waveguide length                                      | 139     |

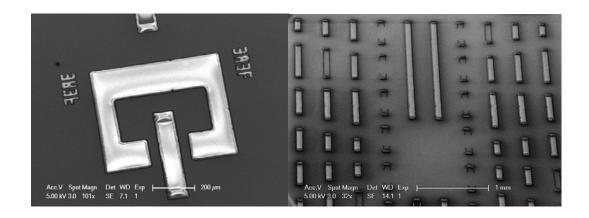

| Figure 5-27 Fabricated Bulk titanium waveguides. Left: a single waveguide         | e with  |

| electrode; Right: A set of TRL calibration devices                                | 141     |

| Figure 5-28 Cavity modes created by metal package                                 | 143     |

|                                                                                   |         |

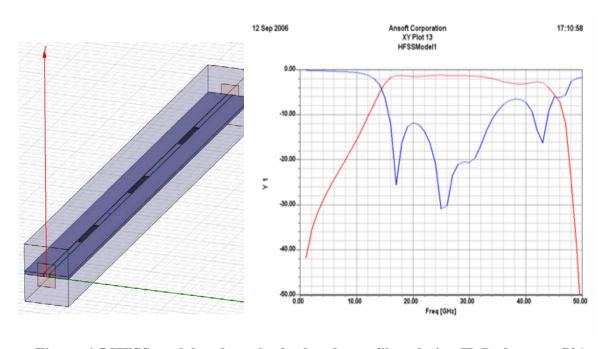

| Figure 6-1 HFSS model for bend analysis                                           | 150     |

| Figure 6-2 HFSS model for study on tapers                                         | 150     |

| Figure 6-3 HFSS model for integration of bulk titanium waveguide with tradition   | nal     |

| CPW                                                                               | 152     |

| Figure 6-4 HFSS model and results for band pass filter design I. Red curve: S21;  | blue    |

| curve: S11                                                                        | 153     |

| Figure 6-5 HFSS model and results for band pass filter design II. Red curve: S21  | ; blue  |

| curve: S11                                                                        | 154     |

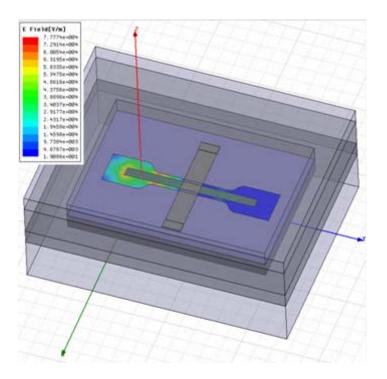

| Figure 6-6 HFSS model for shunt RF contact switch                               | 155 |

|---------------------------------------------------------------------------------|-----|

| Figure 6-7 Field leakage (reduced isolation) due to non-zero contact resistance | 156 |

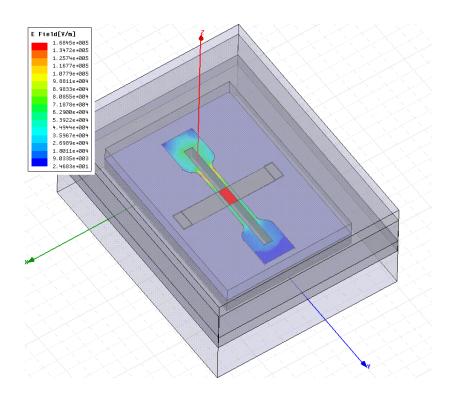

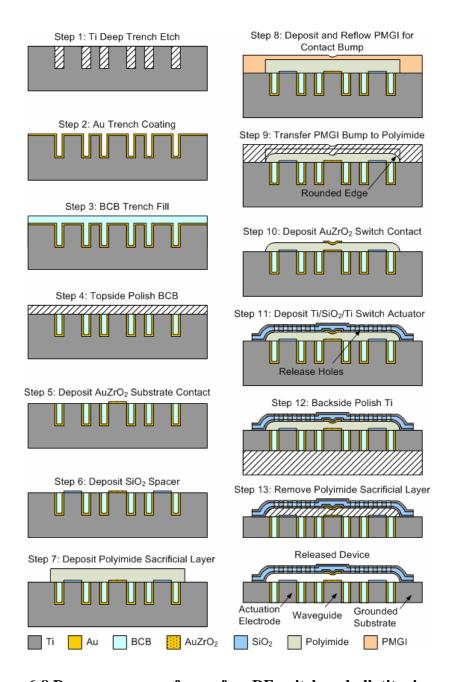

| Figure 6-8 Process sequence for surface RF switch on bulk titanium waveguide    | 157 |

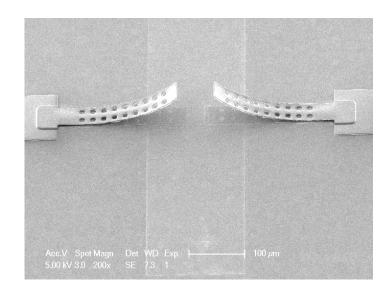

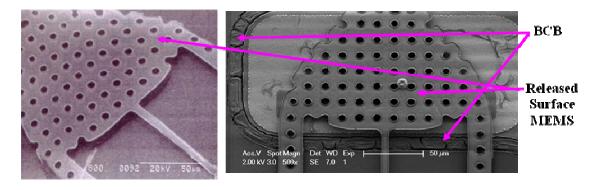

| Figure 6-9 Surface RF switch before stress-engineering                          | 158 |

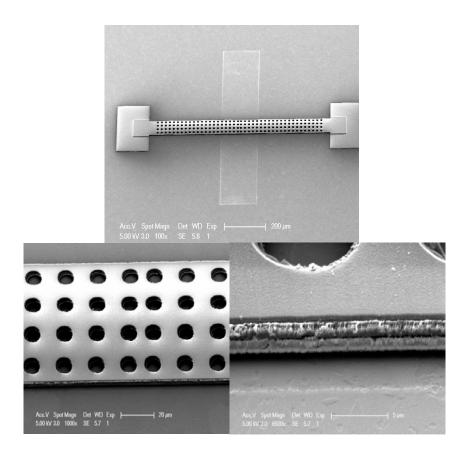

| Figure 6-10 Stress-engineered surface RF switch structure                       | 158 |

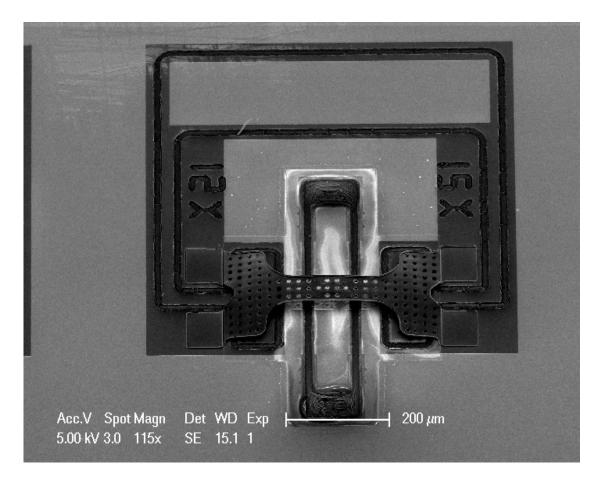

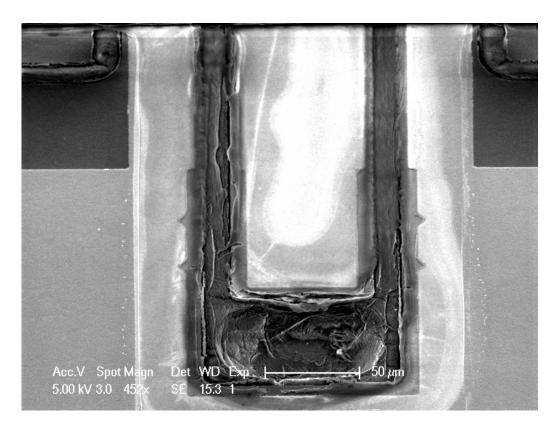

| Figure 6-11 Completed RF shunt switch on bulk titanium waveguide                | 159 |

| Figure 6-12 Completed RF shunt switch                                           | 159 |

| Figure 6-13 Residue after release etch                                          | 160 |

| Figure 6-14 Measured insertion loss of a partially released device              | 160 |

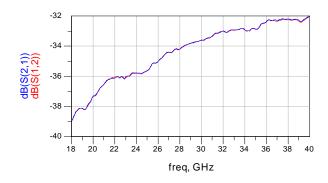

| Figure 6-15 Measured isolation of a stuck-on device                             | 161 |

| Figure 6-16 HFSS model for completely shielded waveguide                        | 161 |

|                                                                                 |     |

| Figure A-1 A uniform waveguide with an arbitrary cross section                  | 166 |

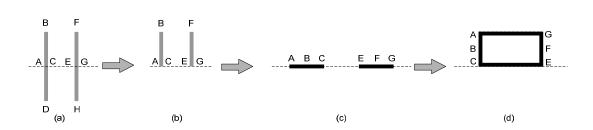

| Figure B-1 Conformal mapping of a finite parallel plate structure               | 168 |

| Figure B-2 Approximated mapping for finite parallel plate structure             | 169 |

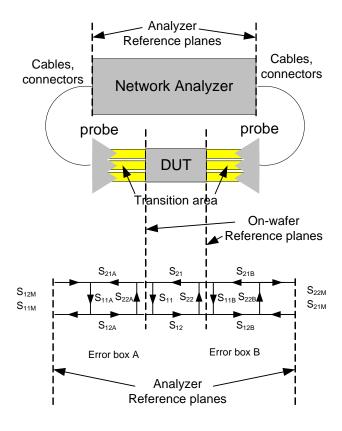

| Figure C-1 Basic model used for TRL de-embedding                                | 172 |

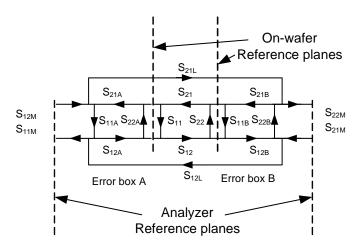

| Figure C-2 Model with leakage across DUT                                        | 173 |

| Figure C-3 Models for TRL standards                                             | 174 |

# LIST OF TABLES

| Table 1-1 | Titanium compounds vs. common MEMS materials                      | 11  |

|-----------|-------------------------------------------------------------------|-----|

| Table 3-1 | Process sequence for stress-anneal straightening of bulk titanium | 51  |

| Table 3-2 | Process sequence of bulk titanium lapping and polishing           | 63  |

| T 11 42   |                                                                   | 0.5 |

| Table 4-2 | Process parameters for deep trench etch in bulk titanium          | 85  |

| Table 4-3 | Process parameters for sidewall enhancement with Au               | 86  |

| Table 4-4 | Parameters for common uses of low-loss trench-filling dielectrics | 90  |

| Table 4-5 | Process parameters for trench-filling with BCB                    | 92  |

|           |                                                                   |     |

| Table 5-1 | Design rules for bulk titanium waveguides                         | 121 |

| Table 5-2 | Typical analysis parameters for HFSS simulation                   | 128 |

| Table 5-3 | Material properties used in HFSS simulations                      | 129 |

| Table 5-4 | Comparison between planar waveguides                              | 144 |

#### **CHAPTER 1**

#### **INTRODUCTION**

For low frequency signals, a wire, or metal trace, on a planar circuit - such as a printed circuit board - can be approximated as a lumped component with a single complex value representing its resistive and reactive properties. At higher frequencies, e.g., microwave frequencies, this approximation breaks down as the physical dimensions of these metal traces become significant relative to the wavelength of the signal [1, 2]. The metal traces now serve as transmission lines with distributed properties that can be utilized to form a myriad of devices with easily implemented changes in their geometries [3, 4].

The vast majority of high frequency, planar circuits are realized with two simple transmission line topologies: microstrip [5, 6] and coplanar waveguide (CPW) [7, 8]. Both topologies consist of thin metal traces fabricated on top of low-loss dielectric substrates.

We present a new 3D topology to microwave circuits, based on a bulk metal substrate with geometries containing dielectric-filled, high aspect ratio trenches for signal carrying. Based on newly developed microfabrication techniques in bulk titanium, the backbone of our new planar circuit platform – bulk titanium waveguide – offers the advantages of compact geometry, superior field confinement, and the capability of forming a small-footprint, high-performance RFMEMS package.

The topological comparison of the bulk titanium and conventional planar waveguides is illustrated in Figure 1-1. Instead of having a large block of dielectric as the universal carrier/substrate, the bulk titanium waveguide limits the dielectric to within the high aspect ratio trenches between segments of bulk titanium that are coplanar, therefore carrying over similar advantages to CPW over microstrip, such as

flexibility in design and ease of integration, low ground inductance, and compact size [9, 10]. Meanwhile, the deep electromagnetic wave-carrying trenches expand the wave-carrying areas from the thin metal edges, as in the case of CPW, to the entire thickness of the substrate, therefore reducing loss. Another key difference in the field distribution lies in the high aspect ratio of trenches, which confines the electric field, therefore significantly reduces losses due to radiation, cross-talk, as well as other parasitic coupling effects. With a much larger surface area to volume for signal transmission, the power handling capability is also improved compared to the conventional waveguide designs.

### 1.1 Bulk metal waveguide - concept and performance highlights

Figure 1-1 Bulk titanium waveguide compared to conventional planar circuits

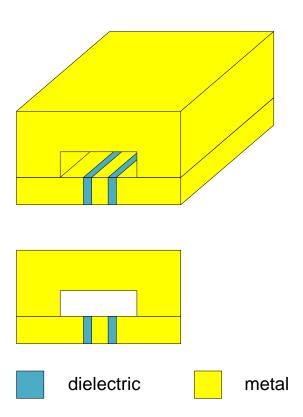

In order to expand the utility of planar circuits, and to minimize cross-talk and undesirable coupling, a package is required, forming a cavity above the waveguide, which allows for integration of other micro-components such as an IC or MEMS. Traditional approaches either feed the signal through the sides of the package,

underneath the areas where the package is integrated on the substrate, therefore generating undesirable parasitic effects, or based on drilled via holes within the insulating substrates and subsequently filling the holes with electroplated metals, thereby reducing the performance dependency on the presence of the package. For ceramic substrates, these vias are formed either by laser drilling [11, 12] or molding in the green state of the ceramic material [13]. Both approaches are restricted by the maximum aspect ratio of the vias, hence prohibiting the inclusion of a large number of interconnects within a compact package. In addition, laser drilling induces a large amount of stress; green state fabrication is limited by the lateral precision; both approaches introduce planarity issues.

Figure 1-2 Packaging for bulk titanium waveguide