A Report from the School of Electrical and Computer Engineering • Compell University

# Computer Engineering Research

in the School of Electrical and Computer Engineering

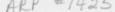

### System Architecture

Different levels of detail in the design of modern computer systems are shown in the figure, from the physical implementation of computation to the overall system architecture. This logical approach is the core of major revisions now in place in computer engineering instruction and research in the ECE School. Emphasis is placed on the various aspects of computer engineering as experiences that allow the students to progress readily from circuit design, to logic design, to computer architecture, to the eventual desired entity, whether it be solving a problem, performing a laboratory exercise, executing a design project that may lead to a physical product, or conducting thesis research.

Sketch courtesy of Rajit Manohar.

This 13th edition of Connections features the challenging research of our computer engineering research group, updates the history of computer engineering in the EE/ECE School, and considers the impact on the ECE School of revisions in the computer engineering curriculum and of new analytical and experimental techniques in the discipline. The "Positive Feedback" section contains news of recent alumni activities. Other items of interest to alumni are listed below in the table of contents. This year we have again added the "Focus for Excellence" insert for your consideration. When you return the pledge card in the insert please be sure to fill out the activities line. We want to hear what you are up to.

Simpson (Sam) Linke, editor

#### Spring 2004 In This Issue

ECE On-Line

**Eminent Professors' Fund**

| III TIIIS ISSUE                                          |        |

|----------------------------------------------------------|--------|

| Report from the Director                                 | 2      |

| Computer Engineering Education Update                    | 3      |

| Computer Operations in the ECE School                    | 4      |

| The Computer Engineering Research Group                  | 5      |

| Asynchronous Computer Architecture Research              | h 5    |

| High-Performance Microprocessor<br>Architecture Research | 7      |

| Parallel Computer Architecture Research                  | 9      |

| ECE School Research Funding                              | 10     |

| Memory System Architecture Research                      | 11     |

| A Focus for Excellence                                   | insert |

| Faculty Initiatives                                      | 13     |

| New High-Performance Computer Laboratory                 | 14     |

| Recent Faculty Accomplishments                           | 15     |

| New Staff Member                                         | 19     |

| Student Project Notes                                    | 20     |

| Enrollment and Graduation Statistics                     | 20     |

| More Tales from the Past                                 | 21     |

| Positive Feedback                                        | 23     |

# Report from the Director

ur faculty takes great pride in the courses that have defined our degree for many years.

But in a field that is as dynamic as electrical and computer engineering, the topics need to be adjusted occasionally. In the '60s we saw vacuum-tube physics dropped from the curriculum and replaced by solid-state physics. I would argue that as a result of the transistor, solid-state

physics has been defined by electrical engineering for the last 40 years. In the '70s we saw rotating machines dropped from most curricula and replaced by computers. The '80s brought fiber optics and digital technology. We became electrical and computer engineers instead of simply electrical engineers. In the '90s we learned how to connect all these computers together with networks, and created wireless phones, and the web.

Now we are in the "aughties," or whatever this decade will be labeled. We are exploring the new issues of complex systems that are no longer linear time-invariant transfer functions but complex networks that depend on economic and human interaction as much as they depend on Kirchhoff's laws. Who would have guessed that a software "virus" could bring down our communication network or a large part of our power system?

In the past year, the ECE faculty has engaged in serious discussions concerning what it means to be an electrical and computer engineer today. Preparation of a graduate for the next twenty years of his career is a daunting task. Next fall we will introduce a new sophomore course that uses the viewpoint of signal processing to teach the fundamentals of signals, including the Fourier transform. By motivating the course with examples from areas such as video compression or digital communication, we hope to give students early exposure to the excitement of our field. Course ECE 301, Signals and Systems I, will be replaced with a new junior-level course that introduces analytical and computational tools for state-space systems representations, finite-state machines, graph-theoretic approaches to network design and analysis, and examination of concepts of complexity and scalability. Next year I hope we can report on the success of this new sequence in the curriculum.

There have been many notable events within the School during this academic year. We have learned that Professor **Tom Parks**, B.E.E. '61, M.S. '64, Ph.D. '67, along with Professor James H.

McClellan of Georgia Tech, will be awarded the 2004 IEEE Jack S. Kilby Signal Processing Medal this summer. This award is a well-deserved tribute to Tom for his major contributions to an important field. The "Recent Faculty Accomplishments" feature in this issue of Connections identifies a total of 18 members of our faculty who have received various awards. I am also pleased to announce the promotion of Lang Tong to full professor, and the tenure and promotion of Amit Lal and Rajit Manohar to associate professor. Our enrollments continue to stay healthy. We have over 360 majors between the junior and senior class, plus over 100

M.Eng. students and 188 graduate students working with our faculty. Projections for future enrollments look steady.

The School is preparing a strategic plan for future development. Adjunct Professor **Peter Jessel**, B.E.E. '65, M.S. '66, has been guiding a group of faculty and students in data collection on the directions taken by other schools and leading companies. We will incorporate those data in the design of a hiring and facility plan for the next five years. Please look at our web page for updates on this program.

The construction next to Phillips Hall is almost done. Duffield Hall is nearing completion and occupation by certain research centers has begun. The atrium between Phillips and Duffield will be finished in August 2004 and will provide a spectacular place for students to meet and study during the long winter months. We have upgraded all of the classrooms along the west wall of Phillips Hall. This much-needed work is finally accomplished and students are pleased by the comfort of the new rooms.

An exciting event for the School in this academic year was the victory in the international competition last summer in San Diego by the student-run autonomous underwater vehicle project. The team, led by Professor **Kevin Kornegay**, handily won the competition against eight other teams from top schools, most of whom had oceanographic programs. Not bad for a bunch of electrical and computer engineers!

I thank you for your continued interest in the School. We are entering a time of significant change in the field, and as always would be very happy to hear from you on the state of the field and your reaction to events in the School. With very best wishes,

Clifford R. Pollock Ilda and Charles Lee Professor of Engineering Director, School of Electrical and Computer Engineering

# Computer Engineering Education Update

by Sam Linke

The growth and impact of computer engineering and technology on the School of Electrical Engineering is well documented in the spring 1992 and spring 1994 issues of *Connections*, and a detailed history of the discipline from its establishment in the School in 1950 to recent times is outlined in the summer 2001 issue of *Connections*. A direct quote from the concluding statements of the latter article states:

An examination of the advanced courses now offered in the ECE School reflects the profound influence of computer technology on the curriculum. Graduate and undergraduate students who wish to concentrate on computer engineering may choose their electives from a wide variety of available subjects and can augment their studies with appropriate courses offered by the Department of Computer Science.

At about the time that this statement was written, several newly appointed young faculty members with teaching and research interests in computer engineering examined the contents of the then current undergraduate computer engineering courses with a view toward raising the level of instruction in order to become competitive with the best programs offered at competitive institutions. As an example, the *Cornell Courses of Study 1998–99* described the four-credithour course ELE E 439 VLSI Digital System Design as follows:

Custom complementary metal-oxide semiconductor/very-large-scale-integrated (CMOS/VLSI) circuit design as seen by a circuit designer. Emphasis on structured design methodologies for digital VLSI systems. Topics include MOS transistors, design rules for MOS integrated circuits, implementation of common digital components, clocking disciplines for VLSI tools for computeraided design, system design for performance, and novel architectures for VLSI systems.

In contrast, Courses of Study 2003–04 describes the equivalent five-credit-hour course ECE 474 Digital VLSI Design (revised by Associate Professor Rajit Manohar) as follows:

Introduction to digital VLSI design. Topics include basic transistor physics, switching networks and transistors, combinational and sequential logic, latches, clocking strategies, domino logic, programmable logic arrays (PLAs), memories, physical design, floor planning, CMOS scaling, and performance and power considerations. Lecture and homework topics emphasize disciplined design, and include: CMOS logic, layout and timing; computer-aided design and analysis tools; and electrical and performance considerations. Students tape out a small project that is tested in the following semester.

Although many of the topics in both course statements are similar, the pedagogical emphasis in the revised course, and indeed in all of the newly revised courses, is to present the computer engineering courses as experiences that allow the students to progress readily from circuit design to logic design to computer architecture to the eventual desired entity, whether it be a solution or a physical product, as illustrated in the sketch on the cover of this issue.

The list of computer engineering courses offered to undergraduates who may wish to concentrate in the discipline begins with the field-required courses, ENGRD 210, Introduction to Circuits for Electrical and Computer Engineers (see Figure 1), and ENGRD 230, Introduction to Digital Logic Design, which was completely revised and updated by Assistant Professor Evan Speight, who has since left Cornell. It was taught this year by Senior Research Associate Wesley E. Swartz. Another field-required course, ECE/COM S 314, Computer Organization, was revised by Associate Professor Rajit Manohar and taught this year by Associate Professor Tony Reeves and Assistant Professor Sally McKee. A two-semester elective course, ECE 474, Digital VLSI Design, was revised by Rajit, who also taught the course during this academic year. The elective course ECE 475, Computer Architecture, was revised by Assistant Professor Martin Burtscher and former Assistant Professor Mark Heinrich and was taught in the fall 2003 semester

Figure 1. An experiment in progress in the "Super Lab"

by Assistant Professor José Martínez. A completely new elective course, ECE 473, Optimizing Compilers (formerly designated as ECE 495), was offered by Martin in the fall 2003 semester. The computer engineering group also offers senior and graduatelevel courses that include, among others, ECE 572, Parallel Computer Architecture, taught by José Martínez, ECE 574, Advanced Digital VLSI Design, taught by Rajit Manohar, and a new course, ECE 575, High-Performance Processor Architecture, developed by Assistant Professor Martin Burtscher and taught by him in the spring 2004 semester. A seminar course, ECE 697, Topics in Computer Systems, is conducted by Assistant Professor Sally McKee and staff. Influential papers from the past as well as papers that describe current research and development are discussed.

The conclusion that can be drawn from this brief survey is that computer engineering is now well established in the ECE School as a major entity that is clearly separate from computer science but continues to maintain mutual interactions with that discipline. The courses now contain much more emphasis on the hardware aspects of the technology than in the past, studies stress hardware as well as software issues and devote more attention to the application of microprocessors in system design, and the economic aspects of system complexities are of major concern. All of these factors indicate the existence of a strong computer engineering program at Cornell.

# Computer Operations in the ECE School

he mission of the computer operations department in the ECE School is to provide support for all aspects of computer activity in the School based on the use of cutting-edge computer technology. Under the direction of Robert L. Beaver, manager of computer operations, this objective is met by establishing a yearly plan that makes optimal use of current facilities and estimates future requirements in both use and acquisition of new equipment. Elements of the plan for fiscal year 2004–2005 are discussed below.

The computing equipment in ECE supported by the department is made up of Microsoft Windows and the UNIX environments Solaris, RedHat Linux, FreeBSD, Mac OS X, Suse Linux, and Fedora Linux. Other systems are available but without an official support policy for their operation. Each person in ECE-faculty, staff, or student-is allowed one username to access the various computing domains. The password for each domain may vary and must meet certain restrictions in complexity. Each person must have a Cornell NetID in order to obtain an ECE computing account and is required to sign a user policy to obtain or to keep an account. Student accounts expire at the end of each semester, but individuals have the opportunity to renew their accounts as needed. Faculty and staff are also allowed ECE e-mail accounts. Student e-mail accounts are not allowed at the present time. All aspects of the computing accounts can be managed by a visit to a specific URL.

The operations department provides daily user support related to computing and network problems or questions. Questions are handled by means of a system known as Request Tracker. While each staff member carries a cell phone and the manager has a land-line phone as well, the preferred method of communicating questions or problems is to send e-mail to a "help" address. A ticket is automatically created in the system that establishes a record of the request and allows an end user to see the status of all requests. Tickets are processed in order based on the number of people affected and in accordance with the following priority order: service outages, requests from the

ECE director, university requests, faculty requests, and student requests.

The operations department supports the Microsoft (MS) Windows operating system Windows XP Professional, with the present server environment being MS Windows 2002. Goals for this domain for this fiscal year include: upgrading the server environment to MS Windows 2003, upgrading MS Office XP to MS Office 2003, and creating installation points for all Windows software in the network. Plans are in place for the installation of a system management server (SMS), a set of tools from Microsoft that assists in managing personal computers connected to the network. SMS will enable the network manager to create an inventory of all the hardware and software on the network and store it in a database. Authentication procedure in the Microsoft domain is also scheduled to migrate to a lightweight directory access protocol (LDAP), a set of protocols for accessing information directories.

Planned upgrades for the UNIX environments include migration to LDAP authentication, installation of network servers for Linux and Solaris, arrangement of automatic operating system (OS) updates for Linux, and upgrades of the Solaris operating system to version 9.

The ECE network consists of a fiber cable backbone that can bring 100 MB to 1 GB ethernet connections to desktops in the system. During this fiscal year, migration of the fiber cable to Rhodes Hall moved everyone over to the new network infrastructure. Due to cost concerns and current lack of demand, 1 GB ethernet ports were not installed in every office but connections will be made eventually to every available terminal, and intrusion and security options and a registration management system will be established in the network. An evaluation is in progress on GB needs and plans for switch upgrades to accommodate them, and a procedure is being examined that will provide a simpler method for faculty to determine Cornell Information Technologies' (CIT) network bandwidth charges. There are also plans for faculty and staff to have access to a virtual private network (VPN) that enables the Internet to be used as a medium for the

transportation of data. Network service servers, including the domain name system (DNS), are also scheduled for an upgrade. DNS is an Internet service that translates alphabetic domain names into the more functional Internet protocol (IP) form.

The operations department supports seven academic laboratories in the ECE School, three general labs and four academic teaching labs. The general labs are the Sunlab located in Phillips 303 with 20 seats, the Windows lab in Phillips 318 with 60 seats, and the UNIX lab in Phillips 329 with 36 seats. (See page 14 of this issue for a display of the new AMD 64 equipment in this lab.) The four academic teaching labs are located in the undergraduate teaching facility located on the second floor of Phillips Hall, as described in the 1993 issue of Connections, but with updated various-model Dell PIV computers. Expansion goals for these labs for this fiscal year include migration of all computers to the ECE domain, migration of printing facilities to the quota management system in the School, and creation of a management account to facilitate maintenance and repair. Older computers from the old Phillips 329 lab will be relocated in an upgraded design lab in the facility.

Ongoing implementation of these planned upgrades of computer facilities and corresponding laboratory equipment augments the revisions in computer engineering teaching and research described in other sections of this issue, and helps to ensure the presence of a strong program in the discipline in the ECE School.

## Asynchronous Computer Architecture Research

Directed by Rajit Manohar

### The Computer Engineering Research Group

The Computer Engineering Research Group in the School of Electrical and Computer Engineering consists of Professors Rajit Manohar, Martin Burtscher, José Martínez, Sally McKee, and their graduate students. The group helped to found the Cornell Computer Systems Laboratory (CSL) that brings together faculty members with common interests from the ECE School, the Department of Computer Science, and the College of Engineering. Research in the ECE School has been augmented in recent months by receipt of major funding from several agencies. Other faculty members with interest in CSL include Assistant Professor Bradley Minch, who investigates analog and digital VLSI circuit design, and Professor Keshav Pingali of the Department of Computer Science, who has research interests in programming languages and computers for high-performance architectures. The principal research areas of the computer engineering group are described in the following four articles.

components acting in synchronism suddenly going into asynchronous mode. The generators in the affected areas pulled "outof-step" with one another, clocks went awry, and the now incorrect timing mechanisms on protective devices, together with other abnormal functions, caused the transmission grid to split apart with unpleasant results. In this large-scale electric-power domain, clocks depend upon synchronous behavior of the network. In an odd turnabout, the socalled synchronous behavior of integrated electronic circuitry is controlled by clock settings. For certain applications in computer architecture, asynchronous behavior without clocks may be a more desirable mode of operation.

A very-large-scale integrated (VLSI) system today contains hundreds of millions of transistors. These transistors all operate concurrently to perform billions of computations per second. At first glance it may seem that orchestrating the computation being performed by these transistors is an insurmountable task. Over the past few decades, however, VLSI designers have developed a number of organizational principles that enable them to design very complex systems in a systematic manner. These principles also enable them to utilize the transistors effectively, thereby providing the ever-increasing performance that we have come to expect.

One of the basic organizing principles commonly used by VLSI designers today is the notion of a periodic clock signal that coordinates system activity. A chip is partitioned into components, and each component is given a task to perform and a time budget to be determined by the clock period in which it must complete the task.

At the end of the clock period, information is communicated between components, and the components can now perform a new computation at the next clock period using information computed in previous periods. This simple idea, while being effective, can also introduce inefficiencies in design. The problem arises because the clock period is programmed to account for the slowest possible task performed by a component. Therefore, if some component finishes early, it must simply wait until the next clock period even though it might otherwise be able to perform useful work.

Since present-day technology scaling is reducing the feature sizes of the devices on a chip, we are now in a regime where the time required for communicating information, as determined by the delay along wires on a chip, is dominating the time it takes to actually compute the values being communicated! With increasing clock frequency (clock periods are now below 350 picoseconds), high-performance microprocessors can even reserve entire clock periods for simply communicating information from one point on a chip to another. Distributing a precise, periodic clock signal to different regions of a chip is also a non-trivial task.

Rajit's group is examining a class of VLSI systems that do not use clock signals for their operation. These asynchronous or clockless VLSI systems do not have some of the limitations previously outlined. The absence of a global clock signal means that the clock distribution problem doesn't exist. Since the activity of components on a chip is not synchronized to a periodic clock signal, each component can execute its task at the fastest possible rate without having to wait unnecessarily. Clockless circuits are also appealing because each component on a chip normally waits for data to arrive and can begin activation without waiting for the clock. Therefore there is no activity in components that do not participate in a particular operation, a condition that leads to a reduction in power consumption.

Elimination of the clock introduces sev-

(continued on page 6)

### Asynchronous Computer Architecture Research

(continued from page 5)

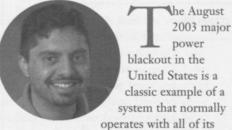

Figure 2. An asynchronous processor pipeline with tokens corresponding to instructions being processed. The tokens are indicated by color.

eral challenges that must be addressed to make these systems a reality. The functionality provided by clock synchronization that informs components of data arrival is still required and must be provided by another mechanism. The current technique makes use of the "handshake protocol," which provides both communication and synchronization functions. If a component wishes to send data to another one, it simply sends the data and waits for the receiver to signal its receipt of the information. These data items can be thought of as "tokens" that flow through computation blocks, as illustrated in Figure 2. Once confirmation has been received the component can send the next data value. There are several variations and optimizations possible, but this basic concept is used by all asynchronous VLSI systems. This additional protocol

constitutes an overhead cost introduced by eliminating the clock signal. One of the questions under examination is the determination of when the benefits of asynchrony outweigh the overhead costs.

Rajit Manohar, B.S. '94, M.S. '95, Ph.D. '98, all at the California Institute of Technology, and all in computer science, joined the ECE School as an assistant professor on August 15, 1998, and was promoted to associate professor on April 1, 2004. Rajit's research and teaching interests are in asynchronous VLSI design, computer architecture, concurrency, distributed systems, and formal methods. While at Caltech he held a National Semiconductor Corporation graduate fellowship, was a research assistant on studies of asynchronous VLSI, and as an instructor, taught a three-term graduate-level

course: Concurrency in Computation. He also served as a student volunteer for Caltech's high-school teacher training program. Rajit, a member of the Institute of Electrical Electronic Engineers and the Association for Computing Machinery, is the co-author of twenty-six refereed journal and conference articles, and is co-inventor of eleven current and pending patents. His teaching assignments include computer organization and digital design, covering aspects of both clocked and asynchronous systems. He is one of the current maintainers of MAGIC, a VLSI layout editor that is used by courses nationwide.

Rajit is one of the founders of the Computer Systems Laboratory (CSL) that brings together faculty with common interests from the School of Electrical and Computer Engineering and the Computer Science Department at Cornell. The Computer Systems area encompasses both experimental and theoretical work growing out of topics in computer architecture, operating systems and compilers, programming languages and environments, distributed systems, VLSI design, and system specification and verification. The interdisciplinary composition of the research teams is one of the strengths of the Computer Systems Lab. Rajit directs the asynchronous VLSI and architecture research group in the Computer Systems Laboratory and uses formal synthesis methods for the design of provably correct, highly concurrent, reliable, and robust asynchronous systems. Some of the recent accomplishments of his group include the design of a high-performance asynchronous field-programmable gate array (FPGA) architecture that is twenty times faster than previously published asynchronous designs, and the design of the first microprocessor optimized for sensor network applications.

# High-Performance Microprocessor Architecture Research

Directed by Martin Burtscher

An automatically controlled production line is an essential component of a modern large-scale manufacturing plant, but for proper operation each one of the many elements in the line

is dependent upon the correct behavior of every other element in the line. If the operation of just one element is interrupted or delayed, the entire line may slow down or even stall until the difficulty is corrected. In much the same way, the desired seamless operation of a central processing unit (CPU) in a present-day computer system is highly dependent upon the coordinated behavior of a multitude of components and memory elements. For example, an instruction might load a value from the memory and that value activates the next step in the program. If the instruction is delayed, the entire program may be delayed with adverse economic consequences. To alleviate the high cost of such slow main-memory accesses, computer architects have proposed various speculation mechanisms, including a procedure known as load-value prediction. A load-value predictor guesses the result of load instructions, thus allowing dependent instructions to perform their tasks without having to wait for the memory access to complete its function. Unfortunately, costly mispredictions hinder the true potential of load-value prediction. Current microprocessor architecture research at the Cornell Computer Systems Laboratory (CSL) is concerned with building more accurate and faster load-value predictors with little or no extra hardware required.

Accesses to memory, especially loading information from memory, can degrade the performance of a processor in two ways. First, due to advances in the design of CPUs and the lag in corresponding improvement in memory speeds, memory accesses are slow and are becoming slower.

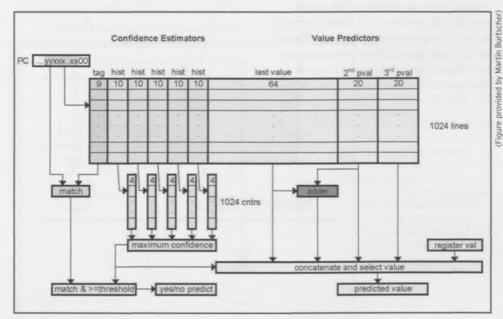

Second, memory reads limit the available instruction-level parallelism because instructions based on the result of a load will stall until the memory access is complete, thereby potentially lengthening the critical path of a program. Load-value prediction addresses both problems by predicting the value of a load instruction. Dependent instructions can immediately consume the predicted value and are thus able to execute their assignments concurrently with the memory access. If the predicted value is incorrect, the speculation hardware must perform potentially expensive recovery actions. Consequently, load-value predictors are effective only if the benefit of the correct predictions outweighs the penalty incurred by the incorrect predictions. Prior work has proposed and evaluated a number of load-value predictors. The most sophisticated predictors are hybrids that consist of multiple component predictors and incorporate confidence estimators (see Figure 3). Confidence estimators dynamically decide which loads are worth predicting and filter out loads that are likely to result in a misprediction. Avoiding mispredictions is crucial because mispredicted loads cause recovery actions

that slow down the processor. Recent research at CSL has investigated novel approaches to building more accurate and faster predictors, to reducing the size of predictors without degrading their performance, to improving the prediction coverage, and to reducing the predictors' power consumption. The following list summarizes some of the contributions of that work.

Compiler optimizations: Some load instructions are inherently unpredictable while others are unimportant because they do not affect the execution speed of a program. The CSL group has devised the first compiler optimizations to support value-prediction hardware by flagging such loads so that they do not have to be predicted at runtime. Skipping these loads lowers the predictors' power consumption and improves the overall performance because, relatively speaking, more hardware is available to predict the important loads.

Type-based optimizations: Most CPUs support several different load instructions. Some load floating-point values, others characters, and yet others large integer values. The group has been able to improve

(continued on page 8)

Figure 3. A hybrid load-value predictor with confidence estimators.

### High-Performance Microprocessor Architecture Research

(continued from page 7)

value predictors by taking advantage of information of this type, thereby allowing, for instance, detection and avoidance of aliasing in predictor tables. Moreover, loads of different types can be guided to different predictors, each of which is optimized for its type. Both techniques improve the prediction accuracy and reduce the power consumption. In addition, the latter technique reduces the predictor size because the table for character loads, for example, can be designed to be much smaller than that for floating-point loads.

Low-power hybrids: Not all load instructions prefer the same predictor, even among loads of the same type. For example, a 64-bit integer load could fetch a pointer from memory or the length of a vector, two very different values. Hence, it is necessary to combine the strengths of different predictors for best performance, as is done in hybrid predictors. Conventional hybrids use hardware to figure out which component predictor to use by running all components in parallel to detect which one is the best for a given load. This technique not only consumes considerable power but also increases the hybrid's size because each component has to be large enough to handle all loads. The group proposed profile-based and other approaches to determine which component should predict which loads. Doing so not only simplifies the hybrids' hardware but also reduces the power consumption because only one component is active at a time. Furthermore, the hybrid can be sized much smaller because no component needs to be large enough to handle all loads. This, in turn, means that the hybrid can be accessed faster, i.e., it provides its predictions sooner.

Self-optimizing, adaptive hardware: Predictor hardware is very general because it should improve the performance of every conceivable program. However, the speed of some programs may be increased substantially by a different predictor configuration. Moreover, programs go through phases, not all of which prefer the same configuration. Fixed predictor implementations cannot exploit these variations between programs and within programs. The CSL group is the first to devise selfoptimizing predictors that reconfigure themselves on the fly to optimize the performance to the current program behavior. This technique outperforms all previously proposed schemes.

Superspeculation: Microprocessors fetch instructions in sequential program order, which unfortunately is not ideal for fast execution. That is why high-end CPUs internally reorder the instructions and execute them in data-flow order, that is, in the order in which the input operands of instructions become available. In the presence of value prediction, potentially all inputs are always available, making data-flow order suboptimal. Current investigations are concerned with a completely novel microprocessor core in which instructions are executed in confidence

order, i.e., the instructions whose input operands are the most likely to be correct are executed first. Preliminary results show that such a core is able to deliver never before seen single-program performance.

Martin Burtscher, B.S. '94 (Swiss Federal Institute of Technology (ETH) Zurich), M.S. '96 (Swiss Federal Institute of Technology (ETH) Zurich), Ph.D. '00 (University of Colorado at Boulder), all in computer science, joined the ECE School faculty in July 2000 as an assistant professor. From 1998 to 1999, during his doctoral studies, he first served as head teaching assistant and then as instructor in Data Structures and Algorithms at the University of Colorado at Boulder in the Department of Computer Science. Martin teaches in the area of computer systems and directs his research toward high-performance microprocessor architecture, instruction-level parallelism, and compiler optimizations. Today's high-end, high-speed processors spend a lot of time waiting for memory. Predicting what will have to be done next allows them to execute useful instructions during these idle periods, which can significantly improve their performance. An important focus of Martin's recent research is the design, evaluation, and improvement of predictors to perform this function. He is a member of the IEEE and its Computer Society, the Association for Computing Machinery (ACM), and is the author of eleven refereed journal and conference articles in his fields of interest.

# Parallel Computer Architecture Research

Directed by José F. Martínez

with careful attention to timing and signals, complete awareness of the position of each player, clear understanding of each individual's required task, and rapid deployment of counter moves to block actions by the opposing team, the whole synchronized to proceed smoothly to the desired end. While observers of the game may find the successful execution of such a play to be spontaneous, the reality lies in the "architecture" of the play devised by the coaches and in the training of the players. In much the same way, computer architecture, the study of the components that make up computer systems and how they are interconnected, is applied to the construction of software and hardware to produce the huge variety of computer applications of today.

When many computer elements are to be operated in parallel, successful application of the architecture is highly dependent upon proper synchronization of all of the "threads" in a given computer code, where the threads are units of concurrent execution composed of abstract data with instructions to initialize and run them. Programmers achieve synchronization by means of typical operations based on condition codes known as flags, execution barriers, and locks, together with determinations as to whether code sections will be in a race-free situation that may prevent unpredictable results due to multiple-access conditions. It is possible to program the elements of a system to avoid ambiguous operation, but the cost is generally prohibitive. A procedure that involves conservative placement of synchronization operations degrades performance due to unnecessary stalling of the threads. An alternative approach takes an optimistic viewpoint that allows recovery from mistakes as they occur. This new strategy, known as thread-level speculation (TLS), is supported

by appropriate hardware that allows threads to speculatively execute their tasks to avoid barriers, busy locks, and unset flags, thereby achieving satisfactory performance.

The following discussion of TLS is a paraphrase of a December 2003 paper by José F. Martínez and Josep Torrellas, "Speculative Synchronization: Programmability and Performance for Parallel Codes," that has been selected to appear in IEEE Micro Top Picks from Computer Architecture Conferences:

Recent research in thread-level speculation (TLS) has produced results that describe a mechanism for optimistic execution of unanalyzable serial code in parallel. The TLS procedure extracts threads from a serial program and submits them for speculative execution in parallel with a safe thread. The goal is to extract parallelism from the code. Under TLS, special hardware checks for cross-thread dependence violations at runtime and forces offending speculative threads to squash and restart on the fly. At least one safe thread exists at all times. While speculative threads venture into unsafe program sections, the safe thread executes code without speculation. Consequently, even if all the speculative work is useless, the safe thread still guarantees that execution moves forward.

Speculative synchronization applies the philosophy behind TLS to explicitly

parallel applications. Speculative execution allows application threads to move past active barriers, busy locks, and unset flags instead of waiting. A speculative thread uses its processor's caches to buffer speculatively accessed data, which cannot be displaced to main memory until the thread becomes safe. The hardware looks for conflicting accesses—accesses from two threads to the same location—that include at least one write operation and are not explicitly synchronized. If two conflicting accesses cause a dependency violation, the hardware rolls the offending speculative thread back to the synchronization point and restarts it in flight.

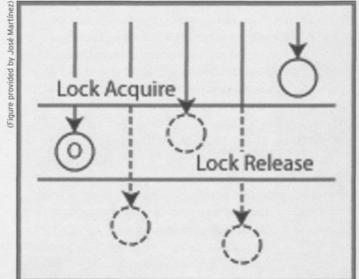

The TLS principle of always keeping one or more safe threads is the key to speculative synchronization (see Figure 4). In any speculative barrier, lock, or flag, safe threads guarantee forward progress at all timeseven in the presence of access conflicts and insufficient cache space for speculative data. Two characteristics set speculative synchronization apart from lock-free optimistic synchronization schemes with similar hardware simplicity: always keeping a safe thread, and providing unified support for speculative locks, barriers, and flags. The complexity of the speculative synchronization hardware is modest—one bit per cache line and some simple logic in the caches—plus support

(continued on page 10)

Figure 4. An example of a critical section protected by a speculative lock. Solid and dashed lines represent safe and speculative threads, respectively. Lock owner (labeled O) and three speculative threads concurrently access the critical section. In a conventional lock, only the lock owner would be allowed access. A fifth thread has not yet reached the critical section and remains safe.

### Parallel Computer Architecture Research

(continued from page 9)

for checkpointing the architectural registers. Moreover, by retargeting high-level synchronization constructs to use this hardware, speculative synchronization becomes transparent to application programmers and parallel-forming compilers. Finally, conventional synchronization is compatible with speculative synchronization. In fact, the two can coexist at runtime, even for the same synchronization variables. When a set of five compiler and hand-parallelized applications was evaluated for speculative synchronization, the time lost to synchronization was found to be reduced by 34 percent on average.

José F. Martínez, B.S. '96 (Universidad Politénica de Valencia, Spain), computer science and engineering, M.S. '99, Ph.D. '02 (University of Illinois at Urbana-Champaign), both in computer science, joined the ECE faculty on August 15, 2002, as an assistant professor. He is a two-time recipient of the Spanish government's prestigious national award for academic excellence

and was a Bank of Spain graduate fellow for four years. In 1998 he was inducted into the Phi Kappa Phi Honor Society for outstanding academic performance. In the ECE School, Professor Martínez is currently teaching computer architecture, parallel computer architecture, and topics in multithreaded and multiprocessor architectures. José is author or coauthor of a number of publications that have been presented in international conferences and symposia on computer architecture, such as Architectural Support for Programming Languages and Operating Systems (ASPLOS), International Symposium on Computer Architecture (ISCA), and the Annual International Symposium on Microarchitecture (MICRO). He is a member of the Association for Computing Machinery and the IEEE Computer Society.

As a member of the Cornell Computer Systems Laboratory (CSL), Professor Martínez's research interests include but are not limited to multithreaded and multiprocessor architectures for high performance and programmability, microarchitecture, and hardware-software interaction. His current research is concerned with speculative shared-memory architectures. The previously discussed TLS procedure has emerged as a promising architectural technology to boost the performance of difficult-to-analyze codes. José has proposed two main contributions of his work to TLS. In the first case a scalable multiprocessor architecture is based on a hierarchical approach that uses largely unmodified speculative chip-multiprocessors (CMPs) as building blocks. In the second case, an application of TLS is used to overcome conservatively placed synchronization in parallel codes. The proposed hardware solutions are quite simple, require no programming effort, and yield performance improvements that are very promising.

#### ECE SCHOOL RESEARCH FUNDING

Total research funds expended in 2000-2001 \$15,263,499

Total research funds for 2001-2002 \$14,435,044

Percent decrease 5.4%

Total research funds expended in 2002-2003 \$16,321,630

Percent increase 13.1%

The 2001–2002 research expenditure decreased since 2000–2001 because the school changed the reporting structure for calculation of expended research funds. During the past academic year the school has received gifts and equipment valued at over \$4.5 M in support of faculty research, teaching, and special projects. In addition to the National Science Foundation and the Office of Naval Research, some of these sponsors include Sensor Systems, Advanced Micro Devices, BAE Systems, BF Goodrich, Emcore, Fuji Electric, General Electric, GTE/Verizon, Lutron Corporation, IBM, Intel, Microsoft Corporation, Northrup Grumman, Nova Crystals, NxtWave, Rockwell Scientific, RF Micro Devices, Triquent, Tiawan Power, and Zepton Networks. These generous grants from foundations and corporations, coupled with equally commendable gifts from many individuals, aid the recipients in their teaching and research and make it possible for the ECE School to establish and maintain a leading edge in the discipline.

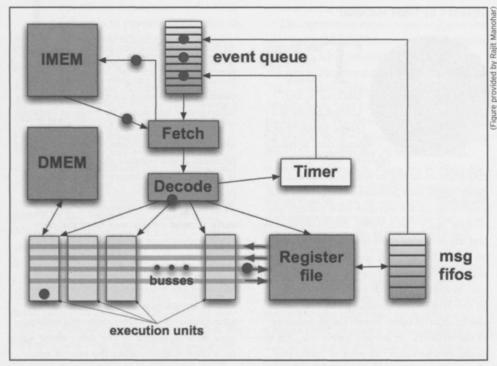

# Memory System Architecture Research

Directed by Sally A. McKee

For many years highway transportation in this country has been hampered by the inability of highway construction to keep up with the growing

number of automobiles. Introduction of a new superhighway is soon followed by the familiar crowded traffic conditions. This unhappy condition has a direct parallel in computer system development where the rate of improvement in microprocessor speed is exceeding the rate of improvement in memory speed. Indeed, the projected eventual decline in improvement of computer system performance as a result of this bottleneck has become known as "the memory wall." Memory system architecture research attempts resolution of this dilemma by improving dynamic random access memory (DRAM) utilization (see Figure 5), increasing efficiency of highspeed memory storage mechanisms (caches) and decreasing periods of time during which one component in a system is waiting for another component to complete its function (latencies), and by exploiting parallelism at multiple levels, e.g., overlapping memory activity with central processing unit (CPU) activity or allowing more memory requests to be serviced at the same

Microprocessor speed is increasing much faster than memory system speed: Since 1987, the microprocessor performance has improved at an average rate of 55 percent per year; in contrast, DRAM latencies have improved by only 7 percent per year, and DRAM bandwidths by only 15-20 percent per year. The result is that the relative performance impact of memory accesses continues to grow. In addition, as instruction issue rates increase, the demand for memory bandwidth grows at least proportionately, possibly even superlinearly. Many important applications, e.g., sparse matrix, large-scale scientific computing problems, and database and computer-aided design (CAD) applications, do not exhibit sufficient locality of reference to make effective

use of the on-chip cache hierarchy. For such applications, the growing processor/memory performance gap makes it more and more difficult to effectively exploit the tremendous processing power of modern microprocessors. Applications that suffer most are characterized by complex data structures, large working sets, and access patterns with poor memory reference locality. Examples of such codes can be found in myriad domains where memory stalls can account for the majority of the execution time of applications. Worse, the stall contribution as a fraction of total execution time increases as the performance gap between processors and memory continues to grow. Reduction of this memory stall time improves processor resource utilization, and will allow an application's performance to scale with improvements in process speed and technology.

The traditional approach to attacking the memory system bottleneck has been to build deeper and more complex cache hierarchies. Although caching works well for programs or parts of programs that exhibit high locality, many important commercial and scientific workloads lack the locality of reference that makes caching effective. Industry researchers report that memory bus and DRAM latencies cause processors to be idle up to 65 percent of the time on commercial database workloads, that the efficiency of current caching techniques is generally less than 20 percent of an optimal cache's, and that cache sizes are up to 2000 times larger than the size of an optimal cache. Although more recent computer architecture has produced better latency-tolerating mechanisms, the larger number of instructions in flight can also put more pressure on the memory system, depending on the characteristics of the application. No matter how hard we push it, traditional caching cannot bridge the growing processor-memory performance gap. A promising partial solution is based on the use of memory controllers.

Within the past six years, Professor McKee and her colleague Professor John Carter of the University of Utah, have attacked the memory problem with a unique approach to the memory controller-a

general-purpose, uniprocessor system that improves performance within the cache hierarchy and the memory back end for both regular and irregular computations. It does this in three ways: by optimizing the use of DRAM resources in the memory controller backend, by prefetching data within the memory controller and delivering it to the processor only when requested, and by remapping previously unused physical addresses within the memory controller. Extending the virtual memory hierarchy by remapping those physical addresses allows optimizations that improve the efficiency of the system bus. The back end includes a parallel vector access (PVA) mechanism that optimizes the use of DRAM resources by gathering data in parallel within the memory controller. The PVA performs cache-line fills as efficiently as a normal, serial controller and performs strided vector accesses from three to 33 times faster. The scalable design is two to five times faster than other gathering mechanisms with similar goals at the cost of only a slight increase in hardware complexity. Professor McKee is working with Dr. Bronis de Supinski, a colleague at Lawrence Livermore National Laboratory, to develop a new coherence protocol and subsystem to go with remapping memory controllers such that multiple aliases (addresses or names referring to

(continued on page 12)

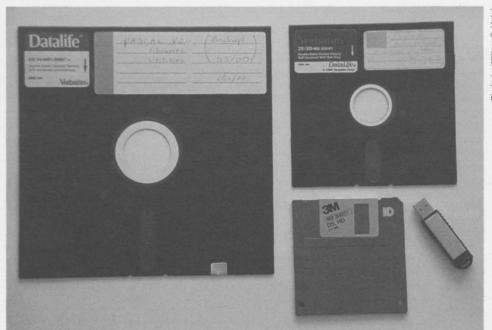

Figure 5. Photograph of the basic component upon which memory-system architectures are built.

### Memory System Architecture Research

(continued from page 11)

memory locations) can exist in the system at once. The protocol has the potential to remove the biggest roadblock to the adoption of the memory controller technology developed to date.

Sally A. McKee, B.A. '85 (Yale University), M.S.E. '90 (Princeton University), Ph.D. '95 (University of Virginia), all in computer science, joined the ECE faculty on July 1, 2002, as an assistant professor and became a member of the Computer Science Graduate Field in September 2002. She was also an adjunct assistant professor at the University of Utah School of Computing during the 2002-2003 academic year. She has taught at the University of Virginia, the Oregon Graduate Institute of Science and Technology, Reed College, and the University of Utah, and has worked for Digital Equipment Corporation, Microsoft Corporation, AT&T Bell Laboratories, and Intel Corporation. Professor McKee has been the principal investigator on three National Science Foundation (NSF) projects with one currently in progress. She has participated in studies funded by the U.S.

Department of Energy and by the Intel Foundation. As a member of IEEE, she has been active for several years in computerrelated activities of the Institute. She is a member of the Advisory Committee of the IEEE Technical Committee on Computer Architecture, and has served as an organizing committee member of 12 international conferences on computer architecture and computing techniques. She is the author or coauthor of over 33 publications in refereed journals and conferences, and is the co-inventor of a U.S. patent. She is also a member of the Association for Computing Machinery, the IEEE Computer Society, the American Association of University Women, and the American Association for the Advancement of Science (AAAS). At Cornell, Professor McKee has received a Faculty Innovation in Teaching Grant and an early career award from the President's Council on University Women. This summer she will collaborate with researchers at the Universitat Politechna de Catalunya under a travel grant from the AAAS/NSF Women's International Science Collaboration Program.

Professor McKee's research interests include computer architecture, and, in particular, memory system architecture; highperformance computing; the interaction of compilers, operating systems, and architectures; hardware/software codesign; performance analysis and prediction; adaptability and accessibility. Her current research focuses on improving memory system performance at all levels. Under a recent award from NSF, along with researchers at Cornell and Georgia Tech, she is creating architectural and operating system-level foundations to enable autonomic highperformance computing systems. Projects under her supervision in the Cornell Computer Systems Laboratory include the design and evaluation of efficient, adaptable, high-performance memory systems and the systems software to exploit them, and the development of metrics and tools for analyzing memory hierarchy performance. In particular, in collaboration with Professor Rich Caruana (Department of Computer Science at Cornell), she is examining the application and adaptation of established machine-learning techniques to problems in computer engineering.

# Teaching Integrative MEMS

The field of microelectromechanical systems (MEMS) not only crosses many areas of traditional disciplines laterally but also transcends vertically in the level of detail within each discipline. Students need to understand not only electromechanical transduction and microfabrication, but also how to use MEMS to change the world by knowing the experimental and analytical techniques to apply to a solution with the necessary level of detail. The spring 2004 course ECE 432, Introduction to Microelectromechanical Systems, taught by Associate Professor Amit Lal, addressed the problem of conveying the inventiveness in MEMS through multiple pathways. First, the lecture material was geared toward fundamental topics such as microfabrication, as well as electrostatic, magnetic, piezoelectric, and thermal effects at the microscale at the chip level. The different energy domains that come into MEMS were used as a way to unify the material. This lecture material, however, does not always translate to the kind of MEMS knowledge conducive to entrepreneurial work in the future.

A second approach allowed the students

to gain hands-on experience in MEMS design. They were given access to three different process flows developed by the graduate students in the SonicMEMS group, including processes using bulk micromachining, surface micromachining, and nickel electroplating, all containing capacitive and piezoresistive sensor elements. This access to three processes for the students is unprecedented as far as is known here. The students chose one process flow to fit an idea that they wanted to implement. The student designs, based on integrated-circuit-design software, were fabricated by the four graduate students (Serhan Ardanuc, Xi Chen, Shankar Radhakrishnan, and Abhijit Sathaye) along with their own designs, and packaged (diced and wire-bonded) onto specially designed pc-boards. The fabricated devices consisted of mature concepts ranging from pressure and acceleration sensors, to more exotic concepts such as magnetic tweezers, optical light valves, microsurgical tools, and electrowetting devices. The students tested their devices and achieved a firsthand introduction to the complexities of packaging and the inaccuracies that occur

during microfabrication. This exercise was not only very useful for the ECE 432 students, but also for the graduate students in the group since they were forced to understand their own processes in a very broad sense.

The third aspect of the MEMS instruction was to ask the students to dream up new ways to use micromachining and micromachines. This aspect was achieved by having the students write term papers that addressed a hypothesis of their interest. The resulting papers included MEMS microsatellites for space, micro propulsion, micro-air-balloons, nano-scale channels for molecular characterization, smart bullets, organic power, radioactive power, etc. A poster session was held for students to present the ideas and analyses that addressed their hypotheses.

The combination of lecture material, hands-on experience on device design and testing the fabricated devices, along with applying the information to further advance the MEMS field, will hopefully lead to MEMS proliferation in companies in which the students will be employed to solve real-world problems.

# Broadband Communications Research

The Cornell Broadband Communications Research Laboratory (CBCRL) in the ECE School was established to develop fundamental knowledge of the devices and circuits that occur in broadband communications systems by study of issues that impact the design of high-performance energyefficient systems. Associate Professor Kevin Kornegay, director of the laboratory, leads a high-energy research group, consisting at present of 13 Ph.D. students and research staff who develop creative device and integrated-circuit solutions to design requirements set by the high standards that will be demanded of the next generation of

wired and wireless communication systems. Typical applications are cellular telephone systems, high-performance networking, and optical communications. Among other goals, the research could lead to smaller and lighter devices with improved data rates and reduced power consumption. The research is supported by corporate and government sponsors. Corporate sponsors include Agilent, Cadence, Cascade-Microtech, Compaq, IBM, Intel and Qualcomm. National government and local sponsors are NSF, DARPA/MARCO (a subsidiary of the Semiconductor Research Corporation (SRC)), and the New York State Office of Science,

Technology and Academic Research. A recent \$200,000 gift from Qualcomm, Inc., will provide three new graduate student fellowships. A team of CBCRL graduate students won third place in the 2002–2003 SiGe (Silicon Germanium) Design Challenge, sponsored by the Semiconductor Research Corp. (SRC). Their project, entitled "A 10 Gb/s Integrated Optical Transceiver," is a good example of the research performed by the CBCRL group.

# "Bleeding-Edge" Computer Technology

Director **Pollock**, at left, with **Abeezer S. Tapia** '02, AMD product marketing manager, center, and **Stephan G Meier** '89, AMD senior architect, at the AMD equipment donation ceremony in Phillips Hall on February 19, 2004.

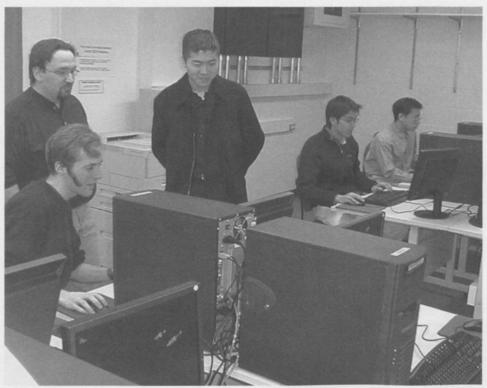

A test run of the new AMD laboratory workstations.

Each AMD computer has a matching SONY liquid-crystal-display (LCD) monitor.

recent donation of 40 top-of-the-line computers by Advanced Micro Devices (AMD) satisfies an urgent need for high-performance computing facilities in the ECE School. The computers, based on AMD Athlon 64-bit 3000+ processors with matching Sony liquid crystal displays (LCD), are located in Phillips Room 329, as shown on this page. The laboratory is designed principally for sophomores and juniors who take ECE 314, Computer Organization, a course that is required for all ECE and computer-science majors. The new facility will also support course ECE 475, Computer Architecture, course ECE 547, Computer Vision, and other courses requiring circuit and /or chip design.

It would appear that acquisition of these computers now places the School at the "cutting edge" of computer technology. Because of the highly advanced design of the new equipment, perhaps it is better to designate the AMD laboratory as being beyond the cutting edge and operating at the "bleeding edge." In that sense, the new computers will give students much greater computational ability and will also challenge them to devise ingenious solutions to problems that may occur due to possible instabilities of the novel 64-bit processors. Similarly, a comparison of the now well-established hybrid electric vehicle with the projected fuel-cell-powered auto suggests that the latter has many promising features but still "needs work," again an example of bleeding-edge technology.

Photographs by William C. Mutch

Students examine the new AMD laboratory equipment. **Robert L. Beaver,** ECE manager of computer operations, is standing at left.

# Recent Faculty Accomplishments

Excellence in Teaching awards were announced at the College of Engineering Fall 2003 Awards Ceremony on November 6, 2003, in the Memorial Room of Willard Straight Hall.

All award recipients in the School are designated by a colored square (**1**).

- Assistant Professor Alyssa Apsel (opto-electronic very-large-scale integrated systems), the Clare Boothe Luce Assistant Professor of Electrical and Computer Engineering, has been developing her research group and facilitating industry interactions with Agiltron, Lockheed Martin, and IBM corporations. During this academic year she was granted a CAREER award from the National Science Foundation for her proposal "Designing with Light: Comparative Analysis and Design of Optical Interconnects for Chip-to-Chip Communication," received a \$50,000 award from the 2004 Lockheed Martin University Research Grants Program for her project "Resonant Monolithic Photodetectors and On-Chip Waveguides for Integrated Optoelectronics," and was asked to act as an associate editor for IEEE Transactions on Circuits and Systems II.

- Professor Joseph M. Ballantyne (opto-electronic devices and materials) has been on a leave of absence during the 2003–2004 academic year in Jerusalem, Israel.

- Lecturer John C. Belina (bioelectronics) assistant director of the ECE School, was faced in the fall semester with a 40 percent increase in class size in course ECE 210, Introduction to Circuits for Electrical and Computer Engineering. More solid-state material was added in the course to prepare students for course ECE 315, Introduction to Microelectronics, in the spring term with Professor J. Richard Shealy. This move seems to have been successful according to student feedback, and it eased the transition to ECE 315's more intense treatment of devices. A significantly enhanced ethics component was added to ECE 210 this fall with the assistance of Professor Ronald R. Kline and Park Doing, B.S. '88, M.E.E. '93, post-doctoral associate in Science and Technology Studies. A videotape of the class discussion was made to help meet Accreditation Board for Engineering and Technology (ABET) direct evidence requirements. In his work with course ECE 402, Biomedical Instrumentation Design, a culminating design experience (CDE), John worked to significantly increase student exposure to the ABET design requirements, including the "Professional Components." This spring the design phase was moved ahead two weeks to deal with the end-ofthe-semester workload issue of students in multiple CDEs so as to allow them more time for final report writing.

John was named by graduating senior and Merrill Presidential Scholar Paul Anthony George as the Cornell faculty member who made the most significant contribution to his college education and experience.

- Professor Toby Berger (information theory and communications), the Irwin and Joan Jacobs Professor of Engineering, was on sabbatical leave during this academic year at the University of Virginia in Charlottesville in the fall term and at Harvard University in the spring, where he taught new courses, made new research associations, gave several talks, and arranged for visits thereto by his graduate students. Toby continues to give presentations at major conferences and deliver invited lectures at several prestigious institutes concerning the interface between information theory and neuroscience. His work in this area has gained increasing recognition by the neurosciences community while simultaneously leading to new informationtheoretic investigations into novel channel models. Toby is a co-principal investigator with Sergio Servetto, Lang Tong, and Stephen Wicker on the new National Science Foundation grant in the ECE School on wireless sensor networks.

- Associate Professor Adam Bojanczyk (computer engineering, parallel architecture, and algorithms for signal and image processing) has developed an algorithm for computing the total least-square solution to the orthogonal Procrustes problem.

- Assistant Professor Martin Burtscher (computer systems, microprocessor architecture, compiler optimizations) was the recipient of a Michael Tien '72 Excellence in Teaching Award in 2003, became the principal investigator of a National Science Foundation Information Technology Research grant, and continued his research on his grant from Intel Corporation. During this academic year Martin diversified his research into compression and micro-architectural speculation, designed a new senior-level computer engineering course on high-performance processor architecture, and taught the course for the first time in the 2004 spring term.

- Professor Hsiao-Dong Chiang (analysis and control of nonlinear systems with applications to electric-power networks) has filed two USA and Patent Cooperation Treaty (PCT) patent applications on a nonlinear-indices-based lung-cancer diagnosis system now under extensive testing at a large hospital. He has also filed one PCT and Japanese patent jointly with Tokyo Electric Power Company, Tokyo, Japan, on a boundary controlling unstable (BCU) equilibrium point method for direct power-system transient stability. Hsiao-Dong is considering filing a patent application, through the Cornell Research Foundation, for his design of a novel paroxysmal atrial fibrillation identification

system that achieves very high diagnosis sensitivity with acceptable specificity and requires very short duration, say 30 minutes, of heart rate variability (HRV) signals. He is also developing a dynamical trajectory-based global optimization methodology for solution of general nonlinear problems.

■ Associate Professor David F. Delchamps (control and system theory) was on sabbatical leave during the spring 2003 semester and spent much of the period studying game theoretical reasoning (coupled with dynamical-systems ideas and insights from the theory of mechanism design) to problems in the theory of evolutionary computation and to more general problems in the modeling and analysis of systems involving many interacting agents with limited shared information and conflicting objectives. He is planning to teach a new 400-level course in fall 2004 that addresses subject matter from the area(s) he has been exploring. During this academic year David has taken on a somewhat major new position as faculty co-chair of the Fraternities and Sororities Residential Initiative Programming Council. His principal responsibility in that position is to facilitate and promote faculty involvement with the Greek system along the lines of the Faculty Fellow and House Fellow programs associated respectively with the North and West Campus components of the Residential Initiative.

David was selected by members of the IEEE Student Branch to receive the 2003–2004 Professor of the Year Award.

- Professor Lester F. Eastman (compound semiconductor materials, devices, and circuits), the John LaPorte Given Professor of Engineering, received the 2003 IEEE Microwave Theory and Technique Society Distinguished Educator Award. In recent research Lester has determined the lifetime of longitudinal optical phonons in high electric fields, for various (Ga) AlN/GaN heterojunctions. This is the key parameter, ranging from 350 to 800 femtoseconds, that limits electron channel velocity. This research was done in cooperation with Prof. Matulionis of Vilnius, Lithuania, with students Yun-Ju Sun and Alexei Vertiatchikh.

- Professor Donald T. Farley (radiowave and upper atmospheric physics), the J. Preston Levis Professor of Engineering, began phased retirement in July 2003. He still teaches a large course load in the fall semester, but does not teach in the spring, a pleasant arrangement that allows him to spend more time on research. This past semester Don prepared for NSF panel reviews of the Jicamarca Observatory in Peru and related activities, gave two invited lectures in Peru (one in Spanish), and is scheduled to give an invited talk in July in the United Kingdom.

(continued on page 16)

- Professor Terrence L. Fine (information theory, inference, and decision making in the presence of uncertainty), director of the Center for Applied Mathematics, has proposed revisions of the ECE undergraduate systems curriculum that effect a much-needed modernization of our basic systems curriculum, and, in so doing, also narrow the wide gap between electrical engineering systems and computer engineering. In this academic year two of Terry's Ph.D. candidates completed their studies, and he had two refereed journal papers accepted for publication in IEEE Transactions. A fall 2003 sabbatical enabled him to complete and send to Prentice-Hall his undergraduate textbook Probability and Probabilistic Reasoning for Electrical Engineering and Computer Science. The sabbatical also provided time for two weeklong visits to discuss research on the foundations of probability and to present invited talks. Progress was, and is, being made on his concept of chaotic probability for objective frequentist random phenomena.

- Associate Professor Zygmunt J. Haas (wireless communication and networks, mobile systems) was the 2003 recipient of the Michael Tien '72 Excellence in Teaching Award and also received the Highly Commended Paper Award at the IEEE International Conference on Advanced Information Networking and Applications (AINA 2003) at Xidian University, Xian, China, March 27–29, 2003.

He was also reselected as IEEE Expert Lecturer for the IEEE Communications Society for 2002-2003 and 2003-2004. Zygmunt reports that in the past year, his group has made substantial progress in research on wireless networks scalability. In particular, both upper and lower bounds have been developed under most general conditions and the research has shown that the bounds are tight. These results are of significant importance to the sensor networks community; many researchers have expressed interest in this work and have asked for publication preprints. The group has also developed a scalable network simulator of hundreds of thousands of nodes (a capability that is orders of magnitude larger than that of any tool publicly available until now). Again, the interest from the ad hoc networking community has been well above the expected level. Current goals in research on Security of Ad Hoc Networks have been completed and substantial progress has been made in the area of applications of the ad hoc networking technology to biosystems.

■ Professor David A. Hammer (plasma physics, controlled fusion, intense ion beams), the J. Carleton Ward, Jr. Professor of Nuclear Energy Engineering, has been selected to receive the 2004 Plasma Science and Applications Award from the IEEE Nuclear and Plasma Sciences Society. David is being recognized by the society "for fundamental contributions to the understanding of intense relativistic electron beam propagation, intense ion-beam generation and propagation, innovative plasma diagnostic development for intense beam devices, x-ray source development using novel plasma pinches, and for his commitment to the mentoring of graduate students in the field of plasma science." This prestigious

award is presented annually to an individual who has demonstrated "outstanding contributions to the field of plasma science." In recognition of this award, David will present a plenary address at the 2004 IEEE International Conference on Plasma Science in Baltimore in June. In research, David reports determination of the X-pinch x-ray source size through the Ph.D. thesis work of Byungmoo Song. This source is approximately one µm in size and therefore required novel measurement methods to be developed and implemented after standard measurement methods proved inadequate for such a small source. In another duty as program chair of the American Physical Society Division of Plasma Physics Meeting, October 27-31, 2003, David organized a five-day meeting involving 1,675 papers and approximately 1,550 people. Dave has also been elected the vice chair of the Division of Plasma Physics of the American Physical Society (APS/DPP). He had responsibility for the program of the annual meeting of the APS/ DPP in November 2003. From November 2003 to November 2004, he is chairing the division.

Associate Professor Sheila S. Hemami (application-specific compression techniques for packet networks, networking aspects of visual communication, and multirate coding and transmission) has been active this academic year with IEEE affairs. She was appointed associate editor of the IEEE Transactions on Signal Processing and is also a member of the Image and Multidimensional Signal Processing Technical Committee of the IEEE that includes program committee membership for both IEEE International Conference on Image Processing and IEEE International Conference on Acoustics, Speech, and Signal Processing. In student activities, Professor Hemami helped organize an information session for undergraduates on procedures for applying for NSF graduate fellowships, and has written recommendation letters for ten undergraduates (a total of perhaps 60 letters) for various fellowship and graduate programs.

Professor Hemami received the 2003–2004 Ruth and Joel Spira Excellence in Teaching Award.

- Professor C. Richard Johnson, Jr. (adaptive control and signal processing) has received NSF funding for a three-year grant on blind adaptive channel shortening that is useful in multicarrier communication. Rick has also established multiyear (through 2006) interaction with French researchers P. Duhamel at Supélec École Supérieure D'Électricité and P. Regalia at l'Institut National des Télécommunications in ultrawideband receiver design and composite adaptive systems approach to receiver design.

- Associate Professor Edwin C. Kan (modeling and fabrication of nanometer-scale devices) received the 2003 Robert '55 and Vanne '57 Cowie Excellence in Teaching Award. During this academic year Edwin's research group has made a number of significant developments in several areas of interest. A new chemoreceptive scheme has been pioneered for a complementary metaloxide semiconductor (CMOS) interface to sense and actuate molecules in air and liquid based on nonvolatile charge in floating gate structures.

Integration of carbon-based or nanowire-based structures on a silicon substrate provides another avenue of design optimization for which the group has been developing new techniques mainly on sensor applications. For nonvolatile memory scaling, the group has pioneered development of metal nanocrystal memories, a promising technology that will reduce memory hierarchy and provide portable, low-cost, large-volume, and fastaccess memory systems. For transistor scaling, the group has worked on novel devices and circuits built from independently driven double-gate MOS field-effect transistors. New circuit topologies have been constructed for dynamic threshold and gain, internal feedback, cascade reduction, and adiabatic switching, which have distinctive advantages in power and speed over single-gate operations. In architecture, pulse-wave interconnects have been proposed that change the information representation from potential levels to pulses and hence provide much improved scaling behavior for delay and power of global interconnects.

- Professor Michael C. Kelley (upper atmospheric and ionospheric physics), the James A. Friend Family Distinguished Professor of Engineering, published his work under the 2002–2003 Fulbright Scholarship to the physics department at the University of Crete in Greece. Mike also completed work as a National Academy of Sciences committee chair with the responsibility of creating a ten-year vision for the field of atmosphere-ionosphere-magnetosphere science. The report has been reviewed, accepted, and published.

- Professor Paul M. Kintner (atmospheric plasma physics) has been elected a fellow of the American Physical Society. He was recognized for his "investigation of microstructure, wave-particle interactions, and plasma acceleration in space plasmas using sounding rocket and satellite experiments and for innovative applications of global positioning systems (GPS) technology to space plasma experiments." On January 22, 2004, at 08:57 UT, Paul successfully launched the SERISO sounding rocket (see Figure 6) from Svalbard, Norway. In other research he obtained a patent for making GPS software receivers practical, and continued leading NASA's Geospace Mission Definition Team toward implementation of a satellite program. In preparation for the next ABET visit, Paul wrote the first draft of the ECE ABET Self-Study Questionnaire.

- Professor Ronald M. Kline (history of technology and electrical engineering) significantly extended the Bovay Program in the History and Ethics of Engineering by hiring post-doctoral associate Park Doing, B.S. '88, M.E.E. '93, giving ethics seminars in ENGRG 150 (500 students) and other courses, and creating a web site about the activities of the program (http://bovay.ece.cornell.edu). Ron continued his work on a book-length project on the history of information theory and cybernetics.