# DESIGN OF INTEGRATED, EFFICIENT POWER AMPLIFIERS FOR NEXT-GENERATION WIRELESS COMMUNICATIONS

#### A Dissertation

Presented to the Faculty of the Graduate School

of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by

Ian Andrew Rippke

January 2005

# DESIGN OF INTEGRATED, EFFICIENT POWER AMPLIFIERS FOR NEXT-GENERATION WIRELESS COMMUNICATIONS

# Ian Andrew Rippke, Ph.D. Cornell University 2005

An integrated power amplifier and DC-DC converter are presented to create a variable supply voltage power amplifier to improve battery life in cellular handsets. This system has the ability to reduce the average battery current drawn by a handset power amplifier by operating at lower supply voltages when not transmitting at maximum power. This type of system has not been adopted because of the need for additional circuitry when used with traditional power amplifier modules. To be attractive to system designers, advanced power amplifiers need to exhibit the integration that has been seen in modern radio receivers. In this work, SiGe BiCMOS technology is harnessed to achieve the integration of both circuits on one die, presenting a solution to the desire for high efficiency in a single chip solution.

The design of power amplifiers in SiGe technology is explored, with a focus on the design of a WCDMA handset power amplifier for third generation mobile systems. The design challenges of such a circuit are presented, along with a design methodology involving a mix of time and frequency domain simulation techniques. Layout concerns are addressed in regards to the SiGe BiCMOS process, and their impact on power amplifier performance is highlighted. Measured results are presented which meet the linearity requirements of WCDMA.

A high switching frequency DC-DC converter is also examined, with a focus on integration of such a circuit with a power amplifier. The impact of frequency

selection and converter efficiency is analyzed, and several techniques to improve the efficiency are presented. Simulation and measurement results are presented which show excellent agreement over the broad range of converter operating conditions. An analysis method for determining the average reduction of battery current in a variable supply voltage system is presented, with results given for the DC-DC converter/power amplifier integrated system. The integration issues and system performance in regards to physical layout are discussed. The final system measurements show the successful performance of the power amplifier under variable supply voltage operation with the DC-DC converter. The results of this work demonstrate the feasibility of such an integrated, efficient power amplifier and provide a path for integration of advanced power amplifier systems with other transceiver components.

#### BIOGRAPHICAL SKETCH

Ian Andrew Rippke was born on July 28, 1978 to Mr. Robert Henry Rippke and Mrs. Marcia Ruth Rippke in Princeton, New Jersey. Ian graduated from Hempfield High School in Landisville, Pennsylvania in 1996. He received his undergraduate education from Lafayette College in Easton, Pennsylvania and graduated with Honors in May 2000 with a Bachelor of Science in Electrical Engineering. In August 2000, Ian began graduate study at Cornell University. He received a Master of Science in Electrical and Computer Engineering in October 2003. He completed his Doctor of Philosophy in Electrical and Computer Engineering with a minor in Applied Physics in 2005. Ian is currently a member of the Applications Engineering team at Xpedion Design Systems, Inc. in Allentown, Pennsylvania.

#### ACKNOWLEDGEMENTS

I wish to acknowledge the support and guidance of my thesis advisor, Professor Kevin T. Kornegay. From the beginning he encouraged me to dream big and then pushed me to achieve those dreams. I would also like to thank the members of my special committee, Professor Alyssa Apsel and Professor Lester F. Eastman, for their guidance and support of my work. Additionally I am grateful to Dr. Jon S. Duster for his countless hours of guidance and lab assistance.

I would like to acknowledge the support I received from the National Science Foundation and the Intel Corporation through funding of my graduate study at Cornell. I wish to extend special thanks to Stewart Taylor at Intel for his mentoring and technical guidance during my project and my six month stay in Oregon.

I would also like to thank past and present CBCRL research group members Dr. David Fried, Dr. Sean Welch, Dr. Kyle Maurice, Drew Guckenberger, Daniel Kucharski, Dr. Conan Zhan, Yanxin Wang, Franklin Baez, Rich Gabrielson, Brian Welch, Javier Alvarado, and Dr. Mihaela Balseanu for their support, assistance, and willingness to provide innumerable distractions from work. I would like to particularly thank Jami Meteer for providing a sounding post and individual support group during my time in graduate school.

Finally, I would like to recognize the incredible support of my wife Kristie, my parents Bob and Marcia, and my in-laws Carl and Margaret. They have all had such a profound effect on my research through their continuous support and eagerness to see me succeed in my endeavors.

To my wife Kristie, who through her love, support, and patience has taught me what truly matters in life

# TABLE OF CONTENTS

| Chapter 1 | : Introduction                                           | 1  |

|-----------|----------------------------------------------------------|----|

| 1.1       | Perspective                                              | 1  |

| 1.2       | Motivation                                               | 4  |

| 1.3       | New and Original Contributions                           | 5  |

| Chapter 2 | : Linear Power Amplifier Design Fundamentals             | 7  |

| 2.1       | Overview                                                 | 7  |

| 2.2       | Technologies                                             | 8  |

| 2.2.1     | RF Silicon CMOS Technology                               | 8  |

| 2.2.2     | SiGe HBT Technology                                      | 10 |

| 2.3       | Classes of Operation                                     | 12 |

| 2.3.1     | Linear Power Amplifiers                                  | 12 |

| 2.3.2     | Nonlinear Power Amplifiers                               | 15 |

| 2.4       | Tuning and Matching                                      | 19 |

| 2.4.1     | Power Transfer and Load-line Matching                    | 19 |

| 2.4.2     | Small-signal S-parameter Analysis                        | 22 |

| 2.4.3     | Time-domain Tuning                                       | 24 |

| 2.5       | Summary                                                  | 29 |

| Chapter 3 | : Efficiency Improvement Techniques for Power Amplifiers | 30 |

| 3.1       | Introduction                                             | 30 |

| 3.2       | Dynamic Biasing                                          | 30 |

| 3.3       | Linear, Efficient Architectures                          | 31 |

| 3.3.1     | Envelope Elimination and Restoration (EER)               | 31 |

| 3.3.2     | Doherty Amplifiers                                       | 33 |

| 3.4       | Variable Supply Voltage                      | 35 |

|-----------|----------------------------------------------|----|

| 3.4.1     | System Architecture                          | 38 |

| 3.4.2     | Battery Current Analysis                     | 39 |

| 3.5       | Summary                                      | 41 |

| Chapter 4 | : A WCDMA Power Amplifier in SiGe Technology | 43 |

| 4.1       | Introduction                                 | 43 |

| 4.2       | Power Amplifier Design                       | 44 |

| 4.2.1     | Target Specifications                        | 45 |

| 4.2.2     | Output Matching Network Design               | 46 |

| 4.2.3     | Output Stage Design                          | 48 |

| 4.2.4     | Interstage Matching Network Design           | 49 |

| 4.2.5     | Driver Stage and Input Match Design          | 53 |

| 4.2.6     | Final Circuit Schematic                      | 55 |

| 4.3       | Simulation Results                           | 55 |

| 4.4       | Layout Techniques                            | 58 |

| 4.4.1     | Critical Layout Areas in Power Amplifiers    | 59 |

| 4.4.2     | Large Parallel Transistor Layout             | 61 |

| 4.4.3     | Electromigration Concerns                    | 64 |

| 4.4.4     | Final Power Amplifier Layout                 | 65 |

| 4.5       | Board Design for Testing                     | 67 |

| 4.5.1     | Matching Network Design                      | 67 |

| 4.5.2     | PCB Design                                   | 69 |

| 4.6       | Measurement and Testing                      | 70 |

| 4.7       | Summary                                      | 76 |

| Chapter 5 | : A Variable Supply Voltage Power Amplifier  | 78 |

| 5 1       | Introduction                                 | 70 |

| 5.2 D      | OC-DC Converter Design                           | 79  |

|------------|--------------------------------------------------|-----|

| 5.2.1      | Buck Converter Design Overview                   | 80  |

| 5.2.2      | Filter Components                                | 82  |

| 5.2.3      | Transistor Sizing                                | 83  |

| 5.2.4      | Frequency Selection                              | 84  |

| 5.2.5      | CCM/DCM Operation                                | 86  |

| 5.2.6      | W-Switching                                      | 88  |

| 5.2.7      | Comprehensive Loss Analysis                      | 89  |

| 5.2.8      | Circuit Design                                   | 95  |

| 5.2.9      | Simulation Results                               | 97  |

| 5.2.10     | Layout                                           | 99  |

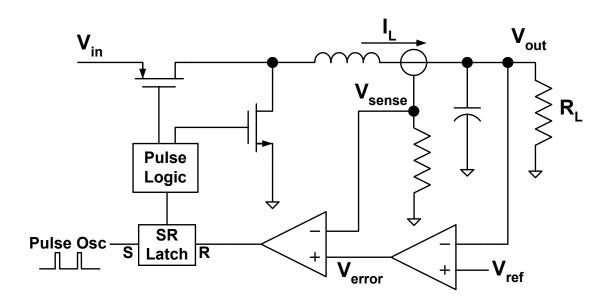

| 5.3 C      | Control Circuitry Design                         | 101 |

| 5.3.1      | Converter Transfer Function                      | 102 |

| 5.3.2      | Voltage and Current Mode Control                 | 104 |

| 5.3.3      | Digital Control Circuitry                        | 106 |

| 5.4 S      | ystem Analysis                                   | 108 |

| 5.4.1      | Power Amplifier Performance                      | 108 |

| 5.4.2      | Chip Layout Issues                               | 110 |

| 5.5 N      | Measurement and Testing                          | 111 |

| 5.5.1      | Board Design for Testing                         | 112 |

| 5.5.2      | Converter Performance                            | 113 |

| 5.5.3      | System Efficiency Analysis                       | 115 |

| 5.5.4      | System Performance                               | 117 |

| 5.5.5      | Comparison to Other Designs                      | 119 |

| 5.6 S      | ummary                                           | 121 |

| Chapter 6: | Conclusions and Suggestions for Further Research | 123 |

| (  | 6.1 S    | Summary                                             | 123 |

|----|----------|-----------------------------------------------------|-----|

|    | 6.1.1    | WCDMA Power Amplifier Design in SiGe BiCMOS         | 124 |

|    | 6.1.2    | High Frequency DC-DC Converter Design               | 124 |

|    | 6.1.3    | Single Chip Variable Supply Voltage Power Amplifier | 124 |

| (  | 6.2 S    | Suggestions for Further Research                    | 125 |

|    | 6.2.1    | Improved Power Amplifier Performance                | 125 |

|    | 6.2.2    | DC-DC Converter Control System                      | 126 |

|    | 6.2.3    | Complete Transmitter Power Control                  | 126 |

| Re | ferences |                                                     | 128 |

# LIST OF TABLES

| Table 1. Target specifications for WCDMA power amplifier                   | 46           |

|----------------------------------------------------------------------------|--------------|

| Table 2. Simulated S-parameters for Class A and Class AB power a           | mplifier at  |

| 1.95GHz                                                                    | 56           |

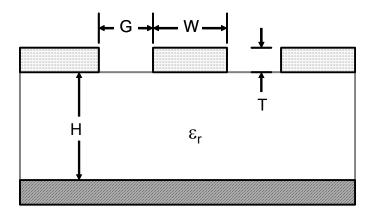

| Table 3. PCB transmission line parameters for FR-4 material                | 68           |

| Table 4. $50\Omega$ transmission line parameters                           | 69           |

| Table 5. Measured s-parameters for stabilized power amplifier at 1.7GHz    | 74           |

| Table 6. Measured power amplifier performance                              | 76           |

| Table 7. DC-DC Converter Parameters                                        | 96           |

| Table 8. Device width versus select bits                                   | 97           |

| Table 9. Simulated DC-DC converter performance                             | 99           |

| Table 10. Measured DC-DC converter results                                 | 114          |

| Table 11. Measured average battery current for fixed and variable supply v | oltage . 116 |

| Table 12. Measured vs. simulated PA small signal gain under variable sup   | ply voltage  |

| operation                                                                  | 118          |

| Table 13. Comparison of previously published variable supply voltage syst  | ems 120      |

# LIST OF FIGURES

| Figure 1. Evolution of cellular standards worldwide and specific needs for 3G2        |

|---------------------------------------------------------------------------------------|

| Figure 2. Reduced conduction angle of output current due to level of input signal13   |

| Figure 3. Reduced bias and conduction angle for class C operation                     |

| Figure 4. Switching power amplifier operational diagram and waveforms                 |

| Figure 5. Load and generation resistance for calculation of maximum power transfer    |

| 20                                                                                    |

| Figure 6. Conjugate match versus load line match under constrained system voltage21   |

| Figure 7. Input-output characteristic for a power amplifier with both conjugate match |

| and load line match at output                                                         |

| Figure 8. L-match at input to RF transistor using shunt-L, series-C configuration 25  |

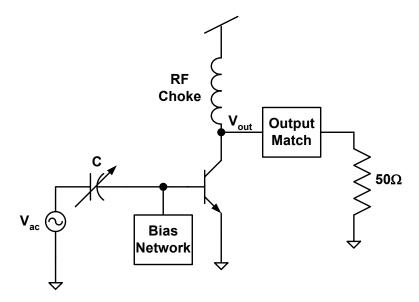

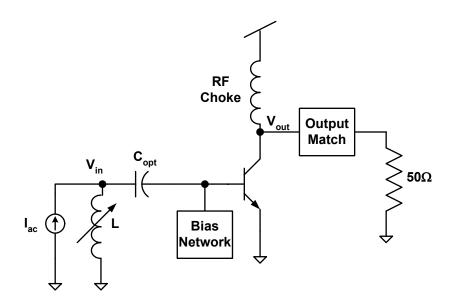

| Figure 9. Determining series capacitor value using AC voltage source                  |

| Figure 10. Determining shunt inductor value using AC current source                   |

| Figure 11. Addition of a driver stage, with operating current and choke inductor      |

| coming from interstage design                                                         |

| Figure 12. Envelope elimination and restoration (Kahn Technique) power amplifier      |

| architecture                                                                          |

| Figure 13. Block diagram of the traditional Doherty power amplifier architecture33    |

| Figure 14. CDG probability curve for urban operation                                  |

| Figure 15. Representation of current-voltage characteristics of a power amplifier     |

| showing variation of operating point in a class AB amplifier under (a) normal         |

| operation and (b) variable supply voltage operation                                   |

| Figure 16. Variable supply voltage power amplifier system architecture39              |

| Figure 17. Typical class AB power amplifier DC current consumption versus output      |

| power40                                                                               |

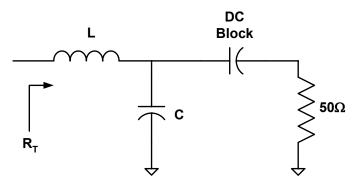

| Figure 18. | Topology of output matching network, including DC blocking capacitor 47 |

|------------|-------------------------------------------------------------------------|

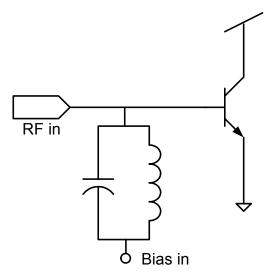

| Figure 19. | Tank circuit for amplifier base bias                                    |

| Figure 20. | Input matching network topology for one half of the differential power  |

| ampli      | fier54                                                                  |

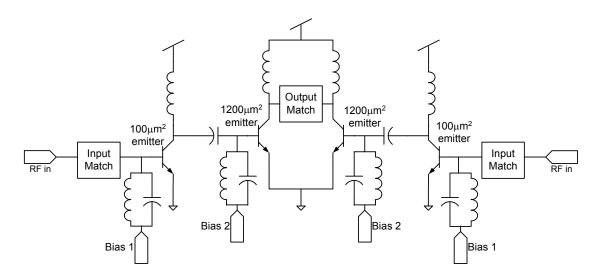

| Figure 21. | Final schematic of full power amplifier design                          |

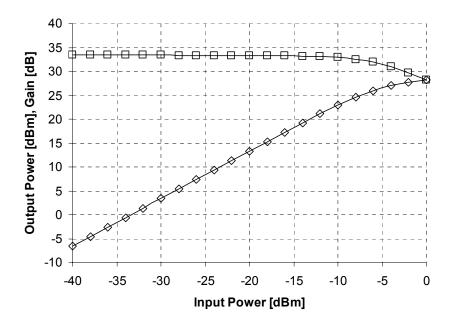

| Figure 22. | Simulated output power and gain vs. input power for class A biasing57   |

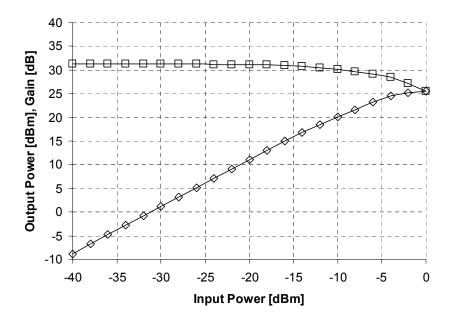

| Figure 23. | Simulated output power and gain vs. input power for class AB biasing 57 |

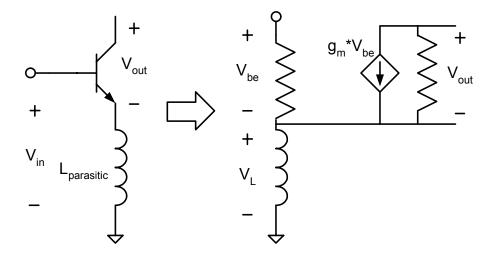

| Figure 24. | Parasitic inductance in emitter acting as voltage divider               |

| Figure 25. | Two finger high breakdown SiGe npn transistor layout                    |

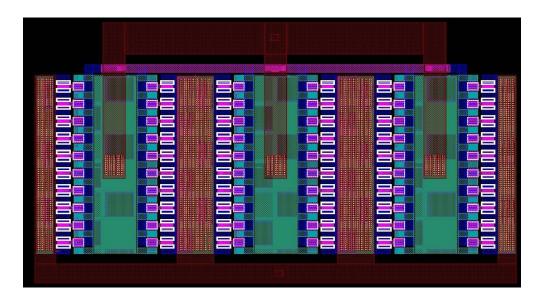

| Figure 26. | Layout of output stage transistor for one half of differential PA63     |

| Figure 27. | Layout of 10 transistor cell for parallel structure                     |

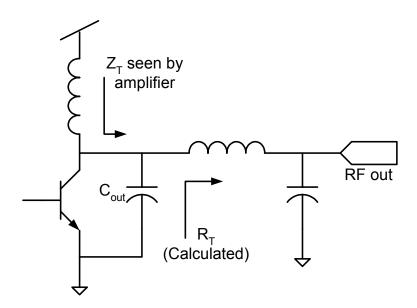

| Figure 28. | Effect of output capacitance on output matching network                 |

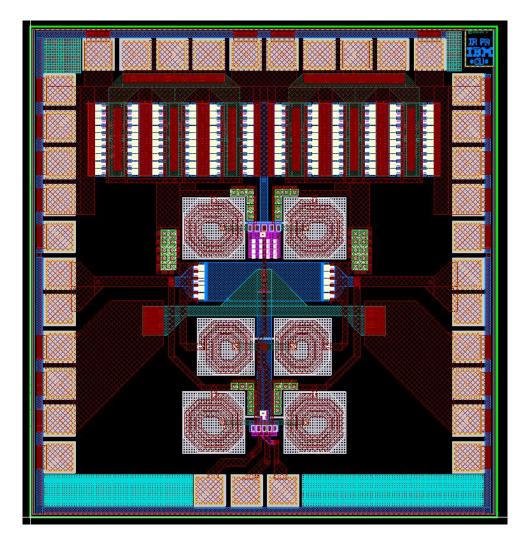

| Figure 29. | Completed Power Amplifier Layout in SiGe 6HP66                          |

| Figure 30. | Grounded coplanar waveguide structure                                   |

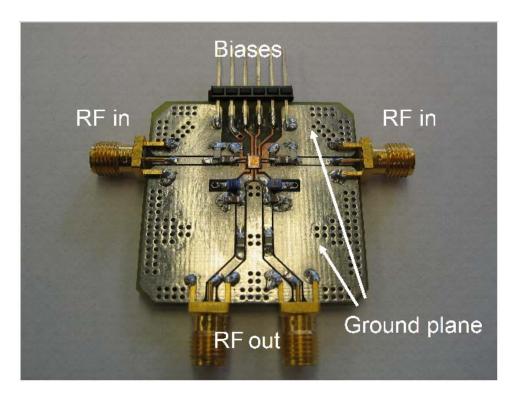

| Figure 31. | Completed board design with power amplifier and all passive component   |

| attach     | ed                                                                      |

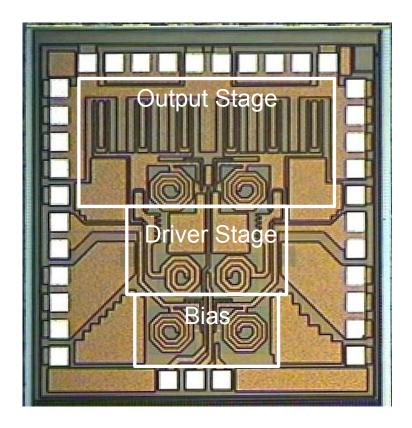

| Figure 32. | 6HP differential power amplifier die photo                              |

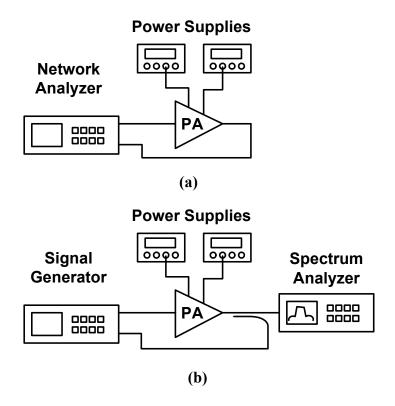

| Figure 33. | Test setup for (a) S-parameter measurement and (b) output power and     |

| ACPI       | R measurement                                                           |

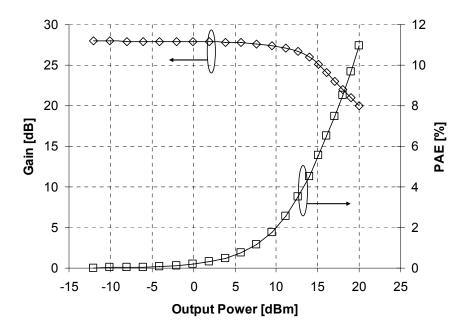

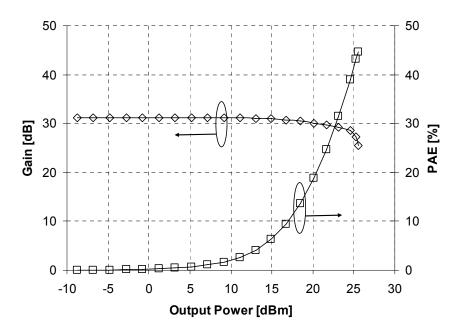

| Figure 34. | Gain and PAE vs. output power for PA with low compression point 74      |

| Figure 35. | Gain and PAE vs. output power for adjusted output matching network75    |

| Figure 36. | System block diagram of power amplifier with variable supply voltage 79 |

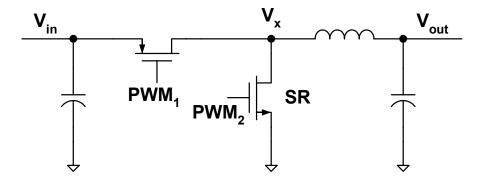

| Figure 37. | Basic buck converter topology8                                          |

| Figure 38. | Buck converter with nFET synchronous rectifier                          |

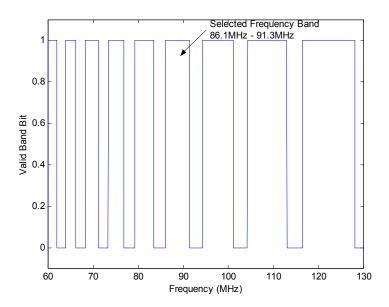

| Figure 39. | Frequency selection analysis results for buck converter in WCDMA        |

| applic     | eations 84                                                              |

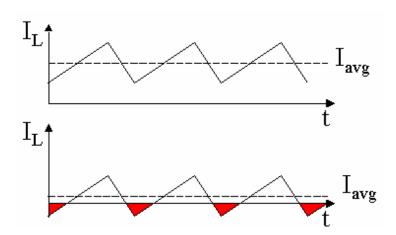

| Figure 40. Continuous conduction mode inductor current for high (top) and low        |

|--------------------------------------------------------------------------------------|

| (bottom) average load current86                                                      |

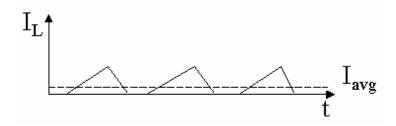

| Figure 41. Discontinuous conduction mode inductor current waveform                   |

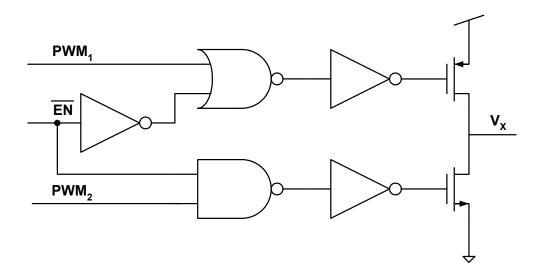

| Figure 42. W-block used to vary effective gate width of switch transistors           |

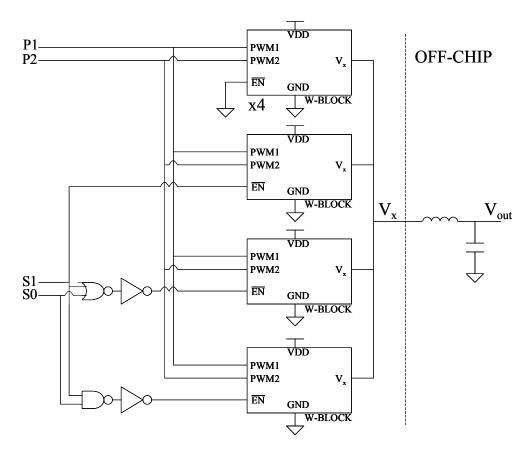

| Figure 43. Parallel connection of W-blocks to create the PFET and NFET switches of   |

| a buck converter89                                                                   |

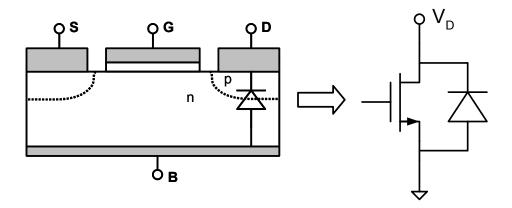

| Figure 44. Body diode from drain to bulk in NFET and its equivalent circuit          |

| representation91                                                                     |

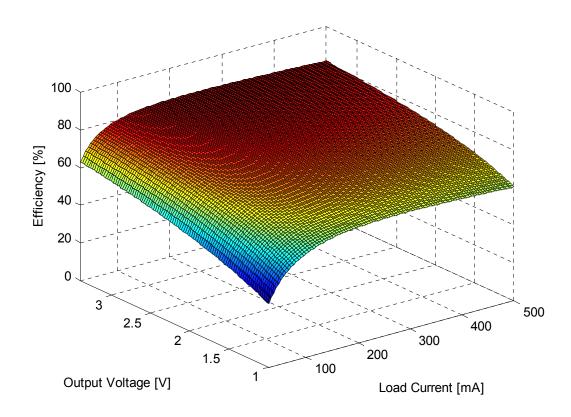

| Figure 45. Efficiency vs. load current and output voltage for a 90MHz converter      |

| operating from 1-3.4V and from 30-500mA95                                            |

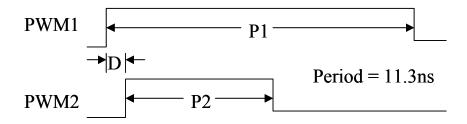

| Figure 46. Pulse width modulator waveform characteristics                            |

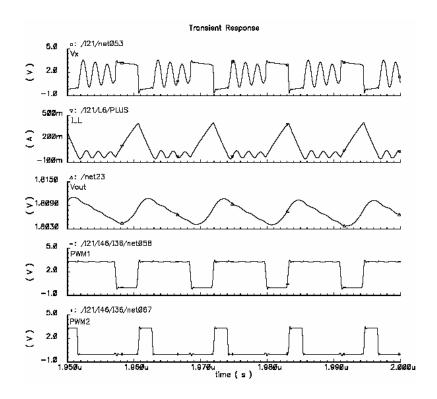

| Figure 47. Simulated converter waveforms for output voltage of 1.8V and 100mA of     |

| load current                                                                         |

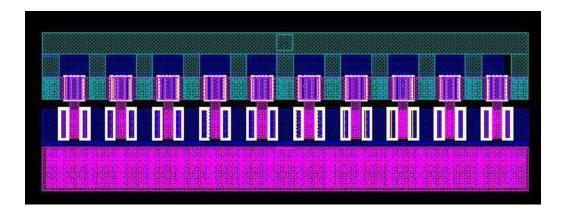

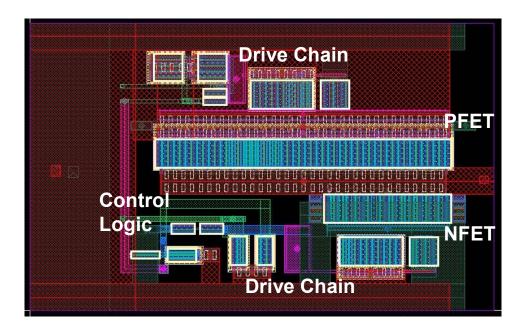

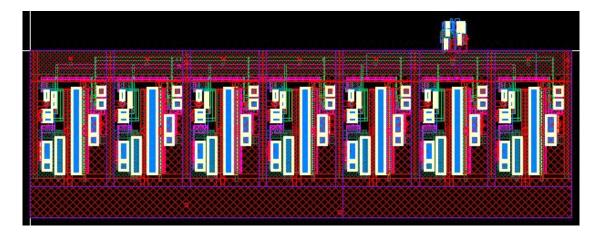

| Figure 48. Layout of single distributed drive "W-block" of converter                 |

| Figure 49. Layout of completed converter                                             |

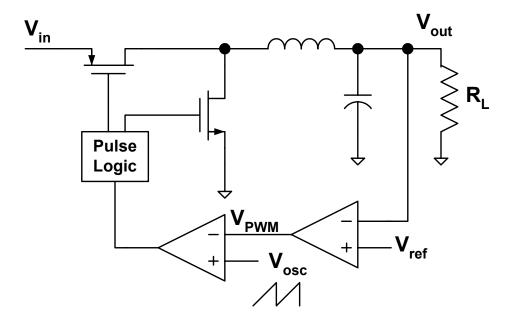

| Figure 50. Basic feedback control loop for a buck DC-DC converter                    |

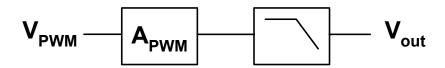

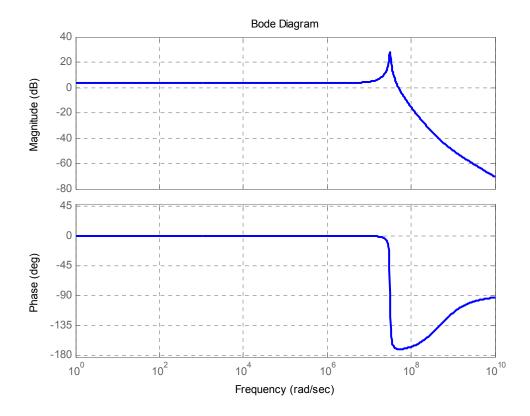

| Figure 51. Open-loop transfer function of buck DC-DC converter                       |

| Figure 52. Bode plot showing magnitude and phase of open-loop converter frequency    |

| response                                                                             |

| Figure 53. Current mode control feedback loop for buck DC-DC converter106            |

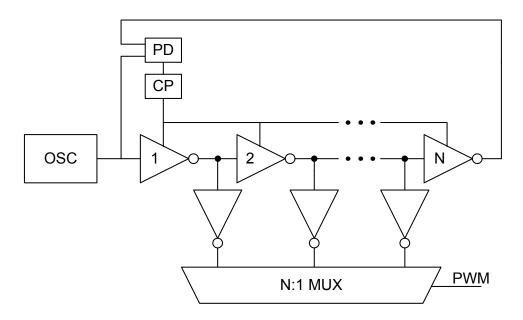

| Figure 54. System diagram of a digital pulse width modulator                         |

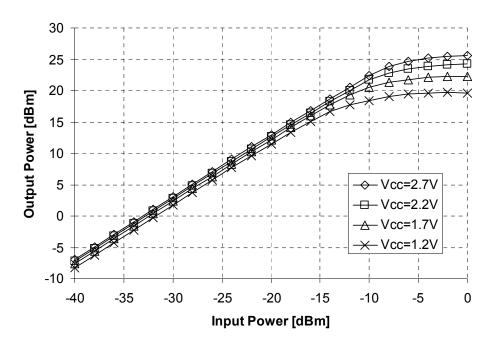

| Figure 55. Power amplifier output power variation with change in output stage supply |

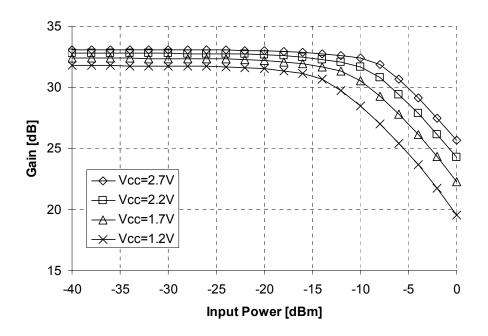

| voltage                                                                              |

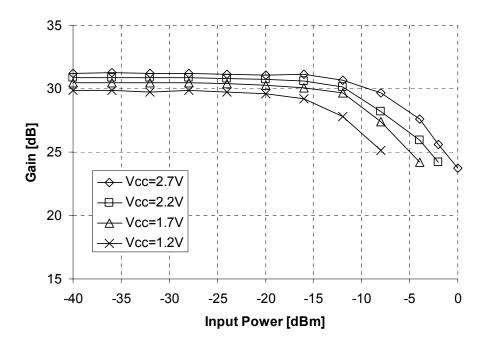

| Figure 56. Power amplifier gain variation with change in output stage supply voltage |

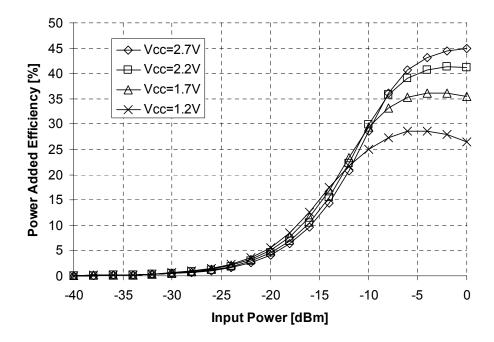

| 109                                                                                  |

| Figure 57. | Power amplifier PAE variation with change in output stage supply voltage |

|------------|--------------------------------------------------------------------------|

|            |                                                                          |

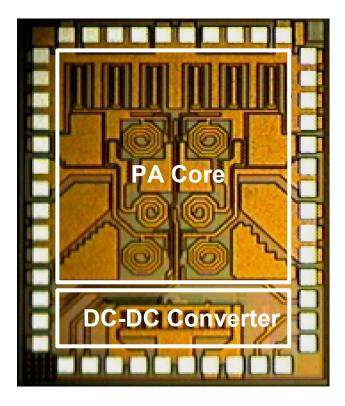

| Figure 58. | Combined power amplifier and DC-DC converter die photo                   |

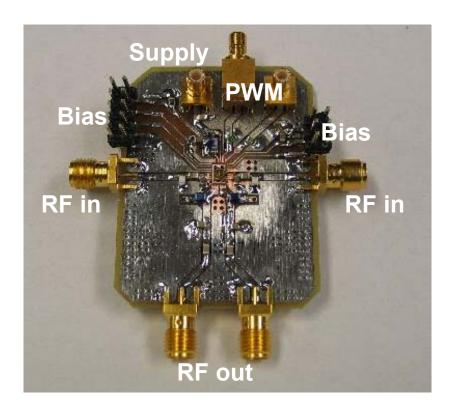

| Figure 59. | Populated PA/converter board for measurement                             |

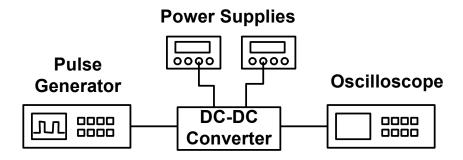

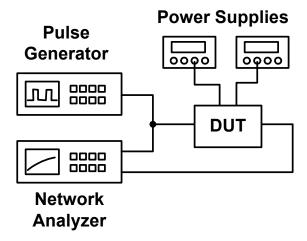

| Figure 60. | Test setup for DC-DC converter measurement                               |

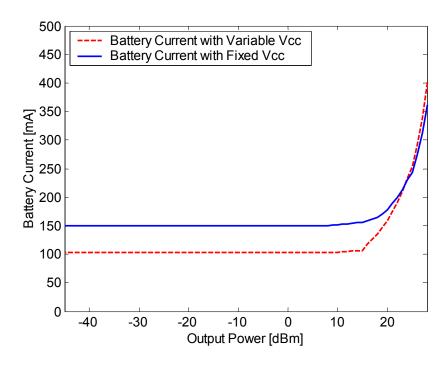

| Figure 61. | Battery current drawn by the power amplifier for both fixed and variable |

| supply     | y voltage 116                                                            |

| Figure 62  | . Test setup for combined DC-DC converter and power amplifier            |

| measu      | rement 117                                                               |

| Figure 63. | Measured gain compression under variable supply voltage operation 119    |

# **Chapter 1:** Introduction

# 1.1 Perspective

The field of radio-frequency integrated circuit (RFIC) design is experiencing a continuing push for integration and miniaturization of transmitters and receivers due to expanding consumer demand for wireless devices. Broad application of wireless technology requires chipsets that are small, robust, low power, and ultimately low cost. This has driven designers to integrate as much of the radio front-end as possible, with the ultimate goal being the reconfigurable single-chip radio that can accommodate multiple standards and applications through flexible and adaptable architecture [1]. The solution to this problem will come in the form of a low-cost, highly integrated radio architecture implemented in a mass-producible, commercially viable process.

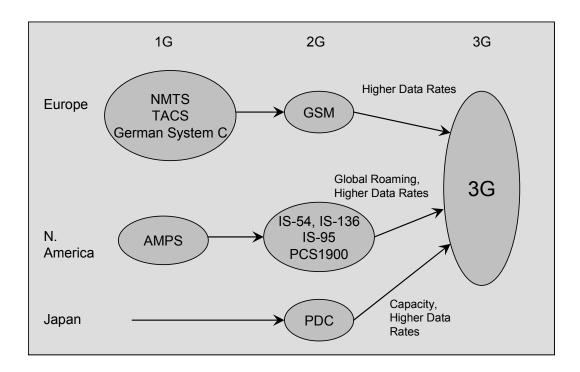

However, the hurdles to such an implementation are numerous. In second generation (2G) cellular phones, the standards vary considerably in different areas of the world, and even in the United States several different standards share the workload of the cellular infrastructure. The move towards third generation (3G) cellular phones looked to unite these varied standards into a single platform of global interoperability. Recognizing the need for higher capacity, broader spectrum allocation, and global roaming, the Third Generation Partnership Program (3GPP) and its associated group 3GPP2 developed a standard that supports both the Global System for Mobile Communications (GSM) and the code-division multiple access (CDMA) standards popular in the United States and Japan [2]. The 3G standards from both groups make

use of wideband code-division multiple access (WCDMA) as the modulation format and access scheme. This provides the potential for up to 3.84 megabits per second (MBPS) of data transfer over the cellular interface. The evolution of cellular standards is shown in Figure 1. Through this harmonization of standards, the adoption of 3G will solve the primary problems of capacity and global accessibility.

Figure 1. Evolution of cellular standards worldwide and specific needs for 3G

The hardware for realizing a reconfigurable radio exists in the baseband (digital) domain in the current multipurpose processors available for use in cellular handsets. The continued advances in scaling of complimentary metal-oxide semiconductors (CMOS) had provided fast, efficient processors with the capability to reconfigure on-the-fly through software. The main technological drawback to the realization of a single-chip radio has been the RF integration that is necessary for such a system. This is not to say that the RF portion of the chip has not benefited from advances in CMOS technology. Several successful integrated transceivers have been

developed in CMOS-only processes, paving the way for integration with baseband processing capabilities [3-6].

But despite the gains made in most areas of transceiver integration, the power amplifier (PA) remains a hurdle to the realization of single-chip radios and overall design integration. The original 1G and 2G power amplifiers made use of gallium arsenide (GaAs) metal-semiconductor field effect transistors (MESFETs) to provide high power devices. These depletion-mode devices often needed complex external circuitry to generate the negative gate voltages required to turn the devices on. This additional voltage generation/regulation circuitry has since been removed due to advances in III-V device technology. Current power amplifier module (PAM) technology for 2G systems is still based on III-V compound semiconductor technology, but primarily uses heterojunction bipolar transistors (HBTs) fabricated by molecular beam epitaxy (MBE). The HBTs are composed of various alloys of III-V compounds such as aluminum gallium arsenide (AlGaAs) and indium gallium phosphide (InGaP), along with GaAs as the epitaxial layers. These devices achieve the high performance of MESFET devices, but have the advantage of a positive base-emitter voltage control. The current power amplifier chips are packaged in a multi-chip solution with a silicon CMOS bias and control chip encased in the same plastic package. While less complicated than their MESFET counterparts, as a separate module and a different technology this approach continues to defy the advances of transceiver integration.

As the use of more exotic materials and devices like III-V HBTs continues to dominate the power amplifier market, this prevents integration with small, low cost silicon CMOS transceiver circuits. Many of the advances in modern RFIC chipsets such as multi-standard support and advanced linearization techniques have been made possible by the use of digital control techniques which are most easily implemented in silicon CMOS and achieve the greatest advantages when applied to a fully integrated

system. A linearized power amplifier offers higher performance because it can operate closer to saturation or can be tuned to trade-off linearity for efficiency when necessary [7]. Digital circuits can also be used to generate predistorted waveforms that can be used with high efficiency switching amplifiers. An entire transmitter can be linearized to allow the use of a cheaper, less advanced transmitter while still achieving the desired performance [8]. This can be an enabling technique for software defined radios to allow the use of multiple RF transceivers in a single handset, rather than requiring a single high-performance, frequency-agile transmitter. All these approaches and techniques point to the need for a power amplifier that can be integrated with a low-cost transceiver while offering improved efficiency to support the increased features of 3G cellular systems.

### 1.2 Motivation

The current commercial demand and emerging markets for wireless connectivity has motivated this work into integrated, efficient power amplifiers. Wireless standards and applications have evolved rapidly to become one of the fastest growing areas of IC technology. The requirements for these wireless devices are continuously expanding, requiring more and more capabilities from the wireless transceivers as well as the baseband processors. While advances in fabrication technology have allowed designers to shrink the size of their circuits while at the same time increasing their complexity, this often comes at the cost of increased power consumption as more and more features are added, including multiple-standard support for wireless networking and Bluetooth.

Current battery technology is not advancing at the same pace as wireless systems and standards, placing increasing demand on mobile transceivers to be energy efficient [9]. Lack of increased battery capacity could greatly impact the adoption of

3G services. Consumer demand for increased feature content is driving handset manufacturers to look for alternatives to the traditional lithium-ion rechargeable battery. Improved battery technologies are on the horizon, but are still in the development stage and will take several years to emerge into the commercial mainstream

Adaptive systems are one way of dealing with the need for increased efficiency to provide longer battery life in mobile applications. The power amplifier remains a large consumer of energy in any RF transceiver system, often eclipsed only by advanced baseband and multi-purpose processors. Modern wireless standards require highly linear power amplifiers that often sacrifice efficiency to provide adequate linearity at maximum signal output. By leveraging a technology that allows integration of adaptive control features with the power amplifier, this balance between efficiency and linearity can be constantly adjusted to provide the maximum battery performance out of a mobile device. Adaptive efficiency control and integrated power amplifiers can overcome current battery limits while reducing transceiver size and cost in 3G systems.

# 1.3 New and Original Contributions

The design of power amplifiers in silicon-germanium (SiGe) technology has recently advanced to the point of commercial acceptance among handset designers who traditionally favored GaAs PA modules. Designing power amplifiers in this technology is still challenging and provides many hurdles that must be overcome through careful circuit design techniques. Additionally, high operating frequency (10-100 MHz) DC-DC converters are rarely used in low-power systems because of the losses associated with increased switching frequency. At these higher frequencies, however, DC-DC converters have the advantage of being integrated along with the

circuits they drive on a single substrate. The design of such converters presents challenges over traditional converter design that has been explained in this work. The combination of these two techniques leads to one of the first implementations of a single chip power amplifier/DC-DC converter that can realize the battery current savings of dynamic supply voltage adjustment while enabling true single-chip radio solutions in the future.

# Chapter 2: Linear Power Amplifier Design Fundamentals

#### 2.1 Overview

Engineers new to power amplifier design are often amazed by the elegant simplicity of the amplifier itself. It differs little from the textbook common-source or common-emitter amplifier, but the differences themselves are the critical distinctions between power amplifiers and their small-signal brethren. At the heart of understanding power amplifiers is a virtual alphabet soup of naming conventions, each describing the general operation of the amplifier in one or two simple letters.

Beneath this basic façade lies a world that has spanned the careers of many famous engineers, and continues to pique the interest of researchers worldwide. The ultimate challenge of delivering power efficiently has become increasingly more complex through the introduction of elaborate modulation schemes brought about by digital radios. Add to this the increasing performance of silicon technologies and the tried-and-true compound semiconductor devices, and the landscape begins to unfold on a dramatic field which is possibly the last haven of the mysterious 'black art' of microwave design.

But despite all these factors, power amplifier design still boils down to fundamental equations and assumptions that have withstood the test of time, ultimately providing the same starting point as the theory did for designers using vacuum tubes and kilowatts in the early days of radio technology.

This chapter presents an overview of power amplifiers, highlighting the current technologies used, their classes of operation, and techniques used in their design. The process overview will focus on emerging technologies that provide lower cost and increased integration potential. Because of the focus on high data rate communications, linear power amplifiers will be the primary topic of the discussion on classes of operation. Design techniques will cover some of the primary differences between power amplifiers and typical RF circuits, as well as the use of small signal analysis in PA design. Finally, a large-signal transient technique will be discussed as a starting point for linear power amplifier design.

# 2.2 Technologies

For a long time a discussion of microwave and RF power amplifier technology was a very short one, because the only technology of interest was the GaAs MESFET. Improvements in molecular beam epitaxy brought along the successors to the MESFET, the III-V compound HBT and high electron mobility transistor (HEMT). These devices continue to dominate the wireless power amplifier market. Yet with recent advances in compound semiconductor technologies and silicon device scaling, several technologies, while by no means new, are emerging in the power amplifier market as viable alternatives to III-V compound devices. This section will describe the emerging use of Silicon MOSFETs and SiGe HBTs in power amplifier design, with a focus on integrated transceiver applications.

# 2.2.1 RF Silicon CMOS Technology

Scaling of silicon CMOS and the desire for transceiver integration has resulted in a push for RF applications in this technology. Fully integrated CMOS transceivers have already found their place in several wireless standards [10], but almost always with the exception of the power amplifier. The desire to integrate all components of

the radio in a single technology, even on a single chip has motivated much of the research into CMOS power amplifiers.

Despite this integration desire, the technology itself presents several hurdles to be overcome. Foremost among these is the low breakdown voltages of advanced CMOS technologies. While baseband digital circuits are scaling to supply voltages of 1V [11], supplying the required power for many wireless standards requires a much higher supply voltage in order to limit the amount of current that needs to be sourced by the FETs. Counteracting the desire for a higher supply voltage for the PA is the ever-shrinking gate length of CMOS processes. To minimize short-channel effects, the gate thickness is also being reduced [11]. This results in decreasing gate-drain and gate-source breakdown voltages for device reliability. Circuit approaches such as cascoded devices can be used in these situations [12], but now the size of the overall circuit is increasing to accommodate these techniques.

Low cost digital CMOS processes also often lack the integrated passives that are necessary for RF power amplifier design. The lack of metal-insulator-metal (MIM) capacitors increases the process variability of any matching networks. Advanced capacitor architectures such as vertical mesh capacitors [13] can help alleviate this burden, but the close pitch of metal lines in digital processes also reduces the current handling at any level of metal. These thin, narrow metal traces also increase parasitic inductance in the circuit. Even in more "analog-friendly" CMOS processes, the limitation becomes the inductors that can be implemented on-chip. The conductive substrate of most silicon processes allows for large eddy currents that contribute to very low quality factors in inductors. To simplify integration and reduce time-to-market, it is desirable to have all the matching components on-chip, but the lossy silicon substrate limits the quality factor (Q) of on-chip inductors to around 10 at best in bulk CMOS processes [14]. The conductivity of the substrate also provides paths

for signals to couple between circuits or even different sections of the same circuit. This has pushed the power amplifier back into the module space, where advanced substrates such as low temperature co-fired ceramic (LTCC) are used, at increased cost, limited integration, and longer design cycle [15]. Yet the desire for single-chip integration and the benefits of having analog and digital components on one die continues to fuel the research into CMOS power amplifier design.

#### 2.2.2 SiGe HBT Technology

SiGe BiCMOS technology has recently emerged as a viable candidate for power amplifier integration. The graded-base SiGe HBT can achieve the performance level of GaAs-based devices while maintaining integration capabilities enjoyed by CMOS technology. Integrated with a traditional CMOS process, the BiCMOS technology is considerably cheaper than GaAs from a process standpoint. SiGe achieves an almost 5x cost reduction compared to GaAs chips while only adding 10% to the cost of a comparable bulk silicon process. Of additional interest in PA applications, silicon offers three times the thermal conductivity of GaAs, making it an ideal substrate for these circuits [16].

The SiGe 6HP process from IBM represents a major advancement in the area of on-chip passive components in silicon substrates as well. This process includes an "analog metal" layer as the last metal layer of the process. This layer is a 4µm thick aluminum layer that has a much lower resistivity than traditional metal interconnect layers. This reduces series resistance in on-chip inductors, and also provides high current handling. Borrowing from DRAM technology, an oxide-filled deep-trench layer is available which effectively increases the distance between conductive elements such as the turns of an inductor and the low-resistivity silicon substrate. By lowering the series resistance, increasing the substrate spacing, and reducing eddy

currents, inductors with Q factor of 20 have been realized at RF frequencies upwards of 2GHz SiGe technology [17]. These higher quality passives can be used for interstage bias inductors in power amplifiers, though high current handling requirements still limits their use in the output stage of a power amplifier. A second use for the deep-trench structures is in isolation guard rings. These guard rings can be used to reduce the coupling of signals between blocks in a complex RF circuit, and also to shield critical lines from other signals that might inject noise in sensitive areas. These structures can be leveraged to increase the integration of RF circuits, even in the presence of noisy digital logic or high power signals from a power amplifier.

An initial drawback of SiGe technology was the low open-base breakdown voltage BVceo reported from initial technology studies. Reported breakdown voltages of 3-5.5V caused speculation that with voltage swings as high as twice the supply voltage at the output of the power amplifier, the technology would not be able to produce power amplifiers operating at current handset battery voltages.

Recent research indicates that the previous concern over BVceo as the limiting factor in SiGe power amplifiers is unwarranted, and that in fact the devices are capable of operating at voltages well above BVceo [18,19]. These devices will not only survive these voltages instantaneously; they also exhibit excellent reliability when exposed to extreme operating conditions [20]. Further research indicates that SiGe devices used for power amplifiers will not be limited by the Johnson limit, which states that the product of BVceo and the unity gain transition frequency  $f_T$  for a device is constant. Rather, the maximum frequency of oscillation  $f_{max}$  and the breakdown voltage with the base grounded through a resistance (BVcer) instead determine the performance characteristics of SiGe HBTs used in power amplifier applications [18]. These promising results, along with continued research into SiGe power amplifiers

and integration potential have helped establish SiGe technology as a likely candidate for future power amplifier products.

# 2.3 Classes of Operation

The general operation of a power amplifier falls into two categories: linear and nonlinear. The distinction between the two can become somewhat blurry in more advanced topologies, but historically this delineation has been maintained. In linear classes of amplifiers, the output power is a linear function of the input power over some desired power range. Beyond this linear range, the device is said to move into the "saturated" mode of operation, where the output power changes very little for increases in the input power. This represents one of the cases of nonlinear power amplifier operation. Nonlinear power amplifiers can also be designed as switching power amplifiers, where the transistor is used as a switch and the output signal is restored through harmonic filtering of the switch output. This section briefly describes nonlinear amplifiers and their various classifications, but focuses primarily on the linear classes of power amplifiers.

#### 2.3.1 Linear Power Amplifiers

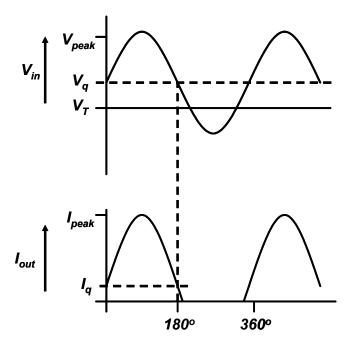

Linear power amplifiers are classified as class A, B, or AB. The difference in the types depends on their conduction angle, or for what fraction of a period of a sine wave the transistor is in the on-state. The concept of conduction angle is illustrated in Figure 2. Here, as the input voltage drops below the threshold of the device  $(V_T)$ , the output current goes to zero until the input voltage rises above  $V_T$  again. The conduction angle is set by the bias point at of the input voltage, given here as  $V_q$ , or the quiescent point. The effect at the output, other than reducing the conduction angle of the signal, is also to reduce the DC level of the signal, given as  $I_q$  in Figure 2. The

benefits of such an approach are explained later. This graphical representation of conduction angle can also be given as an equation for the output current:

$$i(\theta) = \begin{pmatrix} I_{peak} \cos \theta & -\alpha/2 \le \theta \le \alpha/2 \\ 0 & \text{otherwise} \end{pmatrix}$$

(2.1)

where  $\alpha$  is the fraction of time that the amplifier is conducting signal.

Figure 2. Reduced conduction angle of output current due to level of input signal

The desire to reduce the DC component of the output signal while maintaining linearity can be seen from the expression for power added efficiency (PAE). PAE can be written as

$$PAE = \frac{P_{RF,out} - P_{RF,in}}{P_{DC}} \tag{2.2}$$

PAE includes the RF power delivered to the amplifier, in addition to the RF output power and DC power. It can be seen from (2.2) that decreasing the DC component results in a higher PAE. This will be explained in more detail below.

### 2.3.1.1 Class A Amplifiers

In class A operation, the power amplifier conducts for the entire period of the sine wave, or 360° of conduction angle. The bias point of the amplifier is such that there is no clipping of the signal. This is the most linear class of operation from a harmonic generation standpoint, because there is ideally no signal distortion that can contribute harmonics other than the fundamental.

While the class A power amplifier provides the highest linearity, it suffers from a low efficiency. Because the bias points must be chosen as  $V_{peak}$  and  $I_{peak}$ , the maximum efficiency of a class A power amplifier is 50%. This comes from using the RMS values of the output voltage and current waveforms to determine the RF power.

$$\eta = \frac{P_{RF}}{P_{DC}} = \frac{V_{peak} / \sqrt{2} * I_{peak} / \sqrt{2}}{V_{peak} * I_{peak}} = \frac{1}{2} \text{ or } 50\%$$

(2.3)

Here,  $\eta$  is the efficiency of the amplifier, expressed as the ratio of RF output power to DC power supplied to the circuit. So while linearity is maintained over the entire output power range, half the power supplied to the amplifier from the circuit is lost rather than converted into transmitted signal at RF frequencies.

# 2.3.1.2 Class B Amplifiers

A second choice for conduction angle in a power amplifier might be half the period of the sine wave, or 180° of conduction angle. This is known as class B operation. First instinct would say that this could not possibly be linear because half of the signal is clipped on each cycle. Yet Fourier analysis of the signal indicates that

because the output is now an even function, there are no odd harmonics generated through this clipping process [21]. The presence of a strong second harmonic content does impact the output signal, but usually harmonic termination methods are used to remove this harmonic content from the final output signal.

The advantage of using such a conduction angle is that the output signal at the fundamental is the same level as in the class A case, but the DC component of the current waveform is reduced by  $\pi/2$ , which gives a peak efficiency of  $\pi/4$  or 78.5%. This is a significant improvement over the class A amplifier with the only caveat being the need for a proper second harmonic termination.

#### 2.3.1.3 Class AB Amplifiers

Class AB amplifiers span the range of conduction angles between 180° and 360°. They have less second harmonic content that the class B amplifier, but the output signal is no longer an even function which introduces odd-order harmonic content as well. Often the designer will trade off linearity with efficiency in order to choose the bias point, and thus the conduction angle, of a class AB power amplifier.

#### 2.3.2 Nonlinear Power Amplifiers

These classes of amplifiers are differentiated from the linear classes because the output power is not a linear function of the input power. As mentioned above, there are two general types of nonlinear amplifiers: saturated and switching.

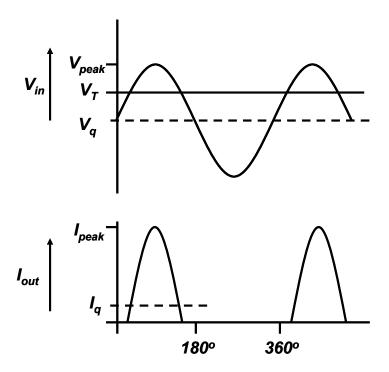

#### 2.3.2.1 Class C Amplifiers

Saturated amplifiers are class C amplifiers. Either through bias choice or signal level, they are designed to conduct for less than 180°. The requirements for this operation are either a very large input signal, or a negative bias level that reduces the

conduction angle by lowering the quiescent level below the threshold of the device. The output then is a mere fraction of the overall signal, resulting in reduced output power, increased harmonic content, and greatly increased efficiency. This operation is depicted in Figure 3.

Figure 3. Reduced bias and conduction angle for class C operation

The further reduction of the DC level over the class B condition leads to efficiencies that are theoretically as high as 100%, however this is not practical because to achieve that efficiency, the conduction angle has gone to 0° and there is no RF power being delivered to the load. Similar operation is achieved when a linear amplifier is driven into saturation. As the output voltage can no longer support the required amplitude at higher input powers, the output signal begins to clip, and the output power saturates. In this condition, the output power level is no longer a linear function of the input level. This type of operation is used in GSM systems, where the

data is encoded entirely in the phase and not in a time-varying envelope, allowing the use of a nonlinear amplifier.

### 2.3.2.2 Class D, E, and F Amplifiers

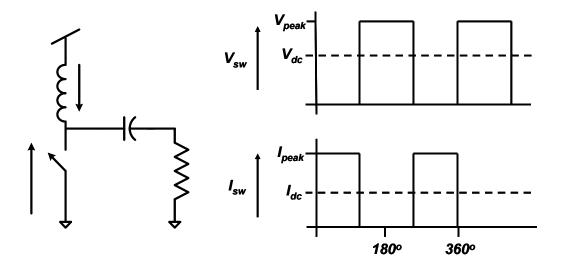

These classes of amplifiers are all based on the use of the transistor as a switch. With the advent of CMOS as a potential candidate for RF power amplifiers, these classes of operation have gained increasing attention because of how well a MOSFET behaves as a switch. In a switching amplifier, theoretically 100% efficiency can be obtained **while still delivering power to the load,** unlike the class C amplifier. This is achieved by using reactive storage elements to preserve the signal when the devices are off. The basic switching amplifier and its important waveforms are given in Figure 4.

Figure 4. Switching power amplifier operational diagram and waveforms

Class D is a fairly straightforward implementation of the direct switching amplifier pictured above. Resembling a "push-pull" type of amplifier, the switch is used to create a square voltage wave at the output of the amplifier, while the current flows into a series resonant circuit at the output of the switch. When the switch is

connected to the supply, half the sinewave of current is provided to the resonant circuit, while when the switch is connected to ground, the negative half-sinewave is generated by the output resonant circuit. The goal of such an amplifier is to never have an overlap of switch current and switch voltage. The ideal design also assumes that there is no loss in the reactive elements. In a real device, the finite rise and fall times of the switch, as well as resistive losses in the passive elements will limit this efficiency, but designs have been reported with upwards of 75% efficiency when operating at RF frequencies [22].

In a class E amplifier, this approach is varied slightly. The switch toggles between open and closed rather than supply and ground. A capacitor across the output of the switch sources the charge when the switch is open. Again, a series resonant circuit is used in the output to regenerate the current at the fundamental frequency. In both class D and class E amplifiers, reactive components are used at the output of the amplifier to filter the square waves. In the case of a class E amplifier, this tuning is designed to minimize the crossover time between the current and voltage waveforms.

Class F takes a different approach and uses tuned networks to purposely enhance or add harmonic content to the output waveform. Less a switching amplifier and more of a clipping of overdriven amplifier, it uses the same principles of square waves to achieve its efficiency improvements. Just as a sine wave can exhibit a more "square-like" characteristic by adding third harmonic content, the waveforms in a class F power amplifier can be tuned in order to emulate a square-wave signal at the output.

Advances in RF CMOS technology and increasing need for long battery life will continue to spur research into switching amplifier topologies for wireless communications. Future wireless systems, such as ultra-wideband (UWB), that make use of pulsed RF transmissions could stand to make the best use of switching

amplifiers. Also, increased digital processing power in RF systems and the use of advanced waveform-shaping techniques could allow systems to exploit nonlinear amplifiers for the transmission of linear signals, realizing both high linearity and high efficiency transceiver systems.

# 2.4 Tuning and Matching

An important part of any RF circuit design is ensuring that the proper impedances are presented to each component in the circuit. In small-signal analysis,  $50\Omega$  is the standard for interface impedances to ensure a lossless transition of signal. The basic principle of operation of an RF power amplifier is to boost the small signal generated by the rest of the transmitter to a level that is powerful enough to be transmitted through an antenna, enabling wireless transmission of voice or data. The power amplifier does this by converting DC power at zero frequency to RF power at some higher frequency in the MHz to GHz range. The goal is to perform this conversion as efficiently as possible, thereby wasting very little energy in the power conversion.

#### 2.4.1 Power Transfer and Load-line Matching

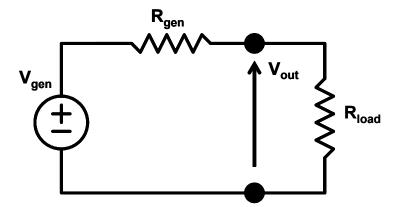

Basic circuit theory indicates that when concerned with power, the maximum transfer of power occurs when the interface impedances are the complex conjugate of each other. This is equivalent to the point where there is no power reflected back to the source, and all is being delivered to the load [23]. Figure 5 shows the setup for a resistively matched system.

Figure 5. Load and generation resistance for calculation of maximum power transfer

The output power is given as

$$P_{out} = \frac{V_{out}^2}{R_{load}} \tag{2.4}$$

where  $V_{out}$  can be represented in terms of  $V_{gen}$  through a voltage divider ratio.

$$P_{out} = \frac{\left[V_{gen} * R_{div}\right]^2}{R_{load}} \tag{2.5}$$

where

$$R_{div} = \frac{R_{load}}{R_{load} + R_{gen}} \tag{2.6}$$

Taking the partial derivative of  $P_{out}$  with respect to  $R_{load}$  and setting it equal to zero gives the condition that  $R_{load} = R_{gen}$  for maximum power transfer. Using the complex representation of  $Z_{gen}$  and  $Z_{load}$  extends this analysis to all complex impedances, resulting in the complex conjugate relationship mentioned above.

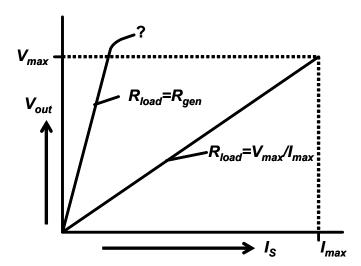

In a situation where the system voltage is constrained, the maximum power transfer analysis begins to break down. The theory assumes small-signal operation, which is not the case in a power amplifier where the output voltage can swing as high as  $2*V_{dd}$  for linear amplifiers. In this case, the maximum signal swing  $V_{max}$  is limited

to  $V_{dd}$ . As illustrated in Figure 6, if  $R_{load}$  was matched to  $R_{gen}$ , then the required voltage could be well above the supply rail. In this case, a load line match must be used, where

$$R_{load} = \frac{V_{\text{max}}}{I_{\text{max}}} \tag{2.7}$$

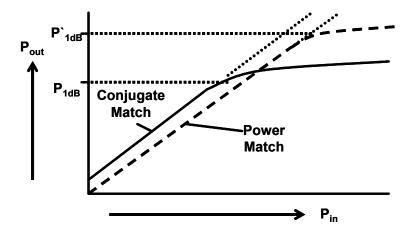

In this case, the system limitations result in a change in the output load from what would traditionally be expected from small-signal analysis. The effect of this type of match can be seen in Figure 7. The conjugate match provides higher gain, but because of the supply voltage necessary to maintain the Ohm's law relationship between  $I_{max}$  and  $R_{load}$ , the signal clips or compresses at a lower power level, given as  $P_{1dB}$ . At this point, the voltage swing has reached  $V_{max}$ , but the output current swing is far from  $I_{max}$ , resulting in less than the maximum power being delivered to the load. By using a load line match, the gain is reduced but the amplifier can now reach its full signal swing because of the choice of  $R_{load}$ . The new compression point using this approach is given as  $P'_{1dB}$ , and is the point where the output peak signal swing is both  $V_{max}$  and  $I_{max}$ , transferring the most power to the load.

Figure 6. Conjugate match versus load line match under constrained system voltage

Figure 7. Input-output characteristic for a power amplifier with both conjugate match and load line match at output

This basic analysis is the starting point for design of most linear power amplifiers, with the load-line criteria determining the output matching components that are necessary to achieve the maximum desired power. From this point, the amplifier is designed "backwards" to the input, analyzing the performance requirements at each stage. This design approach will be explained in more detail later in this chapter.

## 2.4.2 Small-signal S-parameter Analysis

Traditional analysis techniques for RF and microwave circuits usually focus on the use of scattering or "S" parameter analysis for circuit design. Rather than present a review of s-parameter theory, this section will focus on some of the elements more pertinent to power amplifier design. S-parameters are primarily a small-signal design and analysis tool, but they can provide a starting point for power amplifier design as well. Impedance matching networks are most easily designed with the use of s-parameters and the smith chart, however this becomes challenging in power amplifiers because the impedances of the active components can change based on the signal level applied to them.

Stability is a constant concern in power amplifier design. High gain coupled with high signal swing and complex feedback paths through substrates, ground returns, and even the wiring traces themselves makes typical analysis approaches impractical. Traditionally, the stability of a circuit is determined by examining its transfer function and observing the behavior of the poles and zeros of the system. This is neither a simple nor intuitive approach for analyzing power amplifiers. Despite their apparent simplicity and similarity to traditional amplifiers, integrated multi-stage power amplifiers can have many complex feedback paths, such as substrate coupling, that are difficult to model in terms of traditional poles and zeros. A better approach to such a system is to model the power amplifier as a two-port network and analyze it in terms of power transmission and reflection, as is the case in s-parameter analysis. Theory states that for a two-port network to be stable, the real part of its impedance at the input and output must be positive for all frequencies and loads. Expressed in terms of the reflection coefficients  $\Gamma$ , the following criteria are established:

$$\left|\Gamma_{S}\right| < 1 \tag{2.8}$$

$$|\Gamma_I| < 1 \tag{2.9}$$

$$\left|\Gamma_{IN}\right| = \left|S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L}\right| < 1$$

(2.10)

and

$$\left|\Gamma_{OUT}\right| = \left|S_{22} + \frac{S_{12}S_{21}\Gamma_{S}}{1 - S_{11}\Gamma_{S}}\right| < 1$$

(2.11)

These criteria imply that the source and load are both passive, and the input and output impedances are also passive [23]. These equations can be manipulated to produce load and source stability circles on the smith chart. This provides a graphical

representation of what source or load impedances are required to have an unconditionally stable circuit.

When the input and output impedances are known, such as in a  $50\Omega$  system, the use of stability circles becomes excessive in examining the stability of the circuit. Instead, the stability factor K is introduced. Based solely on the s-parameters at each frequency, K can be used to ascertain and guarantee the stability of the circuit.

$$K = \frac{1 - \left| S_{11} \right|^2 - \left| S_{22} \right|^2 + \left| \Delta \right|^2}{2 \left| S_{12} S_{21} \right|}$$

(2.12)

where

$$\Delta = S_{11}S_{22} - S_{12}S_{21} \tag{2.13}$$

From these equations, the necessary and sufficient conditions for unconditional stability are

$$K > 1 \tag{2.14}$$

and

$$\left|\Delta\right| < 1 \tag{2.15}$$

With these conditions satisfied, the circuit will be unconditionally stable. Some circuits will exhibit *conditional* stability, where K < 1 and  $|\Delta| < 1$ . In these cases, stability circles are usually required to see what load and source impedances are required to operate the circuit in a stable fashion.

#### 2.4.3 Time-domain Tuning

An interesting technique for the design of interstage matching circuits for a power amplifier comes in the form of time-domain tuning. This approach can best be

considered a transient replacement for large signal s-parameters. It has the added advantage of providing feedback to the designer on voltage levels and waveforms that might lead to transistor reliability issues or potential instability. The cost of such an approach is increased simulation time for very complex designs, though modern computer workstations are largely eliminating this concern.

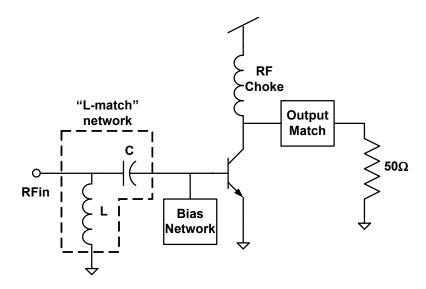

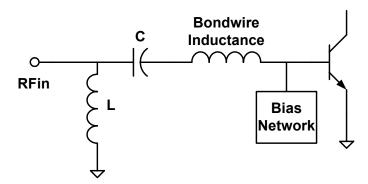

The approach assumes the use of a two-element L-matching network for input and interstage matching, as shown in Figure 8. Time-domain tuning follows directly from the design methodology presented in the previous sections, beginning with the design of the output network and working backwards to the input. Proper device sizing and biasing concerns are dealt with directly and become an integral part of the technique.

Figure 8. L-match at input to RF transistor using shunt-L, series-C configuration

Assume initially a simple two-stage linear amplifier, biased for class AB operation. Assuming accurate models, the impedances of the amplifier are going to be a function of the drive level provided at the input of each stage. To achieve the best performance at the maximum output power, the matching is done in the large-signal

region. Here it is assumed that the output matching network is already designed as described above, with the output transistor sized to deliver the appropriate amount of power to the converted load impedance.

From this point, the bias insertion network can be added. In the case of CMOS power amplifiers where there is no current into the gate (assuming negligible gate leakage current); this can be done with a suitably large resistance. For HBT based designs, the bias current can be sourced through an inductor that is resonated with a capacitor at the fundamental frequency, providing fairly large impedance compared to the input of the device.

The next step is to add a series capacitor in the signal path. It is assumed that the input impedance of the device will be fairly small, given the large transistor sizes needed to provide high output power. The capacitor transforms the impedance to a higher value to provide a load-line match for the first stage. To do this, an AC voltage source is attached to the input, and the voltage is set to the maximum peak-to-peak swing expected from the first stage. This is illustrated in Figure 9. Following from previous discussion, this would normally be twice the supply voltage, but a factor of safety of 10-20% is built into this voltage to prevent the first stage from saturating before the output. As mentioned before, this is a critical flaw the must be avoided for proper linear output.

The value of capacitor at the input is swept until the desired output voltage  $V_{out}$  is achieved.  $V_{out}$  should have a peak-to-peak swing of twice the supply voltage and should be the voltage that delivers the chosen maximum power into the output matching network. Alternatively, the voltage across the  $50\Omega$  termination can also be monitored.

Figure 9. Determining series capacitor value using AC voltage source

Once the capacitance is determined, the shunt inductor can be added to the input of the circuit. This inductor is added to resonate with the series capacitor at the desired operating frequency, presenting a real impedance at the input of the matching network. This is done by adding an AC current source at the input as shown in Figure 10. In this step, the voltage at the input of the matching network is monitored while the value of inductance is varied. The goal is do develop the peak input voltage at that node, which corresponds to the point of resonance. Once the resonant value of inductance is found, the current level can be reduced or increased as necessary to develop the proper voltage level at the input, as determined in the previous step.

It is important to mention that this is an iterative process. The resonance of the network will depend on the drive level of the AC current source, because of the variations of the transistor input impedance with signal level. Thus once the value of current has been changed, a sweep over inductance value should be performed again to be sure the value still corresponds to the resonant peak of the network. Once this iteration is complete, the current level used in the simulation will be close to the operating current of the next stage of the amplifier, and can be used to properly size

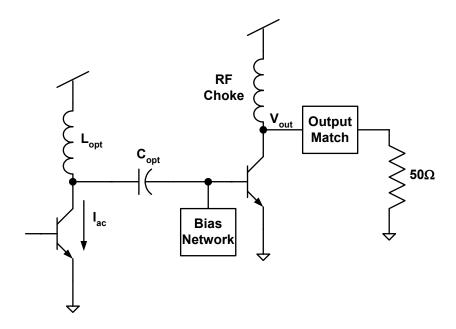

the devices of that stage. In addition, by using this topology, the shunt inductor of the matching network can be used as the RF choke for the driver stage of the design, as shown in Figure 11.

Figure 10. Determining shunt inductor value using AC current source

Figure 11. Addition of a driver stage, with operating current and choke inductor coming from interstage design

The time domain tuning approach can be repeated for the design of additional interstage matches depending on the number of stages needed in the power amplifier. This approach gives the designer a good feel for the signal levels that will be experienced in the final amplifier, more so than in a typical small-signal s-parameter design approach. The use of a load line match at the interstage boundaries ensures that the amplifier will not prematurely saturate, which is critical in the design of linear power amplifiers. It must also be stressed that this approach provides the **starting point** for a design, and that additional factors such as parasitic capacitances and inductances can de-tune the matching networks, resulting in reduced performance. Common optimization techniques available in most commercial simulation tools can be used to further refine the performance of the power amplifier as the design complexity increases.

# 2.5 Summary

This chapter provides an overview of power amplifiers and basic design techniques. The different classes of both linear and nonlinear power amplifiers were explained. The concept of a load-line match was presented, along with the required equations to design the output matching network of a linear power amplifier. Sparameter analysis for power amplifiers was introduced, with a focus on determining the stability of a circuit. Finally, the idea of time domain tuning was presented for use in the design of interstage matching networks in multi-stage power amplifiers. This background provides a starting point for the design of linear power amplifiers for RF circuit applications.

# Chapter 3: Efficiency Improvement Techniques for Power Amplifiers

#### 3.1 Introduction

The maximum efficiency of an amplifier can be determined by its class of operation, as explained in chapter 2. Yet there are several techniques that can be used to improve the efficiency of a power amplifier throughout its operating region. These techniques are attracting more attention because of the incorporation of power control into wireless standards, as well as the use of non-constant envelope modulation schemes, such as CDMA and OFDM. In both of these cases, the transmitter may rarely or never transmit at the maximum output power, which shifts the focus on efficiency to lower power levels. The topics to be covered include dynamic biasing, architectures for improved efficiency, and finally variable supply voltage amplifiers.

# 3.2 Dynamic Biasing

The first and often simplest technique for improving the efficiency of a power amplifier is some type of adaptive bias control. This is achieved by default in the use of reduced conduction angle modes of operation (class AB, class B). In this case, the quiescent current of the power amplifier increases from a nominal value as the RF power increases. This can be expanded to offer 'low power' settings of bias current below a certain RF power threshold. This can be sensed on- or off-chip and bias

control can be implemented through various analog and digital feedback techniques. The variability of the gain in such a system is often the limitation of this approach.

This approach can be extended to provide a dynamic biasing scheme where the bias is adjusted to maintain the linearity requirements of the PA as well. By implementing a bias control circuit, the bias points of individual stages of the power amplifier can be adjusted to provide the minimum current necessary to meet linearity requirements at any given power level [24]. This approach offers improvements to both efficiency and linearity. Several challenges are presented by this approach, however. The system either has to adapt on-the-fly by having some method of sensing the linearity of the output signal, or the bias range must be set beforehand by the designer based on either simulation or initial measured results. The lack of a calibration feature for such a system may reduce its performance from chip to chip as process and environment change.

# 3.3 Linear, Efficient Architectures

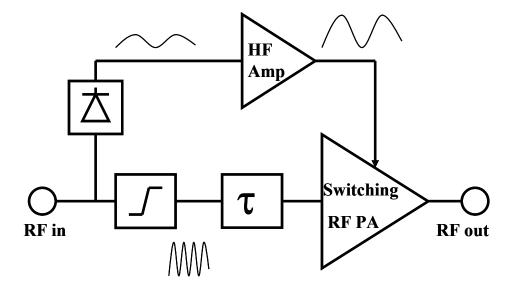

#### 3.3.1 Envelope Elimination and Restoration (EER)

The envelope elimination and restoration approach (also referred to as the Kahn technique after its inventor, Leonard Kahn) involves the use of two different amplification paths based on a polar decomposition of the RF signal [25]. This allows a nonlinear amplifier to be used to amplify the carrier (containing the phase data), while a lower frequency highly linear amplifier is used to amplify the envelope of the signal. These amplified signals are then combined at the output to produce an amplified version of the original signal. The general architecture of the system is given in Figure 12.

Figure 12. Envelope elimination and restoration (Kahn Technique) power amplifier architecture

The RF signal input to the system is passed through a limiter, effectively removing any amplitude modulation component. What remains is a fixed amplitude carrier that contains all the phase information for the transmitted signal. At the same time, an envelope detector strips off just the amplitude modulation or envelope of the signal. This is at a much lower frequency than the carrier, varying at the frequency of the baseband signal. This lower frequency signal can then be amplified by a much lower frequency amplifier, which ideally has a high efficiency. The limited carrier signal is then passed to a switching (or saturated) power amplifier that can amplify the carrier very efficiently as well. The two are recombined by applying the amplified envelope signal to the supply of the switching power amplifier, which re-modulates the carrier and produces an amplified version of the desired transmitted signal.

The one element not described yet is the delay block ( $\tau$  in Figure 12). This block is very important for this system to work with modern digital modulation formats. Because data is contained in both the phase and the amplitude of the signal for non-constant envelope modulation, it is important to preserve this relationship after

the polar decomposition. If the recombined signal at the output has a time delay between the amplitude and phase information, the result will be reduced error vector magnitude (EVM) and ACPR performance, and ultimately loss of data [26]. This requirement is one of the current limitations on this type of amplifier, though prototype designs have been implemented [27]. The advances in DSP technology in baseband processing could eliminate many of the analog components in this technique by producing a direct polar-modulated waveform, making it once again viable for use in linear, efficient RF power amplifier and transmitter architectures [28].

#### 3.3.2 Doherty Amplifiers

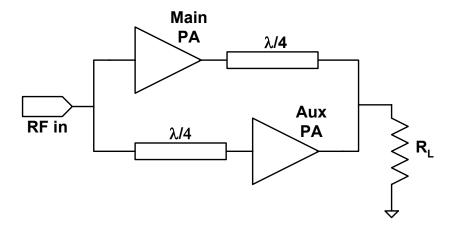

A second type of amplifier topology for improved efficiency is the Doherty amplifier. Based again on work done for high power tube amplifiers for broadcast purposes, this technique has become popular for modern RF power amplifiers because of the efficiency improvements it can offer as the carrier power is backed-off from its maximum. In this technique, the outputs of two amplifiers are combined in the proper phase alignment through the use of a passive power-combining network [29]. The basic configuration of the Doherty amplifier is shown in Figure 13.

Figure 13. Block diagram of the traditional Doherty power amplifier architecture

Here, there are two PAs which operate in conjunction at high power to produce a linear signal. The  $\lambda/4$  transmission lines act as the power combining network, the effect of which is to perform an active load-pull on the devices. The active load-pull technique is described in detail in [21], and summarized here. If a load resistance is acted upon by two generators that source complex currents  $I_1$  and  $I_2$ , then the effective load impedance seen by generator 1 is modified to

$$\mathbf{Z}_{1} = R_{L} \left( 1 + \frac{\mathbf{I}_{2}}{\mathbf{I}_{1}} \right) \tag{3.1}$$

The result is that if  $I_2$  is in phase with  $I_1$ ,  $Z_1$  is transformed to a higher resistive value, and likewise if  $I_2$  is 180° out of phase with  $I_1$ ,  $Z_1$  is reduced. In this respect, the amplifiers in the Doherty configuration act as generators that adjust the impedance seen at the output through proper combining of their power.

In a traditional Doherty amplifier, the main device typically saturates at ¼ of the maximum output power. Beyond this point, the auxiliary amplifier is used to source the power, providing a combined linear output up to the maximum output power. The results is to have a double efficiency peak, with one peak occurring at the maximum power, as expected, and the other at 6dB less, from the main amplifier. This technique as been extended to include multiple stages of amplifiers, producing an additional efficiency peak for each amplifier added [30].

The drawbacks for this approach are the need for the  $\lambda/4$  transmission lines depicted in Figure 13. At typical cellular frequencies from 900MHz to 2GHz, these transmission lines consume considerable board/module space. In an industry looking for increased integration and smaller designs, this approach is directly opposed to that goal. Some work has been done to implement such a system using lumped elements in place of the transmission lines [31]. The performance of such an amplifier has proven comparable to the transmission line architecture, while occupying considerably

less board area. The linearity of such an approach may be an issue, possibly requiring further linearization to be a viable option for RF circuit applications.

# 3.4 Variable Supply Voltage

Another way in which the efficiency of a power amplifier can be improved is through the variation of the PA supply voltage. This seems counterintuitive because it was previously explained that power amplifiers are designed to have maximum efficiency based on their load-line characteristics, which constrain the problem by both the power amplifier current and the supply voltage. The initial reaction is that by varying the supply voltage, the load line would be changing and the efficiency would decrease.

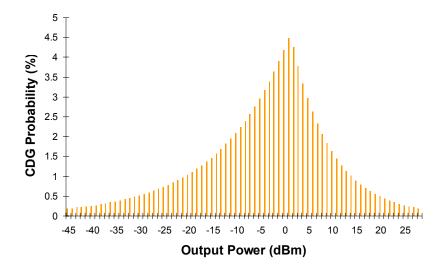

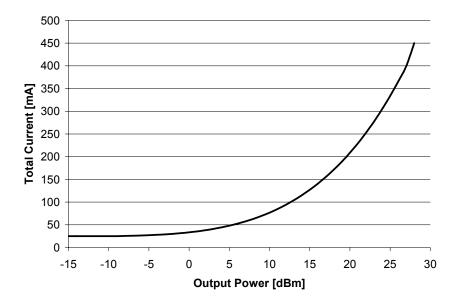

This would be true if the supply voltage was reduced when the amplifier is operating at maximum power. The key to this approach is the variation of the output power with time. The average output power of a PA in a CDMA system, for example, is given as a probability density function provided by the CDMA Development Group (CDG) for both urban and suburban locales. Because of the high population densities of urban locations, this is the more commonly used distribution. This distribution is given in Figure 14.

Figure 14. CDG probability curve for urban operation

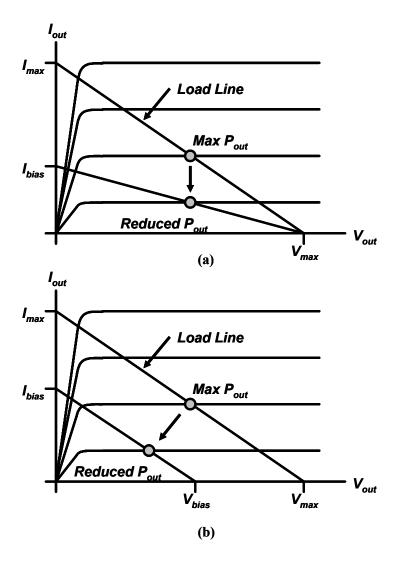

Based on the CDG distributions, it can be seen that the power amplifier is operating at its maximum power quite infrequently. When the PA is not operating at maximum power, the current drawn by the PA is less than the ideal load-line approximation (assuming anything other than class A operation). The efficiency improvement can be viewed in either of two ways. First, if the current is changing and the output match is fixed, then the efficiency is degrading because the load-line condition is not being satisfied. This is illustrated in Figure 15(a). Here the DC bias current is reduced (as in class AB operation) at lower output power. Because the supply voltage is not changing, there is additional headroom in the signal swing that is not being utilized because the load line condition is not met. By reducing the supply voltage as in Figure 15(b), the efficiency is improved by moving the operating point to maintain the original load-line condition, ensuring operation near the peak current and voltage the amplifier is capable of delivering.

Figure 15. Representation of current-voltage characteristics of a power amplifier showing variation of operating point in a class AB amplifier under (a) normal operation and (b) variable supply voltage operation

A second way of viewing the efficiency improvement is to look at the DC power loss component of the efficiency. If power added efficiency (PAE) is defined as

$$PAE = \frac{P_{RFout} - P_{RFin}}{V_{DC} \cdot I_{DC}}$$

(3.2)

then at lower output power, reducing the DC supply voltage directly improves the PAE of the amplifier. This assumes that RF voltage swing is set entirely by the output matching network, which is a valid assumption, given the load-line approximation.

Although the benefits of a variable supply voltage have been addressed in part by several authors [32,33] there still exists a need for a concise, intuitive analysis that can accurately describe the system-level advantages of this approach. Despite the apparent efficiency improvement described above, the true performance advantage of a variable supply voltage using a DC-DC converter is best expressed through the application of the CDG probability curves to the analysis of the battery current drawn from the amplifier.

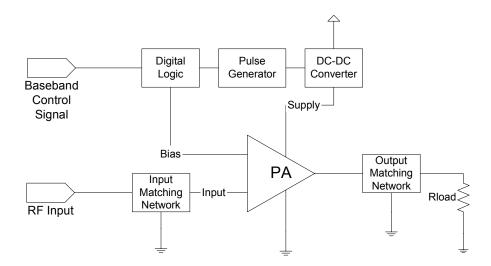

#### 3.4.1 System Architecture

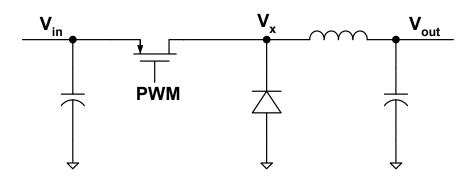

The variable supply voltage is best realized using some type of switching voltage converter. A linear regulator could be used to reduce the supply voltage, but the losses through the regulator would overshadow any efficiency improvements seen in the power amplifier. A switching converter provides high efficiencies over a broad range of load currents and output voltages. The general system architecture of an adaptive power amplifier employing this technique is shown in Figure 16.

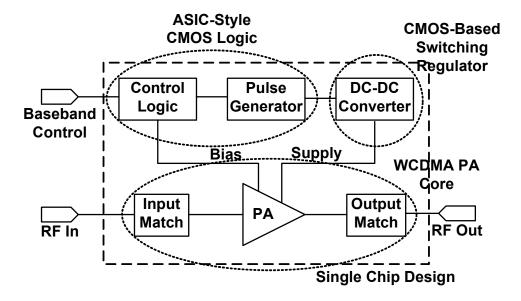

Figure 16. Variable supply voltage power amplifier system architecture

The power amplifier's supply voltage is provided through a DC-DC converter, which is in turn controlled by a power control signal from the baseband processor. This signal adjusts either the bias of the PA, the supply voltage, or both. The supply voltage in the DC-DC converter is controlled by a pulse generator that determines the duty cycle of the switches in the converter. The overall effect is to adjust the operating point and/or supply voltage of the amplifier based on the output power to be transmitted, where adjustments to the bias can be used to maintain a constant gain in the power amplifier, if so desired.

### 3.4.2 Battery Current Analysis

The total battery current drawn by a power amplifier using a variable supply voltage can be analyzed as follows. Assume initially that the amplifier is biased for class AB operation. In this case, the PA will have a low quiescent current at low RF power levels. The current drawn from the battery (I<sub>load</sub>) will then increase linearly with the output power (in Watts) or on a linear-in-dBm scale, it will appear to increase exponentially as in Figure 17.