## COMPILING FOR NUMA PARALLEL MACHINES

A Dissertation

Presented to the Faculty of the Graduate School

of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by Wei Li August 1993

### © Wei Li 1993 ALL RIGHTS RESERVED

# COMPILING FOR NUMA PARALLEL MACHINES

#### Wei Li, Ph.D.

#### Cornell University 1993

A common feature of many scalable parallel machines is non-uniform memory access (NUMA) — data access to local memory is much faster than to non-local memories. In addition, when a number of remote accesses must be made, it is usually more efficient to use block transfers of data rather than to use many small messages. Almost every modern processor is designed with a memory hierarchy organized into several levels – each smaller and faster than the level below. In general, the effective use of parallel machines requires careful attention to the following issues: (1) exposing and exploiting parallelism; (2) accessing local memory instead of remote memory; (3) using block transfers for remote accesses; (4) reusing data in the cache; and (5) load balancing.

We have built a system called *Pnuma* for programming NUMA machines. We make the following contributions: First, we propose a parallelization scheme for both parallelism and data locality. Second, we develop a framework based on *non-singular* matrices and integer lattice theory for the systematic development of loop transformations. Program transformations, such as loop restructuring,

are critical to achieving high performance. The framework can be used in parallelizing compilers for both coarse-grain and fine-grain parallel architectures. We have implemented a loop restructuring tool-kit called *Lambda* based on this framework. Third, using this loop transformation framework, we develop algorithms for improving memory locality. The memory locality algorithm restructures loop nests to expose opportunities for parallel execution and for block transfers, while keeping data accesses local wherever possible. Fourth, for cache locality, we introduce a new simple cache model based on *reuse distances*, which is more precise than the existing *reuse vector space* model. We develop a new loop transformation technique that optimizes directly on reuse distances, so that no exhaustive search is necessary. Fifth, we use our loop transformation framework to improve parallelism as well. We develop a unified algorithm for parallelism, memory locality and cache locality.

System evaluations have been conducted on a multiprocessor machine without cache (BBN GP1000), a uniprocessor workstation with cache (HP 9000/720) and a multiprocessor machine with caches (KSR1), using programs from linear algebra, NASA benchmarks and SIMPLE hydrodynamics benchmark.

To my parents, my sister, Ting, and my teachers

## Acknowledgements

It is a great pleasure to work with my advisor, Professor Keshav Pingali. He has the intuition and insights for solving a problem in a simple way. The Pingalirule, "everything can be reduced to at most 3 points", has helped me always try to understand and tackle a problem from its basics. His intolerance of mediocre research has helped me maintain a decent research standard.

My work would have been impossible without the stimulating and friendly research environment at Cornell. Tom Coleman always found time to listen to my ideas, and helped me learn integer lattice theory. Charlie Van Loan was always happy to answer my questions on matrix computation. His elegant matrix framework for FFT algorithms influenced my work on matrix-based loop transformation framework. Steve Vavasis, Keith Marzullo and Anil Nerode are very kind to have served on my committee. Juris Hartmanis provided guidance and understanding.

I have benefited from discussions with Danny Ralph, Radha Jagadeesan, and Shirish Chinchalkar. My work have been improved by the comments from Micah Beck, Mark Charney, Richard Huff, Richard Johnson, Mayan Moudgill, Anne Rogers, and Paul Stodghill. Sudeep Gupta, Scott DeVine and Nikos Pitsianis helped implement part of Pnuma. Paul Stodghill has been a wonderful

officemate for the past two years. He helped in the implementation of an earlier version of the compiler. Richard Huff deserves special thanks for his helpful comments on my papers and my talks. Paul, Sudeep, and Shirish carefully read my thesis draft and provided invaluable comments. I would like to thank Charlie DeVine, Anne Elster, Doug Ierardi, Aiping Liao, Yuying Li, Shmuel Onn, Eva Tardos, Mike Todd, Leslie Trotter, Zhijun Wu, Wei Yuan for listening to my ideas, and patiently answering my random questions.

Helene Croft provided great support for ACRI. Cindy Robinson was always willing to help. Anne Gockel provided excellent systems support.

I will miss the exciting games of badminton, bridge, tennis and volleyball at Cornell. Jiaqi Luo has been a perfect bridge partner. Anil Pannikkat has improved my badminton skills by playing with me. Thomas Bressoud organized the weekly CS/OR volleyball games.

It is impossible to enumerate all the friends I would like to thank. Finally, I would like to thank Ting for her friendship and company during all these years.

During my stay at Cornell, I was supported by a McMullen Fellowship from Cornell University, assistantships from Cornell, and a grant from Hewlett-Packard.

## Table of Contents

| 1 | Intr | roduction                                    | 1               |

|---|------|----------------------------------------------|-----------------|

|   | 1.1  | Motivation                                   | 1               |

|   | 1.2  | Thesis Overview                              | 2               |

|   | 1.3  | Organization                                 | 5               |

| 2 | Ger  | neration of Parallel Code                    | 6               |

|   | 2.1  | Introduction                                 | 6               |

|   | 2.2  | Locality-driven Loop Parallelization         | 6               |

|   |      | 2.2.1 Data Distribution                      | 6               |

|   |      | 2.2.2 Computing Distributed Loops            | 7               |

|   | 2.3  | Localizing Data Accesses                     | 9               |

|   | 2.4  | Discussion and Related Work                  | 11              |

| 3 | A L  | coop Transformation Theory                   | 12              |

|   | 3.1  | Introduction                                 | 12              |

|   | 3.2  | Linear Loop Transformations                  | 13              |

|   |      | 3.2.1 Iteration Spaces and Integer Lattices  | 13              |

|   |      | 3.2.2 Loop Transformations                   | 14              |

|   |      | 3.2.3 Generating Code                        | 17              |

|   | 3.3  | Difficulties in Generating Code              | 18              |

|   |      | 3.3.1 Computing Image of Bounds              | 18              |

|   |      | 3.3.2 Dense Spaces                           | 21              |

|   |      | 3.3.3 Discussion                             | 21              |

|   | 3.4  | Algorithm for Code Generation                | 21              |

|   |      | 3.4.1 Auxiliary Iteration Space              | 22              |

|   |      | 3.4.2 Target Iteration Space                 | 25              |

|   |      | 3.4.3 Sparse Source Iteration Space          | 27              |

|   | 3.5  | Data Dependences                             | 28              |

|   |      | 3.5.1 A Dependence Algebra                   | $\frac{-5}{28}$ |

|   |      | 3.5.2 Legality of $\Lambda$ -transformations | $\frac{20}{30}$ |

|   | 3.6  | Discussion and Related Work                  | 30              |

| $\mathbf{Tr}$ | ansformations for Memory Locality |

|---------------|-----------------------------------|

| 4.1           | Introduction                      |

| 4.2           | Pata Access Matrix                |

| 4.3           | Non-singular Data Access Matrices |

| 4.4           | Singular Data Access Matrices     |

|               | 4.4.1 Basis Matrix                |

|               | 4.4.2 Padding Matrix              |

| 4.5           | Data Dependences                  |

|               | 4.5.1 Generating a Legal Basis    |

|               | 4.5.2 Legal Padding Matrix        |

| 4.6           | Completion Algorithm              |

|               | 4.6.1 Completion Procedure        |

|               | 4.6.2 Discussion                  |

| 4.7           | 1 1                               |

|               | 4.7.1 The Machine Architecture    |

|               | 4.7.2 GEMM                        |

|               | 4.7.3 SYR2K                       |

| 4.8           | B Discussion and Related Work     |

| т.            |                                   |

|               | ansformations for Cache Locality  |

| 5.1           |                                   |

| 5.2           | 1                                 |

|               | 5.2.1 Reuse Vectors               |

|               | 5.2.2 Reuse Distance              |

|               | 5.2.4 Discussion                  |

| 5.3           |                                   |

| ე.ე           | 0                                 |

|               | 0 0                               |

|               | 5.3.2 Dependences                 |

| 5.4           | O                                 |

| 5.4           |                                   |

| 5 5           |                                   |

| 5.5           | 5.5.1 The Machine Architecture    |

|               | 5.5.2 Banded SYR2K Results        |

|               | 5.5.3 NASA Benchmark Results      |

|               | 5.5.4 The Effect of Data Sets     |

|               |                                   |

| F 0           | 5.5.5 The Effect of Tiling        |

| ാമ            | ) Discussion and Kelated Work     |

| 6            | Imp   | roving Parallelism and Locality                  | <b>78</b> |

|--------------|-------|--------------------------------------------------|-----------|

|              | 6.1   | Introduction                                     | 78        |

|              | 6.2   | Dependence Summary Vector                        | 78        |

|              | 6.3   | Transformation for Parallelism                   | 79        |

|              | 6.4   | A Unified Algorithm for Parallelism and Locality | 80        |

|              | 6.5   | Experiments on Multiprocessor with Caches: KSR1  | 81        |

|              |       | 6.5.1 The Machine Architecture                   | 81        |

|              |       | 6.5.2 Cholesky Decomposition                     | 83        |

|              |       | 6.5.3 SIMPLE Benchmark Results                   | 84        |

|              | 6.6   | Discussion and Related Work                      | 84        |

| 7            | Con   | clusions                                         | 86        |

| $\mathbf{A}$ | Pnu   | ma Compiler                                      | 88        |

| В            | Lan   | nbda Transformation Toolkit                      | 89        |

|              | B.1   | Introduction                                     | 89        |

|              | B.2   | Data Dependences                                 | 89        |

|              |       | B.2.1 Data Types                                 | 89        |

|              |       | B.2.2 Routines                                   | 90        |

|              | B.3   | Constructing Transformations                     | 91        |

|              |       | B.3.1 Data Types                                 | 91        |

|              |       | B.3.2 Nonsingularity                             | 92        |

|              |       | B.3.3 Data Dependences                           | 92        |

|              | B.4   | Code Restructuring                               | 93        |

|              |       | B.4.1 Computing Loop Bounds                      | 93        |

|              |       | B.4.2 Computing Loop Body                        | 95        |

|              | B.5   | Utility Routines                                 | 95        |

| Bi           | bliog | graphy                                           | 96        |

## List of Tables

| 5.1 | NASA benchmark on HP 9000/720                       | 73 |

|-----|-----------------------------------------------------|----|

| 5.2 | Loop Tiling (Size 1000)                             | 76 |

| 5.3 | Loop Tiling after Height Reduction (Size 1000)      | 76 |

| 6.1 | KSR1 Memory Hierarchy                               | 82 |

| 6.2 | Cholesky Decomposition on KSR1 (time unit = second) | 84 |

| 6.3 | SIMPLE on KSR1 (Size=400)                           | 84 |

# List of Figures

| 1.1  | Pnuma System Overview                                      |

|------|------------------------------------------------------------|

| 2.1  | Access Set Operators                                       |

| 2.2  | Computing Distribution Expressions                         |

| 2.3  | Distributing loops among processors                        |

| 2.4  | Computing a special solution                               |

| 3.1  | The working example                                        |

| 3.2  | Primitive Transformations                                  |

| 3.3  | Primitive Transformations (Cont.)                          |

| 3.4  | Dense Iteration Space                                      |

| 3.5  | Computing the Hermite form                                 |

| 3.6  | Computing the loop bounds                                  |

| 3.7  | Operators for Directions                                   |

| 4.1  | Transformation and Code Generation for a Simple Example 33 |

| 4.2  | The running example                                        |

| 4.3  | A loop nest with a singular data access matrix             |

| 4.4  | Computing a Basis Matrix                                   |

| 4.5  | Computing a Padding Matrix                                 |

| 4.6  | Algorithm LegalBasis: Computing a Legal Basis Matrix 41    |

| 4.7  | Legal basis and padding matrices                           |

| 4.8  | Extending Partial Transformation by Projection             |

| 4.9  | Computing a Legal Full Transformation (first part) 47      |

| 4.10 | Computing a Legal Full Transformation (second part) 47     |

| 4.11 | GEMM                                                       |

| 4.12 | GEMM (cont.)                                               |

| 4.13 | SYR2K                                                      |

| 4.14 | SYR2K (cont.)                                              |

| 5.1  | A Simple Example                                           |

| 5.2  | Reuse Distances                                            |

| 5.3  | Comparison of Models                                       |

| 5.4  | Height Reduction                                           |

| 5.5  | Loop Tiling                            | 7 |

|------|----------------------------------------|---|

| 5.6  | Width Reduction                        | 8 |

| 5.7  | Banded SYR2K                           | 0 |

| 5.8  | Width Reduction- banded rank-2k Update | 1 |

| 5.9  | Matrix Multiplication                  | 4 |

| 5.10 | Cholesky Decomposition                 | 5 |

| 6.1  | Improving Parallelism                  | 0 |

| 6.2  | Improving Parallelism and Locality     | 1 |

| 6.3  | Cholesky Decomposition on KSR          | 3 |

## Chapter 1

### Introduction

#### 1.1 Motivation

There is a wide range of applications that may find parallel machines useful. They come from areas such as linear programming, matrix algebra, computational physics, financial modeling, weather and climate modeling, electromagnetic fields simulation, and numerical aerodynamic simulation [CVL88, EA87,MFL<sup>+</sup>92].

Scalable parallel machines are often organized as networks of processor-memory pairs; examples of such machines are the BBN Butterfly, the Kendall Square Research KSR1, and multi-computers like the Intel iPSC/i860. These machines are called non-uniform memory access (NUMA) machines because a processor can access data in its local memory ten to a thousand times faster than it can access non-local data. For example, in the Kendall Square Research "all-cache" machine, accesses to local memory take 18 cycles, while accesses to non-local memory take 175 cycles [Ken91]. Distributed memory machines like the Intel iPSC/i860 have even greater non-uniformity in access times because access to non-local data must be orchestrated through the exchange of messages [Int91]. If non-local accesses are on the critical path through a program, making these accesses local through proper data management will speed up program execution.

Almost every modern processor is designed with a memory hierarchy organized into several levels – each smaller, faster and more expensive than the level below. Typically, a cache hit takes only one cycle, while a cache miss takes 8-32 cycles [HP90]. Therefore, for good performance, programs must possess cache locality.

In general, the effective use of parallel machines requires careful attention to the following issues.

• Parallelism: Unless the algorithm underlying a program has lots of parallelism, it is pointless to run the code on a parallel machine. Moreover,

the compiler must be able to expose and exploit this parallelism.

- Memory Locality: Scalable high-performance machines are built as interconnections of processor-memory pairs in which a processor can access its local memory ten to a thousand times faster than non-local memory. Therefore, proper data management to maximize local accesses is essential.

- Block transfers: Communication between processors can be viewed as a pipelined process in which the start-up time is large compared to the time to transfer a unit of data. Therefore, when non-local accesses must be made, it is more efficient to use a single block transfer of data rather than many individual transfers.

- Cache Locality: Each node of a multiprocessor may have data cache that is much faster than memory. Cache locality techniques can be applied to uniprocessors, since almost every modern uniprocessor has a cache. Programs are required to have data locality to achieve high performance.

- Load balancing: It is important to avoid swamping a few processors with work when other processors are idle.

#### 1.2 Thesis Overview

We have built a system called *Pnuma* for programming NUMA machines. Pnuma takes programs written in FORTRAN extended with data distribution information and generates code for parallel machines such as the KSR1 and the BBN Butterfly. The system can also produce uniprocessor code optimized for cache locality.

In the traditional approach to parallelization (pioneered by the Cedar project at Illinois), iterations of the loops in a loop nest are distributed among the processors. Synchronization instructions are introduced to take care of dependences between "iterations". To reduce the amount of synchronization, transformations like loop interchange are performed to move parallel loops outermost [MP87, Pol89]. This 'outside-in' strategy is simple but it does not perform any data management, and may result in many non-local accesses during the execution of the loop nest.

A different approach to compiling is to generate code 'inside-out' using the so-called ownership rule — the owner of the variable on the left-hand side of an assignment statement is responsible for computing the expression on the right-hand side. A processor executes a loop iteration if it has any work to do in the body for that iteration. Although this strategy takes data mappings into account, code generation is very complex, compared to the traditional approach,

and the code generated can be very inefficient if the structure of the loop nest does not match the data distribution [RP89,HKT91].

This thesis makes the following contributions:

- We propose a parallelization scheme based on both parallelism and data locality. Loop iterations are distributed according to parallelism and locality. We use data distribution information to drive our loop transformation strategy. Once a loop nest has been transformed for parallelism and data locality, we can generate code by distributing outermost parallel loop iterations among the processors. Data accesses in the resulting code are local wherever possible, and non-local accesses are performed using block transfers if possible.

- We develop a framework based on non-singular matrices and integer lattice theory for the systematic development of loop transformations. Program transformations, such as loop restructuring, are critical to achieving high performance. The main benefit of this framework is that it provides an approach to tackling the so-called 'phase-ordering problem' for many problems where there is no obvious order in which the transformations should be performed, it is often possible to generate a non-singular matrix from which the desired order of loop transformations can be determined easily. This framework can be used in parallelizing compilers for MIMD machines as well as in compilers for fine-grain parallel architectures such as VLIW and superscalar machines. This framework is more general than the unimodular loop transformation framework [Ban90,WL91b]. We have implemented a loop restructuring toolkit called Lambda based on this framework.

- Using this loop transformation framework, we develop algorithms for improving both memory locality. The memory locality algorithm called access normalization restructures loop nests to expose opportunities for parallel execution and for block transfers, while keeping data accesses local wherever possible. Loop restructuring is followed by a code generation phase that generates parallel code and makes use of block transfers.

- For cache locality, we introduce a new simple cache model based on reuse distances, which is more precise than the existing reuse vector space model [WL91a]. We develop a new loop transformation technique that optimizes directly on reuse distances, so that no exhaustive search is necessary.

- We use our loop transformation framework to improve parallelism as well. Furthermore, we develop a unified algorithm for parallelism, memory locality and cache locality.

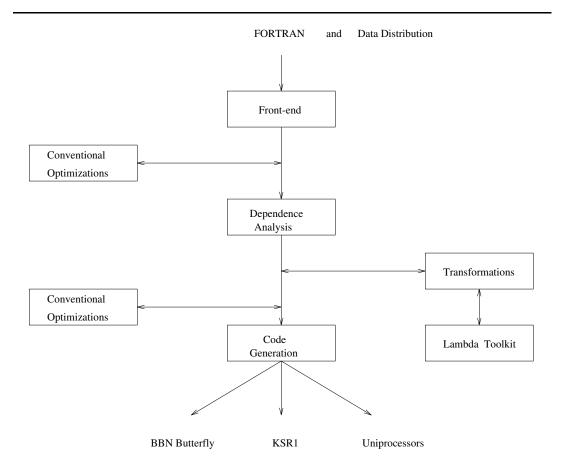

Figure 1.1: Pnuma System Overview

Pnuma has been evaluated on a multiprocessor without cache, a uniprocessor workstation with cache and a multiprocessor with caches. Experiments were conducted on BBN GP1000, HP 9000/720 and KSR1 using programs from linear algebra, the NASA benchmarks, and the SIMPLE hydrodynamics benchmark.

The individual modules in the Pnuma system are shown in Figure 1.1. A front-end from SIGMA [GJG88] is used to generate abstract syntax trees with data dependence information from FORTRAN programs. Access normalization matches code and data distributions to exploit both parallelism and memory locality. As an added bonus, access normalization exposes opportunities for block transfers of data. For uniprocessor machines, programs are transformed to improve data reuse. For NUMA architectures, programs are transformed to improve parallelism and data locality. We generate parallel FORTRAN for the KSR1, parallel C code for the BBN Butterfly, and optimized FORTRAN for uniprocessor, respectively.

The Lambda toolkit is the implementation of our loop transformation theory.

The toolkit has been integrated with Parascope, the parallelizing environment from Rice University [BP93].

### 1.3 Organization

The rest of the thesis is organized as follows: in Chapter 2, we describe the locality-driven code generation scheme. We introduce the loop transformation theory in Chapter 3.

The transformation construction algorithms for memory locality are developed in Chapter 4 with the experimental results from a BBN GP1000, which is a multiprocessor machine without caches. Then we develop a cache locality model, and optimization algorithms in Chapter 5 with experimental results from an HP 9000/720, which is a uniprocessor with data cache. The algorithm to improve parallelism, memory and cache locality is presented in Chapter 6 with experimental results from a KSR1, which is a multiprocessor machine with caches.

We conclude, and point out future work in Chapter 7. A brief description of the Pnuma compiler is included in Appendix A, and the implementation of the loop transformation framework called the *Lambda* toolkit is included in Appendix B.

## Chapter 2

### Generation of Parallel Code

#### 2.1 Introduction

There are two ways of generating parallel code from a sequential program. One way is *control-driven*, i.e. distribute iterations of a loop among the processors. If the loop is a DOALL loop, then no synchronization is needed. Otherwise, synchronization instructions are introduced to take care of dependences carried by this loop, called a DOACROSS loop [MP87,Pol89]. This approach is simple, and has a clean process decomposition, but since it was designed for uniform memory access machines, it does not take data locality into account.

A different approach is data-driven, i.e. generate code using the ownership rule — the owner of the variable on the left-hand of an assignment statement is responsible for computing the expression on the right-hand side. A processor executes a loop iteration if it has any work to do in the body for that iteration. Although this strategy takes data mappings into account, code generation is very complex, compared to the traditional approach, and the code generated can be very inefficient if the structure of the loop nest does not match the data distribution [RP89,HKT91].

Our approach combines the simplicity of the control-driven approach and the locality sensitivity of the data-driven approach.

### 2.2 Locality-driven Loop Parallelization

In this section, we first define the data distributions we support, then present our parallelization scheme.

#### 2.2.1 Data Distribution

Our compiler accepts programs written in FORTRAN extended with data distribution declarations that specify how arrays are to be distributed across the

local memories of the machine. We support most of the data distributions commonly used by programmers of NUMA machines, such as wrapped and blocked column and row distributions. In a wrapped column distribution, the columns of an array are distributed in a round-robin fashion to the processors. If P is the number of processors, then processor 0 gets columns 0, P, 2P and so on, while processor 1 gets columns 1, P+1, 2P+1, etc. Most of the examples in this paper use a wrapped column distribution. Blocked column distribution is similar, except that a processor gets a contiguous set of columns.

Data distributions can be specified precisely using a distribution function.

**Definition 2.2.1** A distribution function is a function from array indices to integers between 0 and P-1, where P is the number of processors in the machine. An array dimension is a distribution dimension, if that dimension is used in the distribution function for the array. The expression in a distribution dimension is called distribution expression.

For example, the distribution function for the wrapped column distribution of a two dimensional array is  $W_2(i,j) = j \mod P$ , the second dimension of the array is a distribution dimension, and the expression in the second dimension is the distribution expression.

#### 2.2.2 Computing Distributed Loops

Our scheme parallelizes the outermost parallel loops that carry data locality.

**Definition 2.2.2** A loop *carries* a distribution expression e, if e is a function uniquely defined by the loop index variable.

For example, in a loop nest with loops i and j, the distribution expression i + j is carried by loop j but not loop i, since i is a loop invariant in loop j.

A loop may carry multiple expressions. We use a heuristic to decide a unique expression for a loop, and this expression is used in section 2.3 to generate the parallel code if the loop is decided to be parallelized.

The algorithm in Figure 2.2 computes the distribution expressions carried by loops in a loop nest. Let J be the loop index vector of the loop nest. The Access set is a set of distribution expressions with three attributes: level, weight, block. level is the nesting level of the loops; weight is the number of occurrences; and block indicates whether this is a wrapped or blocked distribution. If t is a distribution expression, then t.l, t.w and t.b to represent the attributes level, weight and block respectively. Two expressions can be compared by the lexicographical order of (t.l, t.w). Two set operations, union  $(\uplus)$  and intersection  $(\boxtimes)$ , on access sets are defined in Figure 2.1.

$$S_1 \uplus S_2 = \{t : t \in S_1, t \in S_2, t.b_1 = t.b_2\}.$$

- t.b = t.b1;

- if (t.l1 > t.l2) t.l = t.l1, t.w = t.w1;

- if (t.l1 < t.l2) t.l = t.l2, t.w = t.w2;

- if (t.l1 = t.l2) t.l = t.l1, t.w = t.w1 + t.w2;

$$S_1 \otimes S_2 = \{t : t \in S_1, t \in S_2, t.b1 = t.b2\}.$$

- t.b = t.b1;

- if (t.l1 > t.l2) t.l = t.l1, t.w = t.w1;

- if (t.l1 < t.l2) t.l = t.l2, t.w = t.w2;

- if (t.l1 = t.l2) t.l = t.l1, t.w = max(t.w1, t.w2);

Figure 2.1: Access Set Operators

```

= \emptyset

Access(x)

Access(A[..., f(J),...])

= \{ f(J) \text{ with level} = 0, \text{ weight} = 1 \}

Access(Exp1 op Exp2)

= Access(Exp1) \uplus Access(Exp2)

Access(Var := Exp)

= Access(Exp) \uplus Access(Var)

Access(S1; S2)

= Access(S1) \uplus Access(S2)

Access(if Exp then S1 else S2)

= Access(Exp) \uplus (Access(S1) \otimes Access(S2))

Access(for i=l,u do S)

= choose the expression carried by i-loop

with the highest (t.l, t.w) from Access(S);

return Access(S) deleting expressions

carried by the loop.

```

Figure 2.2: Computing Distribution Expressions

$$\begin{array}{ll} for \ i=l, \ u & for \ i=l, \ u, \ step \ s \\ \\ \text{(a) unit step} & \text{(d) non-unit step} \\ \\ for \ i=\lceil \frac{l-p}{P} \rceil * P+p, & for \ i=l+n_0*s, \\ u, & u, \\ step \ P & step \ P/(P,s)*s \end{array}$$

(b) task p for wrapped distribution (e) task p for wrapped distribution

for

$$i = max(l, p * S)$$

,

$min(u, (p+1) * S - 1)$  for  $i = max(l, p * S)$ ,

$min(u, (p+1) * S - 1)$ ,

$step s$

(c) task p for blocked distribution (f) task p for blocked distribution

Figure 2.3: Distributing loops among processors

### 2.3 Localizing Data Accesses

After the distribution expressions are computed, we must generate the code that will run on each processor. We generate the same code for each processor, but this code is parameterized by the processor number so that each processor does only the work for which it is responsible.

First, consider a loop with step size 1 (Figure 2.3(a)). For a wrapped distribution, processor p owns the data segments p, p + P, p + 2P, .. etc, where a data segment is a column in the wrapped column distribution or a row in the wrapped row distribution. Since the iterations that access the data segments on processor p are assigned to processor p, it is easy to verify that the iterations executed by processor p are the ones shown in Figure 2.3(b). The lower bound  $\lceil \frac{l-p}{P} \rceil * P + p$  is the first iteration between l and u that belongs to process p. For a blocked mapping, the corresponding iterations are shown in Figure 2.3(c).

When the step size is not 1 (Figure 2.3(d)), we must solve a linear congruence for the wrapped distribution. Assume that the step size is positive, since the solution can be easily extended to handle the case when the step size is negative. The iterations can be represented by i = l + n \* s where n is a parameter with integer values. The iterations that belong to process p are those satisfying the equation  $l + n * s = p \pmod{P}$ . Using results from number theory, we know

```

Input: An equation l + n * s = p \pmod{P}.

Output: A special solution 0 \le n_0 < P.

Algorithm Asolution(l, s, p, P : Integer): Integer

begin

if gcd(s, P) doesn't divide (p-l) then no solution;

s_0 = s \mod P;

c_0 = (p - l) \mod P;

/* solve n * s_0 = c_0 \pmod{P} */

c = c_0;

while (s_0 doesn't divide c)

c = c + P;

n_0 = c/s_0;

return(n_0);

end

```

Figure 2.4: Computing a special solution

that the when the g.c.d. of s and P, written as (s, P), divides (l-p), there is an infinite number of solutions in the form of  $n = n_0 + t * P/(s, P)$  for some integer solution  $0 \le n_0 < P/(s, P)$  and integer free variable t. However, only certain t's are solutions for the iterations within the loop bounds. Since  $l \le i \le u$  and  $i = l + (n_0 + t * P/(s, P)) * s$ , the range of t is  $\lceil \frac{-n_0}{P/(s, P)} \rceil = 0 \le t \le \lfloor \frac{u - l - n_0 * s}{P/(s, P) * s} \rfloor$ . Therefore the bounds of the loop for processor p are in Figure 2.3(e). The remaining question is how to compute the special solution  $n_0$ . This can be done by the algorithm in Figure 2.4. The equation  $s_0 n = c_0 \pmod{P}$  has the same solutions as  $l + s * n = p \pmod{P}$ . If there is any solution to the equation  $s_0 n = c_0 \pmod{P}$  then there is unique solution within [0, P/(s, P)) [HW79]. The algorithm finds that solution. For the blocked distribution, the resulting bounds of the loop for processor p are shown in Figure 2.3(f).

For multi-dimensional block distribution, we need to distribute multiple loops (loop tiling). For example, an  $n \times n$  array A has a subblock distribution where each subblock is of size  $b \times b$ . Imagine that the processor names are also two dimensional. Then the element A[i,j] is owned by processor (i/b,j/b). If A has more complicated subscripts or the subscripts are not the loop indices of the two outermost loops, access normalization will attempt to normalize the reference to A[u,v] with u and v as the outermost loops.

Given this assignment of iterations to processors, we must generate synchronization instructions to take care of dependences carried by the outermost loop, and insert block transfers wherever possible. These steps are routine [ZC90], and are omitted.

#### 2.4 Discussion and Related Work

In this chapter, we have discussed the locality driven loop scheduling scheme.

Previous work has been focused on trying load balancing and reducing synchronization. A simple scheduling scheme is the dynamic self scheduling scheme proposed by Tang and Yew [TY86]. A central work queue of iterations is maintained. Idle processors will remove iterations from the work queue until it is empty. This scheme achieves very good load balancing, since the granularity of the work unit is one iteration. However, the overhead of maintaining the central queue is high. Various other schemes have been proposed to improve upon it. Guided self-scheduling by Polychonopoulos [Pol88] schedules a chuck of iterations at a time, where the chuck size depends on the number of iterations left in the queue and the total number of processors. Other scheduling algorithms include Adaptive guided scheduling by Eager and Zahorjan [EZ92]. Unfortunately, none of the above algorithms address data locality. The tradeoff between load balancing and locality has been studied by Markatos and LeBlanc [ML92], who showed that locality is more important than load balancing.

## Chapter 3

## A Loop Transformation Theory

#### 3.1 Introduction

The importance of loop transformations in generating good code for vector and parallel machines is widely recognized [PW86,AK87,Wol89]. A recent advance in this area is the use of unimodular matrices to model three important loop transformations — permutation, skewing and reversal. Unimodular matrices have integer entries and a determinant that is 1 or -1; therefore, they are closed under matrix product. It follows that any sequence of these loop transformations can also be represented as a unimodular matrix; conversely, any unimodular matrix can be interpreted as representing a sequence of permutation, skewing and reversal transformations. The main benefit of the unimodular abstraction is that it provides an approach to tackling the so-called 'phase-ordering problem' — for many problems where there is no obvious order in which the transformations should be performed, it is often possible to generate a unimodular matrix from which the desired order of loop transformations can be determined easily. Banerjee has used this framework to address the problem of generating parallel loops [Ban90]; Wolf and Lam have used this framework extensively to address both this problem and that of promoting data reuse for improving cache performance [WL91a, WL91b].

In this chapter, we propose to use non-singular matrices, rather than unimodular matrices, as a foundation for modeling loop transformations. Nonsingular matrices include unimodular matrices as a special case, and permit us to include a new transformation called *loop scaling* in this framework. Surprisingly, code generation is somewhat more intricate for non-singular matrices than for unimodular matrices, and it is the main concern of this chapter.

Another advantage of our approach is that it is easier to generate non-singular matrices than it is to generate unimodular matrices. A typical algorithm that uses the matrix framework, such as the generation of parallel outermost loops [Ban90] or the exploitation of locality in NUMA architec-

tures [LP93a], determines the first few rows of the matrix, and then 'pads out' the remaining rows to generate a matrix that represents a legal transformation. It is easier to generate a non-singular matrix than a unimodular matrix since there are fewer constraints to be satisfied, and in Chapter 4, we give a completion procedure that produces a non-singular matrix, given the first few rows. This completion procedure is non-trivial since we must ensure that the result matrix respects the dependencies of the loop nest.

The rest of the chapter is organized as follows. In Section 3.2, we define the problem formally, outline our loop restructuring framework and discuss the difficulties in generating the transformed loop nest. In Section 3.3, we sketch the code generation technique for the case of unimodular matrices, and discuss why it cannot be used directly for non-singular matrices. In Section 3.4, we solve the code generation problem for non-singular matrices. The key technical result is that a non-singular matrix can be decomposed into the product of a lower triangular matrix with positive diagonal elements and a unimodular matrix. Using these two matrices, we generate the transformed loop nest. The last section discusses related work.

### 3.2 Linear Loop Transformations

In this section, we introduce integer lattices as a model of the iteration space of loops, and non-singular matrices as a model of loop transformations.

#### 3.2.1 Iteration Spaces and Integer Lattices

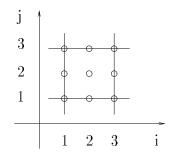

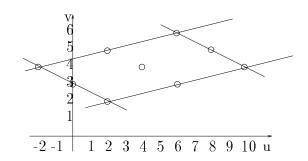

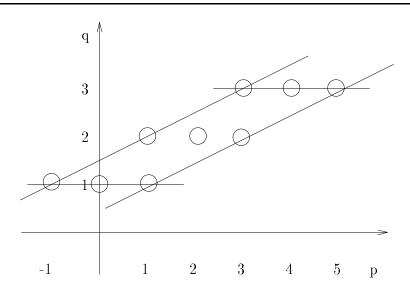

Consider the loop nest in Figure 3.1(a) whose iteration space is shown in Figure 3.1(c). The points in the iteration space of this loop can be modeled as integer vectors in the two dimensional space  $\mathbb{Z}^2$ , where  $\mathbb{Z}$  is the set of integers. For example, the iteration (i=2,j=3) can be represented by the vector (2,3). In general, points in the iteration space of a loop nest of depth n can be represented by integer vectors from the space  $\mathbb{Z}^n$ . It is convenient to use the theory of integer lattices [Cas59] and view the points in the iteration space as being generated by integral linear combinations of a set of basis vectors. For example, it is easy to see that the points in the iteration space shown in Figure 3.1(c) can be generated by integral linear combinations of two integer vectors  $\begin{pmatrix} 0 \\ 1 \end{pmatrix}$  and  $\begin{pmatrix} 1 \\ 0 \end{pmatrix}$ . Similarly, the iteration space in Figure 3.1(d) is generated by linear combinations of the integer vectors  $\begin{pmatrix} -2 \\ 1 \end{pmatrix}$  and  $\begin{pmatrix} 4 \\ 1 \end{pmatrix}$ .

For future reference, we define these concepts more precisely.

**Definition 3.2.1** Let  $a_1, a_2, ..., a_m$  be a set of linearly independent integer vectors. The set  $\Lambda = \{\lambda_1 a_1 + \lambda_2 a_2 + ... + \lambda_m a_m \mid \lambda_1, ..., \lambda_m \in \mathbb{Z}\}$  is called an integer lattice generated by the basis  $a_1, a_2, ..., a_m$ .

We will call an integer matrix a basis matrix, if its columns are a basis.

The loop nest in Figure 3.1(a) has the property that every integer point within the loop bounds is a point in the iteration space of the loop nest. We will call this a *dense* iteration space. By contrast, Figure 3.1(d) shows a *sparse* iteration space because the integer point (2, 3), for example, is within the loop bounds but does not represent a point in the iteration space of the loop. The notion of *dense* and *sparse* can be formally defined as follows.

**Definition 3.2.2** An iteration space is *dense*, if for any two integer vectors  $v_1$  and  $v_2$  representing loop iterations, any integer vector  $v_3 = \lambda v_1 + (1 - \lambda)v_2$  for some  $0 \le \lambda \le 1$  also represents a loop iteration. An iteration space is *sparse* if it is not dense.

The significance of this classification of iterations spaces is that it is considerably more difficult to generate code for a loop nest if the iteration space is sparse, than if it is dense, as we will show in Section 3.3.

Let  $e_i$  be an *n*-dimensional vector with 1 in the *i*th entry and 0 elsewhere.

**Theorem 3.2.1** The integer vectors from a n-dimensional dense iteration space form an integer lattice with the basis  $e_1, e_2, \dots e_n$ .

**Proof:** Obvious. □

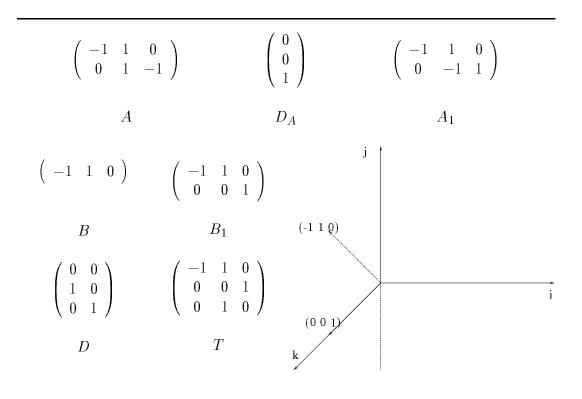

#### 3.2.2 Loop Transformations

We will focus on transformations that can be represented by linear, one-to-one mappings from the iteration space of the source program to the iteration space of the target program. This class of transformations includes permutation, skewing and reversal, as well as a new transformation called *scaling*. Examples of these transformations are shown in Figure 3.2. These transformations are standard except for scaling which corresponds to replacing a loop iteration variable by an integer multiple of it. Loop scaling gives the ability to transform sparse iteration spaces, which is important in iteration space tiling. For example, if a two dimensional iteration space is partitioned into  $2 \times 2$  tiles, each tile can be represented by its bottom-left corner. The space of these representatives is a sparse space, and it can be viewed as the result of loop scaling by a factor of 2. Loop scaling is also useful in *access normalization* [LP92] which is a loop transformation for improving data locality.

Linear, one-to-one mappings between iteration spaces can be modeled using integer, non-singular matrices. The reader can verify that the matrices shown in Figure 3.2 perform the desired mappings from the source iteration space to the target iteration space, and are integer and non-singular. Similarly, in Figure 3.1(d), the points in the target iteration space are the image of the source iteration space points under the integer, non-singular matrix  $T = \begin{pmatrix} -2 & 4 \\ 1 & 1 \end{pmatrix}$ .

for

$$i = 1, 3$$

for  $j = 1, 3$

$A[4j-2i+3, i+j] = j;$

(a) The original code

(c) The original iteration space

$$\begin{array}{ccc} 1 \leq & i & \leq 3 \\ 1 \leq & j & \leq 3 \end{array}$$

(e) Loop Bounds

(b) The target code

(d) The target iteration space

$$-2 \le u \le 10$$

$$max((u+6)/4, (6-u)/2) \le v$$

$$v \le min((u+18)/4, (18-u)/2)$$

(f) Image of Bounds

Figure 3.1: The working example

for

$$i = 1, 3$$

for  $j = 1, 3$

$A[i, 2j] = j$

The original loop nest

$$\begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix} \qquad \begin{array}{c} \textit{for } u = 1, \ 3 \\ \textit{for } v = 1, \ 3 \\ \textit{A/v}, \ 2u \ | = u \end{array}$$

(a) loop interchange

$$\begin{pmatrix} 1 & 0 \\ 0 & -1 \end{pmatrix} \qquad \qquad \begin{array}{l} for \ u = 1, \ 3 \\ for \ v = -3, \ -1 \\ A[u, \ -2v] = -v \end{array}$$

(b) loop reversal

Figure 3.2: Primitive Transformations

$$\begin{pmatrix} 1 & 0 \\ 1 & 1 \end{pmatrix} \qquad \qquad \begin{array}{c} for \ u = 1, \ 3 \\ for \ v = u+1, \ u+3 \\ A[u, \ 2(v-u)] = v-u \end{array}$$

(c) loop skewing

$$\begin{pmatrix} 1 & 0 \\ 0 & 2 \end{pmatrix} \qquad \begin{array}{c} \textit{for } u = 1, \ 3 \\ \textit{for } v = 2, \ 6, \ 2 \\ A[u, \ v] = v/2 \end{array}$$

(d) loop scaling

Figure 3.3: Primitive Transformations (Cont.)

**Definition 3.2.3** A loop transformation is called a  $\Lambda$ -transformation if it can be modeled by an integer non-singular matrix.

Performing a sequence of transformations corresponds to composing the mappings between iteration spaces, which, in turn, can be modeled as the product of the matrices representing the individual transformations. Since the product of any number of integer, non-singular matrices is integer and non-singular, it follows that the set of  $\Lambda$ -transformations is closed under composition.

Conversely, we can show that the transformation represented by any integer non-singular matrix can be viewed as a composition of the four basic transformations. More precisely, we have the following result.

**Theorem 3.2.2** The transformation represented by any integer non-singular matrix can be viewed as a composition of permutation, skewing, reversal and scaling.

**Proof:** By applying the appropriate elementary row and column operations, an integer non-singular can be reduced to a diagonal matrix. The elementary operations can be represented by multiplying interchange, reversal and skewing matrices on the left hand side and on the right hand side the non-singular matrix. The diagonal matrix can be further reduced to a product of scaling matrices.  $\Box$

As mentioned earlier, unimodular transformations are the subset of non-singular transformations without loop scaling. An important property of unimodular transformations is the following.

**Theorem 3.2.3** Unimodular transformations map a dense (sparse) iteration space to another dense (sparse) iteration space.

**Proof:** The lattice remains the same, since only the basis is changed.  $\Box$

#### 3.2.3 Generating Code

To generate code for the target loop nest, we must generate DO-loops that scan the points of the target iteration space in lexicographic order, and replace occurences in the loop body of the old loop indices with the new loop indices. The first problem is non-trivial and is discussed in Sections 3.3 and 3.4. On the other hand, the problem of transforming the loop body is relatively straightforward and we sketch a solution here for completeness. If vectors  $S_i$  and  $S_j$  represent the source and target iteration variables, notice that  $S_i = T^{-1}S_j$ . This is just a set of equations expressing the old subscripts in terms of the new ones, and it can be used to eliminate occurrences of the source iteration variables in the body of the loop in favor of the new ones. For our running example, this set of equations is the following:

$$\begin{pmatrix} i \\ j \end{pmatrix} = \begin{pmatrix} -1/6 & 4/6 \\ 1/6 & 2/6 \end{pmatrix} \begin{pmatrix} u \\ v \end{pmatrix}$$

The transformed loop body is shown in Figure 3.1(b).

Note that  $T^{-1}S_j$  will always be an integer point even though  $T^{-1}$  may be a rational matrix; therefore, expressions like u/2 and (u+2v)/6 in Figure 3.1(b) should be strength reduced.

### 3.3 Difficulties in Generating Code

The difficulty in generating DO-loops to scan the target iteration space is that a Λ-transformation, in general, does not preserve lexicographic order (two iterations may be performed in one order in the source loop nest but in a different order in the target loop nest), so there is no obvious way to use the source loop nest to generate code. As a first attempt, we can find the image of the original bounds (the four inclined lines in Figure 3.1(d) for the running example), and then generate a loop nest that visits in lexicographical order all the integer points in the area bounded by the image. In this section, we show that this approach works well when the target iteration space is dense; sparse iteration spaces will require additional machinery.

#### 3.3.1 Computing Image of Bounds

There are many ways to compute the image of the original bounds; here, we describe a simple method that uses Fourier-Motzkin elimination.

Given a non-singular matrix representing the transformation, the image bounds for the target loop can be computed using the inverse of the transformation. Let  $S_i = (i_1, ..., i_n)^T$  and  $S_j = (j_1, ..., j_n)^T$  be source and target loop indices respectively under the non-singular transformation T. Let the loop bounds for loop  $i_k$  be an affine function of loop indices  $i_1, ..., i_{(k-1)}$ . Each lower bound is in the form of  $a_{j1}i_1 + ... + a_{j(k-1)}i_{(k-1)} + b_j \leq i_k$ . There may be many such lower bounds whose maximum is the lower bound for  $i_k$ . Similarly for upper bounds, there may be many affine bounds whose minimum is the upper bound for  $i_k$ . The bounds in the loop nest can be written in the following matrix form:

$$L_bS_i + b_l < I_lS_i$$

and  $I_uS_i < U_bS_i + b_u$

where  $L_b(U_b)$  is an  $m_l \times n$   $(m_u \times n)$  matrix,  $b_l(b_u)$  is a vector of length  $m_l(m_u)$ .  $I_l(I_u)$  is an identity matrix with some of its rows replicated to an  $m_l \times n$   $(m_u \times n)$  matrix. Each row of  $L_b(U_b)$  plus the corresponding row from  $b_l(b_u)$  form one lower(upper) bound.

Then the source iteration space is bounded by the following inequalities:

$$AS_i \leq b$$

, where  $A = \begin{pmatrix} L_b - I_l \\ I_u - U_b \end{pmatrix}, b = \begin{pmatrix} -b_l \\ b_u \end{pmatrix}$

The bounds for  $S_j$  are found by replacing  $S_i$  by  $T^{-1}S_j$ .

$$AT^{-1}S_j \le b \tag{3.1}$$

These inequalities can not be used directly as loop bounds, since the bounds for a loop can only be a function of outer loop indices. We use the Fourier-Motzkin elimination algorithm [DE73] suggested in [AI91] to compute the suitable bounds. The Fourier-Motzkin algorithm may introduce redundant constraints, but these may be eliminated [AI91].

The Fourier-Motzkin algorithm is quite simple. Consider a system of linear inequalities

$$\sum_{j=1}^{n} a_{ij} x_j \le b_j, \qquad i = (1, ..., m).$$

This system can be partitioned into three sets of inequalities according to the sign of the coefficient of  $x_n$ .

$$x_n \leq D_i(\overline{x}), \quad i = (1, ..., p)$$

$x_n \geq E_j(\overline{x}), \quad j = (1, ..., q)$

$0 \leq F_k(\overline{x}), \quad k = (1, ..., r)$

where  $D_i$ ,  $E_j$  and  $F_k$  are linear functions of  $\overline{x} = (x_1, ... x_{(n-1)})$ .

Now, we can eliminate  $x_n$  from the system to get the following reduced system.

$$E_j(\overline{x}) \leq D_i(\overline{x}), \quad i = (1, ..., p), \quad j = (1, ..., q)$$

$0 \leq F_k(\overline{x}), \quad k = (1, ..., r)$

This process can be repeated until there is exactly one variable left. The bounds for this variable can be determined from inspection of the reduced system of equations.

Going back to our problem, consider the system of inequalities for  $S_j$ . The loop bounds for  $j_n$  can be computed by solving the inequalities for  $j_n$ . The bounds for  $j_k$  can be computed by first eliminating  $j_{(k+1)}, ... j_n$  from the system using Fourier-Motzkin elimination, then solving for  $j_k$  etc.

Consider the working example. The iteration space (Figure 3.1(c)) is represented by the integer vectors bounded by the system of linear inequalities in

$$\begin{array}{ll} -1 \leq p \leq 5 & -1 \leq p \leq 5 \\ \max(1,\frac{p+1}{2}) \leq q & \max(1,\lceil\frac{p+1}{2}\rceil) \leq q \\ q \leq \min(3,\frac{p+3}{2}) & q \leq \min(3,\lfloor\frac{p+3}{2}\rfloor) \end{array}$$

(a) Image of Bounds

(b) Exact Bounds

Figure 3.4: Dense Iteration Space

Figure 3.1(e). By computing i, j in terms of u, v, replacing i, j by u, v in the inequalities and using the Fourier-Motzkin elimination, we have the image of the source bounds (Figure 3.1(f)). Unfortunately, we cannot use these inequalities directly to generate code for the target loop nest. There are two problems. First, the lower and upper bounds may not even be integers — for example, when u = 4, the lower bound for v is  $\frac{5}{2}$ . Furthermore, even though the source iteration space is dense, the target iteration space is sparse. This means that we must find some way to skip over points (like (2,3) in our example) that are not in the iteration space of the target loop nest.

#### 3.3.2 Dense Spaces

For the special case when the target iteration space is dense (such as when a unimodular matrix is used to transform a loop nest with a dense iteration space (Theorem 3.2.3)), both these problems can be solved easily. If the target iteration space is dense, there is no need to skip over points that are not in the iteration space of the target loop nest. Furthermore, we can use floor and ceiling operations to get the nearest integers within the image bounds.

For example, consider the unimodular transformation  $U = \begin{pmatrix} -1 & 2 \\ 0 & 1 \end{pmatrix}$  on the working example.

$$\left(\begin{array}{c} p \\ q \end{array}\right) = U \left(\begin{array}{c} i \\ j \end{array}\right)$$

For the source bounds in Figure 3.1(e), we can compute the image bounds shown in Figure 3.4(a). Since the target space is dense, we can use the ceiling and floor operations to compute the exact bounds shown in Figure 3.4(b).

#### 3.3.3 Discussion

For sparse iterations spaces, the ceiling and floor operations cannot solve the problem. For the example in Figure 3.1(d), (4, 3) is the closest integer point to the boundary of v when u=4, but the starting point of the target loop nest is (4, 4). One possibility is to use conditional tests in the loop body to avoid executing the loop body at points that do not correspond to points in the target iteration space. This approach has been used by other researchers [Lu91], but it involves visiting integer points that are not necessary; moreover, the conditional tests are expensive.

### 3.4 Algorithm for Code Generation

The key insight to solving the general problem is that an integer non-singular matrix T can be decomposed into the product of a lower triangular matrix H

with positive diagonal elements and a unimodular matrix U. This decomposition is related to the  $Hermite\ normal\ form$  of the transformation matrix [Sch86]. We show that if U is used to transform the program, the resulting program executes iterations in the same lexicographic order as the program obtained by using T as the transformation matrix. We also show that the diagonal elements of H correspond to loop step sizes. Putting these observations together gives an algorithm that generates efficient code for the general case of non-singular matrices.

#### 3.4.1 Auxiliary Iteration Space

By applying column operations to an integer non-singular matrix T, we can reduce it to an integer lower triangular matrix with positive diagonal elements. This lower triangular matrix is related to the  $Hermite\ normal\ form\ [Sch86]$  of the matrix T. It follows that T can be written as the product of a lower triangular matrix H with positive diagonal elements and a unimodular matrix U that represents the composition of the column operations. This decomposition is not unique, but for our purpose, any such decomposition is adequate; to avoid being pedantic, we will abuse terminology and refer to any such H as the Hermite form of the transformation matrix T. Figure 3.5 shows how to compute H and U.

Let T = HU, and let the source space be  $S_i$ , and the target space be  $S_j$ . Define  $S_k = US_i$ . Then,

$$S_i = TS_i = HUS_i = HS_k$$

**Definition 3.4.1** The iteration space  $S_k$  is called the auxiliary iteration space of  $S_i$  with respect to the decomposition HU.

**Theorem 3.4.1** The auxiliary iteration space is a dense space if the source space is dense.

**Proof:** Follows from Theorem 3.2.3 since U is unimodular.  $\square$

Therefore the exact loop bounds of the auxiliary space can be computed using the algorithm in Section 3.3.

An important property of the auxiliary space is that it executes iterations in the same lexicographic order as the target iteration space. To see this, consider our running example.

$$T = \begin{pmatrix} -2 & 4 \\ 1 & 1 \end{pmatrix} \quad H = \begin{pmatrix} 2 & 0 \\ -1 & 3 \end{pmatrix} \quad U = \begin{pmatrix} -1 & 2 \\ 0 & 1 \end{pmatrix}$$

```

Input: An \ n \times n integer matrix T.

Output: The Hermite form H of T and a unimodular matrix U.

Algorithm Hermite

begin

U = I, where I is an n \times n identity matrix.

For i = 1 to n do

/* Consider the submatrix T[i:n, i:n] */

While T[i, i+1:n] \neq \vec{0} do

Apply elementary column operations U_e to make T[i, i]

positive and T[i, i+1:n] zero.

U = U_e^{-1}U

End-While

End-For

H = T

end

```

Figure 3.5: Computing the Hermite form

H is lower triangular with positive diagonal elements, and U is unimodular. Consider using U to transform the source program.

$$\left(\begin{array}{c} p \\ q \end{array}\right) = U\left(\begin{array}{c} i \\ j \end{array}\right)$$

This is the unimodular transformation considered in Figure 3.4 in Section 3.3, and the bounds of the auxiliary iteration space are shown in Figure 3.4(b). To develop the readers insight into the relationship between the source, auxiliary and target iteration spaces, the mappings between these spaces are shown below — notice that both (p,q) and (u,v) are traversed in the same lexicographical order, but that this order is different from that of the source. This can also be seen by comparing the iteration space diagrams in Figures 3.1(d) and 3.4.

To show that this property is true in general, let  $\prec$  be the lexicographical order.

**Theorem 3.4.2** If the auxiliary iteration space is traversed in the lexicographical order, then the target iteration space is also traversed in the lexicographical order.

**Proof:**  $S_j = HS_k$ , where H is a lower triangular matrix with positive diagonal. Let  $\vec{k_1} \prec \vec{k_2}$  be two iterations in the auxiliary iteration space, and  $\vec{d_1} = \vec{k_2} - \vec{k_1}$  be the distance of the two vectors. Clearly  $\vec{d_1} \succ 0$ . To see that the lexicographical order is preserved, consider the new distance  $\vec{d_2}$ .

$$\vec{d_2} = \vec{j_2} - \vec{j_1} = H\vec{k_2} - H\vec{k_1} = H\vec{d_1}$$

If  $\vec{d_1}(i)$ , the *i*th element of  $\vec{d_1}$ , is the leading nonzero,  $\vec{d_1}(i)$  must be positive, since  $\vec{d_1} \succ 0$ . Then the leading nonzero of  $\vec{d_2}$  is  $h_{ii}\vec{d_1}(i)$ , which is also positive. Therefore  $\vec{d_2} \succ 0$ , and  $\vec{j_1} \prec \vec{j_2}$ .  $\square$

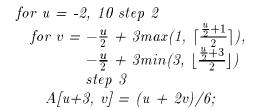

This result yields a technique for code generation - decompose T into HU, generate the DO-loops for traversing the auxiliary space using the technique of Section 3.3 (or any other technique that works for unimodular matrices) and compute the target iteration space variables in the loop body. Using the bounds for the auxiliary space computed earlier, the target code for our running example is the following:

$$\begin{array}{ll} for \ p = -1, \ 5 \\ for \ q = max(1, \lceil \frac{p+1}{2} \rceil), \ min(3, \lfloor \frac{p+3}{2} \rfloor) \\ \binom{u}{v} = \binom{2}{-1} \binom{0}{3} \binom{p}{q} \\ A[u+3,v] = (u+2v)/6; \end{array}$$

Although this code avoids making conditional tests, it can be improved considerably. Notice that the computation of u is invariant in the inner loop; moreover, u is a linear function of the outer loop index and it can be strength reduced. Similarly, v is a linear function of p and q and it can be strength reduced. Although such optimizations can be left to a later optimization phase, it is preferable to use the induction variables u and v directly as the loop control variables instead of p and q. We show how to do this next.

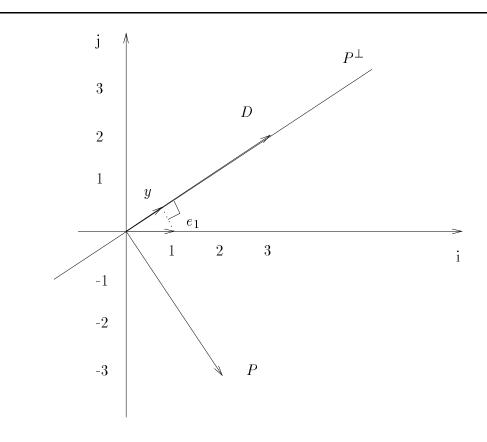

# 3.4.2 Target Iteration Space

Since H is lower triangular, it is easy to convert the bounds in the auxiliary space into bounds in the target space. For our example, the relation between these two spaces is given by the following equation:

$$\left(\begin{array}{c} u \\ v \end{array}\right) = \left(\begin{array}{cc} 2 & 0 \\ -1 & 3 \end{array}\right) \left(\begin{array}{c} p \\ q \end{array}\right)$$

From the first equation, it follows that the bounds for u are the bounds of p multiplied by 2. Therefore, the bounds for u are the following:

$$-2 < u < 10$$

The bounds for v are the bounds of q multiplied by 3 with the offset -p which is  $-\frac{u}{2}$ . Therefore, the bounds for v are the following:

$$-\frac{u}{2} + 3max(1, \lceil \frac{\frac{u}{2}+1}{2} \rceil) \le v \le -\frac{u}{2} + 3min(3, \lfloor \frac{\frac{u}{2}+3}{2} \rfloor)$$

These bounds on u are constant, and the bounds on v depend only on u. Therefore, these bounds can be used directly to construct the loop nest, as is shown in Figure 3.1(b). The general algorithm is given in Figure 3.6.

The proof of correctness of this algorithm depends on the following lemma and the fact that the diagonal elements of H are positive, and is omitted.

Input: The Hermite form H, and the bounds of the auxiliary space  $S_k$  Output: The bounds of the target space  $S_j$ .

```

\label{eq:localization} \begin{split} &begin \\ &S_k = H^{-1}S_j \\ &For \ i = 1 \ to \ n \ do \\ & /^* \ Compute \ the \ offset \ by \ replacing \ k_1, \ ..., \ k_{(i-1)} \ by \ j_1, \ ... \ j_{(i-1)} \ ^*/ \\ & v_i = h_{i1}k_1 + ... + h_{i(i-1)}k_{(i-1)} = f_i(j_1,...,j_{(i-1)}) \\ & /^* \ Compute \ lower \ bound \ with \ k_1, \ ..., \ k_{(i-1)} \ in \ l_i^k \\ & replaced \ by \ j_1, \ ... \ j_{(i-1)} \ using \ S_k = H^{-1}S_j. \ ^*/ \\ & l_i^j = v_i + h_{ii}l_i^k \\ & /^* \ Compute \ upper \ bound \ with \ k_1, \ ..., \ k_{(i-1)} \ in \ u_i^k \\ & replaced \ by \ j_1, \ ... \ j_{(i-1)} \ using \ S_k = H^{-1}S_j. \ ^*/ \\ & u_i^j = v_i + h_{ii}u_i^k \\ & End-For \\ end \end{split}

```

Figure 3.6: Computing the loop bounds

**Lemma 3.4.1** Let  $P1 = (j_1, ..., j_n)$  be a point in the target iteration space that is the image of a point  $P2 = (k_1, ..., k_n)$  in the auxiliary space. Any co-ordinate  $j_i$  can be written as a function of  $k_1, ..., k_i$ ; similarly,  $k_i$  can be written as a function of  $j_1, ..., j_i$ .

**Proof:** Follows from the observation that any leading principal sub-matrix H[1:i,1:i] of H is lower triangular and non-singular, and that the inverse of a lower triangular matrix is also lower triangular [GVL89].  $\square$

To complete the generation of code, we need to skip over points within the bounds that are not in the target iteration space. This would be difficult to do if these points appeared in some irregular pattern within the loop nest bounds; fortunately, we can show that this is not the case. In fact, we show that it suffices to use DO-loops with constant step sizes, and that these step sizes are the integers in the diagonal of the Hermite form.

For the working example, H has the diagonal [2,3], which means that the loop step is 2 for the outer loop, and 3 for the inner loop. More generally, we have the following theorem.

**Theorem 3.4.3** The positive integers on the diagonal of the Hermite form are the gaps in each dimension.

**Proof:** Consider two points  $P1 = (k_1, k_2, ...k_i, k_{(i+1)}...k_n)$  and  $P2 = (k_1, k_2, ...k_i + 1, a_{(i+1)}...a_n)$  in the auxiliary space which have the same co-ordinates in the first i-1 dimensions. Let P3 and P4 be their images in the target space. From Lemma 3.4.1, it follows that P3 and P4 have the same co-ordinate for the first (i-1) dimensions; moreover, their difference in the ith dimension is  $h_{ii}$  since H is lower triangular.  $\square$

Hence a loop nest can be constructed to traverse the target space directly. For our running example, the target program is the following:

for

$$u = -2$$

, 10 step 2

for  $v = -\frac{u}{2} + 3max(1, \lceil \frac{\frac{u}{2}+1}{2} \rceil), -\frac{u}{2} + 3min(3, \lfloor \frac{\frac{u}{2}+3}{2} \rfloor)$  step 3

$A[u+3,v] = (u+2v)/6$ ;

Notice the auxiliary space is used only to compute the bounds for the target space.

# 3.4.3 Sparse Source Iteration Space

So far, we have considered only the case when the source iteration space is dense. Our technique also works when the source iteration  $S_i$  is sparse as long as the source space is regular. A regular sparse space is one that can be represented

by an integer lattice  $\Lambda_i$ . The base space  $S_b$  is always dense. The lattice basis  $\Lambda_i$  can be thought of as a  $\Lambda$ -transformation from  $S_b$  to  $S_i$ . The bounds for  $S_b$  can be computed by the Fourier-Motzkin elimination. Then any  $\Lambda$ -transformation T on  $S_i$  can be considered as a new  $\Lambda$ -transformation  $T\Lambda_i$  on the base space  $S_b$ , since  $\Lambda$ -transformations are closed under composition.

This observation lets us handle source loops in which lower bounds are affine functions of loop indices, upper bounds are piece-wise affine functions of loop indices and step sizes are constant, as shown below.

**Theorem 3.4.4** The following loop nest with constant steps is regular.

for

$$i_1 = 0$$

to  $ub_1$  step  $s_1$

for  $i_2 = a_{21}i_1$  to  $ub_2$  step  $s_2$

...

for  $i_n = a_{n1}i_1 + a_{n2}i_2 + ... + a_{n(n-1)}i_{n-1}$  to  $ub_n$  step  $s_n$

**Proof:** Without loss of generality, the loop nest can be *shifted* so that  $\vec{0}$  is a loop point. This just changes the *origin* of the lattice. It is easy to show that the triangular matrix S whose jth row comes from the coefficients of the lower bound and the loop step of the jth loop forms a basis for the lattice of the loop points.

$$S = \begin{pmatrix} s_1 & 0 & \cdot & 0 \\ a_{21}s_1 & s_2 & \cdot & 0 \\ \cdot & \cdot & \cdot & \cdot \\ a_{n1}s_1 & a_{n2}s_2 & \cdot & s_n \end{pmatrix}$$

# 3.5 Data Dependences

Not every  $\Lambda$ -transformation is valid with respect to the data dependencies in the original loop nest. Data dependencies can be represented by *distance* or *direction* vectors that are lexicographically positive. For example, a distance vector  $d = \begin{pmatrix} 3 \\ 2 \end{pmatrix}$  means that the iteration (i, j) depends on the iteration (i-3, j-2).

# 3.5.1 A Dependence Algebra

In this section, we define an algebra on data dependence vectors.

There are three kinds of data dependences between statements. A data flow-dependence occurs when a value computed in one statement is used in another statement. A data anti-dependence occurs when a variable used in one statement before being reassigned by another statement. A data output-dependence occurs

| Table for Addition |          |     |     |        |   |        |   |        |   |

|--------------------|----------|-----|-----|--------|---|--------|---|--------|---|

| +                  | 0        | p   | n   | <      | < | >      | > | $\neq$ | * |

| a                  | a        | a+p | a+n |        |   |        |   |        |   |

| <                  | <        | <   | *   | <      |   |        |   |        |   |

| $\leq$             | <u> </u> | <   | *   | <      | < |        |   |        |   |

| >                  | >        | *   | >   | *      | * | >      |   |        |   |

| >                  | >        | *   | >   | *      | * | $\geq$ | > |        |   |

| $\neq$             | $\neq$   | *   | *   | $\neq$ | * | $\neq$ | * | $\neq$ |   |

| *                  | *        | *   | *   | *      | * | *      | * | *      | * |

| Table for Multiplication |   |              |              |  |  |  |  |

|--------------------------|---|--------------|--------------|--|--|--|--|

| ×                        | 0 | p            | n            |  |  |  |  |

| c                        | 0 | $c \times p$ | $c \times n$ |  |  |  |  |

| <                        | 0 | <            | >            |  |  |  |  |

| $\leq$                   | 0 | $\leq$       | >            |  |  |  |  |

| >                        | 0 | >            | <            |  |  |  |  |

| >                        | 0 | $\geq$       | $\leq$       |  |  |  |  |

| $\neq$                   | 0 | <i>≠</i>     | <del>-</del> |  |  |  |  |

| *                        | 0 | *            | *            |  |  |  |  |

Figure 3.7: Operators for Directions

when a variable is computed before being recomputed by another statement. When the exact distance is unknown at compile-time, direction vectors provide a conservative approximation.

**Definition 3.5.1** A distance is an integer, and a direction can be one of "<", ">","=", "<=", ">=", "<=", "<=", " and "\*".

For instances, "<" means that the distance is positive; ">" negative, and "\*" unknown.

A data dependence in the loop nest of depth n is represented by a vector of distances or directions. For example, the distance vector  $\begin{pmatrix} 0 \\ 0 \\ 1 \end{pmatrix}$  tell us that the dependence is between successive iterations of the innermost loop. A dependence vector has the property that its leading non-zero is always positive; a legal transformation must preserve this property for each dependence, since the source of the dependence must be executed before its destination. More information on data dependences and techniques of dependence analysis can be found in [Ban88]. A direction vector can be (< > =) or (= < \*), as long as the leading nonzero is positive.

**Definition 3.5.2** A dependence matrix is a matrix whose columns are dependence vectors.

In order to describe the computation over these direction symbols, we define operations similar to addition and multiplication on integers. In Figure 3.7, let c and a be any constant, p be a positive and n be a negative.

# 3.5.2 Legality of $\Lambda$ -transformations

Once we have the dependence algebra, the legality test for a given non-singular transformation T is quite simple. For a dependence vector d in the original loop nest, Td is the dependence vector in the new iteration space, since T is linear. A transformation T is legal if and only if Td is lexicographically positive.

# 3.6 Discussion and Related Work

We have introduced a loop transformation framework called  $\Lambda$ -transformations based on integer non-singular matrices. Efficient code can be generated for target loop nests using integer lattice theory. We have also presented a simple completion algorithm that generates correct transformations from partial transformations.

The use of compound loop transformations to parallelize loop nests goes back to Lamport's hyperplane method [Lam74]. These compound transformations can be viewed as compositions of loop interchange, skewing and reversal. Unimodular matrices were used by Dowling to parallelize loop nests [Dow90]. The unimodular framework was further developed by Banerjee [Ban90], and Wolf and Lam [WL91b]. Ancourt and Irigoin [AI91] have developed algorithms for scanning polyhedra using loop nests. Other approaches to extending the unimodular framework can be found in Lu and Chen [Lu91], Ramanujam [Ram92], and Barnett and Lengauer [BL92]. We are not aware of any prior work on general completion procedures.

# Chapter 4

# Transformations for Memory Locality

# 4.1 Introduction

Scalable parallel machines are often organized as networks of processor-memory pairs; examples of such machines are the BBN TC 2000, the Kendall Square Research 'all-cache' machine, and multi-computers like the Intel iPSC/i860. These machines are called non-uniform memory access (NUMA) machines because a processor can access data in its local memory ten to a thousand times faster than it can access non-local data. For example, in the Kendall Square Research 'all-cache' machine, accesses to local memory take 18 cycles while accesses to non-local memory take 175 cycles [Ken91]. Distributed memory machines like the Intel iPSC/i860 have even greater non-uniformity in access times because access to non-local data must be orchestrated through the exchange of messages [Int91]. If non-local accesses are on the critical path through a program, making these accesses local through proper data management will speed up program execution.

A second feature of most NUMA architectures is that block transfer of data between processors is more efficient than sending this data using many small messages. Data transfer between processors can be viewed as a pipeline with a large setup time compared to the time per stage. For example, on the Intel iPSC/i860, it takes 70 microseconds to start up communication, but it takes only 1 microsecond to transfer a double precision floating point number between nearest neighbors once the communication has been setup [Rue]. Therefore, when a number of data items must be sent from one processor to another, it is preferable to use a single long message to amortize startup time.

Contention in the network has the effect of increasing the expected latency of non-local references; therefore, data management to avoid non-local references has the added benefit of reducing contention, thereby improving performance.

Interestingly, analytical studies show that long messages can increase the latency of non-local accesses [Aga91]. This is an argument against long messages, but on current machines, this effect seems to be of secondary importance compared to the benefits of amortizing start-up time, as we show in Section 4.7.

In this chapter, we present a systematic approach to loop restructuring for parallel machines with a memory hierarchy. As in the ownership approach, our starting point is a language like FORTRAN-D with user-specified data decomposition. We use the data distribution information to drive access normalization. The objective of the restructuring is to transform loop nests so that code can be generated by distributing iterations of the outermost parallel loops among the processors without compromising locality. The structure of inner loops is chosen so that data can be transferred using block transfers wherever possible.

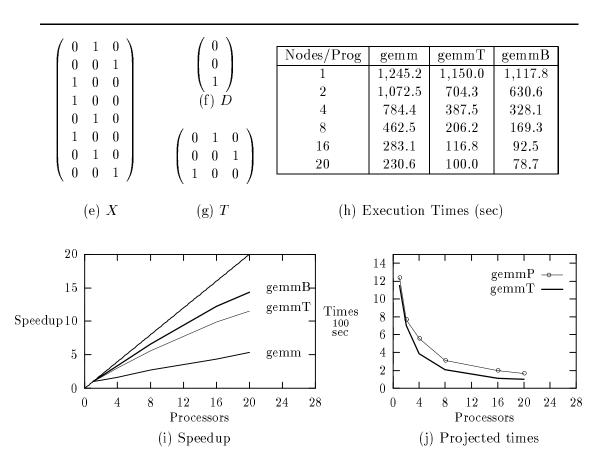

The rest of the chapter is organized as follows. In Section 4.2, we discuss a simple example that gives an overview of our compiling strategy. We also introduce the data access matrix, which plays a key role in the development. For some programs, the data access matrix is non-singular and can be used directly to transform the loop nest, as we show in Section 4.3. In general, however, this matrix may not be non-singular, and the techniques of Section 4.4 must be used to produce a non-singular matrix for the transformation. The final problem is guaranteeing that the transformation respects program dependences; this is done in Section 4.5. We present experimental results in Section 4.7 that demonstrate that our methods work well on programs of practical interest such as routines from the BLAS (Basic Linear Algebra Subroutines) library [CVL88]. Finally, we discuss related work in Section 4.8.

# 4.2 Data Access Matrix

In this section, we introduce a key data structure called the data access matrix. To understand the need for loop restructuring, consider the program in Figure 4.1(a), which is a simplified version of the SYR2K code discussed in Section 4.7. Assume that both A and B have a wrapped column distribution. Distributing iterations of the outer loop among the processors (Figure 4.1(b)) results in processor p executing iterations p, p + P, etc. Consider accesses to elements of array B. Each iteration of the outer loop makes  $N_2(b-b/P)$  non-local accesses, and the total number of non-local accesses is  $N_1N_2b(1-1/P)$ .

The ownership rule uses data decomposition information to generate code. A processor is involved in the execution of an iteration (i, j, k) if it owns any of the elements referenced in the body of the loop in that iteration. Therefore, processor p has work to do in iteration (i, j, k) if  $(j - i) \mod P = p$  (it must update an element of B) or if  $(j + k) \mod P = p$  (it must send an element of A to whichever processor is updating B in that iteration). This is accomplished by placing these conditional tests in front of the statement, and having all the

Figure 4.1: Transformation and Code Generation for a Simple Example

processors execute all iterations 'looking for work to do' [CK88,ZC90]. In simple programs, these conditional tests can be optimized away, but in general they must be executed at runtime, which is inefficient. Moreover, in our program, the code cannot make use of block transfers of elements of A since the elements of A referenced during one iteration of the j loop are referenced by different processors.