# MILLIMETER WAVE TRANSCEIVER FRONTEND CIRCUITS IN ADVANCED SIGE TECHNOLOGY WITH CONSIDERATIONS FOR ON-CHIP PASSIVE COMPONENT DESIGN AND SIMULATLION

### A Dissertation

Presented to the Faculty of the Graduate School

of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by

Yanxin Wang

August 2006

# MILLIMETER WAVE TRANSCEIVER FRONTEND CIRCUITS IN ADVANCED SIGE TECHNOLOGY WITH CONSIDERATIONS FOR ON-CHIP PASSIVE COMPONENT DESIGN AND SIMULATLION

# Yanxin Wang, Ph. D. Cornell University 2006

A novel design approach for implementing millimeter wave wireless transceiver front-end circuits is proposed. The design methodology takes advantage in advances in Silicon Germanium (SiGe) fabrication technology and sophisticated Electro-Magnetic (EM) simulation software to ensure successful implementation of circuits designed to operate in millimeter wave range. The discussion covers basic circuits common in typical transceiver architecture such as low noise amplifier (LNA), active balun, and mixer. The design methodology is not limited to the above circuits. It can be applied to many other situations where operating frequency is high and the dimensions of passive structures are comparable to signal wavelength.

A comprehensive solution to the design of millimeter wave wireless transceiver front-end circuits requires consideration for active devices as well as passive structures. For circuits operating at 94 GHz, 40 GHz and 18 GHz discussed in this dissertation, each design generally has two parts of discussion – one devoted to circuit design and one devoted to passive design. Optimization of circuit performance and reliability is analyzed in each case. Simulation results from both the circuits and the passives are presented and an integrated simulation environment is proposed to simply the design flow. Some measurement results are provided to confirm the validity of the proposed design methodology. Summaries are given at the end of each chapter and future research direction is highlighted at the end of the dissertation.

### BIOGRAPHICAL SKETCH

Yanxin Will Wang was born on October 12, 1979 in Dalian, China and came to the United States in 1997. Yanxin graduated from Cottage Grove High School in Cottage Grove, OR in 1998. He received his undergraduate education from Oregon State University in Corvallis, OR and University of California Berkeley (UC Berkeley) in Berkeley, CA. He graduated in August 2002 with a Bachelor of Science in Electrical Engineering and Computer Science from UC Berkeley. In August 2002 he joined the Broadband Communications Research Laboratory at Cornell University to pursue a Ph.D. degree. He spent the fall and winter of 2005 as an intern at LeCroy Corporation located in Chestnut Ridge, New York where he worked on oscilloscope front-end circuit design. Yanxin received a Master of Science in Electrical and Computer Engineering from Cornell University in May of 2005. He completed his Doctor of Philosophy in Electrical and Computer Engineering with a minor in Earth and Atmospheric Science in August 2006.

To My Parents

### ACKNOWLEDGEMENTS

I would like to express my gratitude to my dear parents, Xizhang Wang and Chuangling Qu, who have provided me the perfect environment where my character and intellectual curiosity were nurtured and who have sacrificed so much to support my education in the United States. Without all the love and support I have received all these years from my parents, I would never have been able to successfully reach my academic goals.

I would like to acknowledge my thesis advisor, Prof. Kevin Kornegay, for his support, as well as the members of my special committee, Prof. Hysell, Prof. Eastman, and Prof. Bhave for critical evaluation of my research work and helpful suggestions. I am also indebted to Cornell University for providing years of funding for my graduate study.

Finally, I would like to thank the members of the Cornell Broadband Communications Research Laboratory who made the graduate experience fond and memorable through many technical and social interactions.

### TABLE OF CONTENTS

| Chapter 1: | Introduction                                               | 1  |

|------------|------------------------------------------------------------|----|

| 1.1        | Overview                                                   | 1  |

| 1.2        | Motivation                                                 | 3  |

| 1.3.       | 1 Development at IBM                                       | 4  |

| 1.3.       | 2 Development at Infineon                                  | 5  |

| 1.4        | Chapters Overview                                          | 6  |

| Chapter 2: | Constraints of Millimeter Wave Front-end IC Design         | 8  |

| 2.1        | Overview                                                   | 8  |

| 2.2        | Constraints from SiGe Device                               | 9  |

| 2.2.       | 1 Lossy Silicon Substrate                                  | 9  |

| 2.2.       | 2 High Frequency Device Modeling                           | 11 |

| 2.3        | Constraints from Passive Elements                          | 12 |

| 2.3.       | 1 Electric-Magnetic (EM) Modeling                          | 14 |

| 2.3.       | 2 Parasitic Extraction                                     | 15 |

| 2.4        | Conclusion                                                 | 16 |

| Chapter 3: | Design Methodology for Millimeter Wave Integrated Circuits | 17 |

| 3.1        | Overview                                                   | 17 |

| 3.2        | Analysis of Circuit Topology Trade-offs                    | 17 |

| 3.2.       | 1 Topology for Low Noise Amplifiers (LNA)                  | 17 |

| 3.2.       | 2 Topology for Mixers                                      | 22 |

| 3.3        | Matching Considerations                                    | 26 |

| 3.3.       | 1 Matching Network                                         | 26 |

| 3.3.       | 2 Active Device Matching Considerations                    | 30 |

| 3.3.       | 3 Circuit Optimization                                     | 41 |

|      | 3.4    | P  | hysical Layout Considerations                                       | 42 |

|------|--------|----|---------------------------------------------------------------------|----|

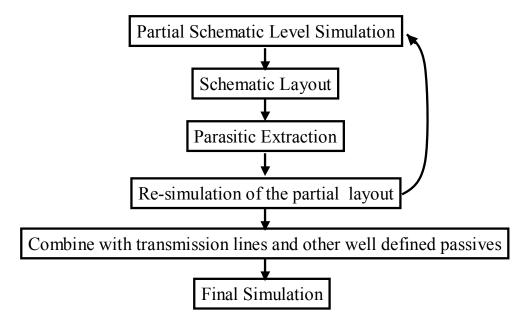

|      | 3.5    | Iı | ntegrated Simulation Considerations                                 | 44 |

|      | 3.5.   | .1 | Proposed Parasitic-aware MM Wave IC Design Flow                     | 44 |

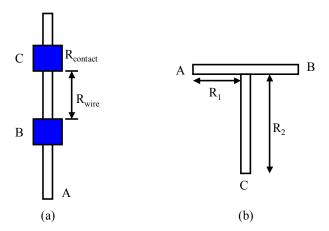

|      | 3.5.   | .2 | Evaluation of Extraction Deck                                       | 46 |

|      | 3.5.   | .3 | Evaluation of EM Simulation Results                                 | 48 |

|      | 3.6    | C  | Conclusion                                                          | 48 |

| Chap | ter 4: | 9  | 4 GHz Receiver Front-end Circuits in SiGe                           | 49 |

|      | 4.1    | C  | Overview                                                            | 49 |

|      | 4.2    | 9  | 4 GHz LNA/Balun                                                     | 50 |

|      | 4.2.   | .1 | Circuit Design                                                      | 50 |

|      | 4.2.   | .2 | Passive Design                                                      | 60 |

|      | 4.2.   | .3 | Layout                                                              | 64 |

|      | 4.3    | L  | NA/Balun Simulation and Measurement Results                         | 64 |

|      | 4.4    | 9  | 4 GHz Double Balanced IF Down-conversion Mixer                      | 67 |

|      | 4.4.   | .1 | Mixer Circuit Design                                                | 67 |

|      | 4.5    | C  | Conclusion                                                          | 71 |

| Chap | ter 5: | 1  | 8 GHz Mixer and Integrated Mixer/VCO in Sige                        | 73 |

|      | 5.1    | C  | Overview                                                            | 73 |

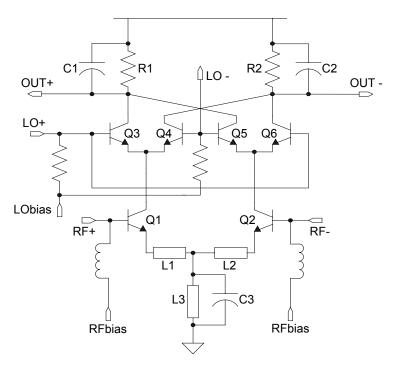

|      | 5.2    | N  | Mixer Circuit Design                                                | 74 |

|      | 5.2.   | .1 | Device Geometry on Noise Figure and Gain                            | 75 |

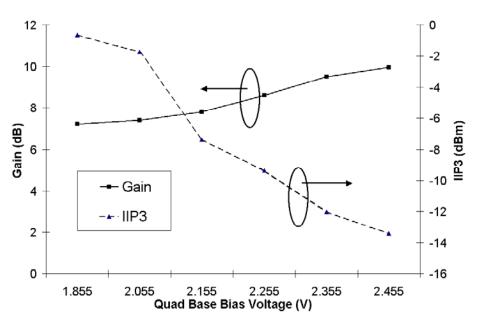

|      | 5.2.   | .2 | Quad Transistors Base DC Bias's Effect on Gain and IIP <sub>3</sub> | 75 |

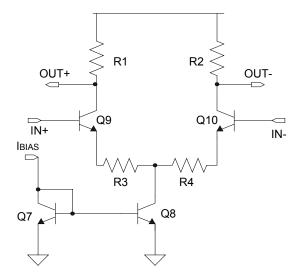

|      | 5.2.   | .3 | Output Buffer                                                       | 77 |

|      | 5.2.   | .4 | Experimental Results                                                | 78 |

|      | 5.3    | Iı | ntegrated Mixer and VCO Combo                                       | 82 |

|      | 5.3.   | .1 | Circuit Design                                                      | 82 |

|      | 5 3    | 2  | Experimental Results                                                | 84 |

| 5.4        | Conclusion                         | 87 |

|------------|------------------------------------|----|

| Chapter 6: | 40 GHz Low Noise Amplifier in SiGe | 88 |

| 6.1        | Overview                           | 88 |

| 6.2        | LNA Circuit Design                 | 88 |

| 6.3        | 40 GHz LNA Layout                  | 91 |

| 6.4        | Simulation and Measurement Results | 92 |

| 6.5        | Conclusion                         | 95 |

| Chapter 7: | Conclusion                         | 96 |

| 7.1        | Summary of this Work               | 96 |

| 7.2        | Technology Issues                  | 97 |

| 7.3        | Future Work                        | 97 |

| References | 98                                 |    |

## LIST OF TABLES

| Table 4-1 94 GHz LNA device parameters                            | 57 |

|-------------------------------------------------------------------|----|

| Table 5-1 Mixer performance compared with other published results | 82 |

| Table 6-1 Other published LNA specs comparison sheet              | 95 |

### LIST OF FIGURES

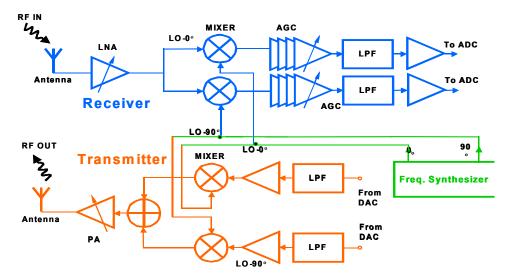

| Figure 1.1: Example of a wireless transceiver system                        | 2  |

|-----------------------------------------------------------------------------|----|

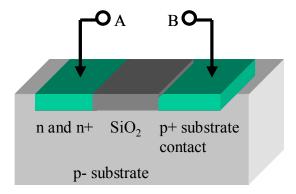

| Figure 2.1: Substrate test structure                                        | 10 |

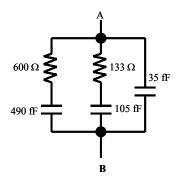

| Figure 2.2: Substrate test structure circuit model                          | 10 |

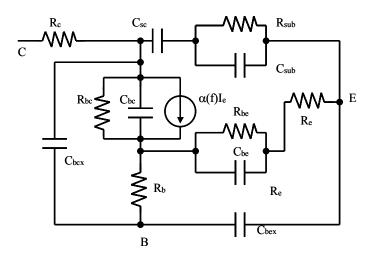

| Figure 2.3: SiGe HBT high frequency model                                   | 11 |

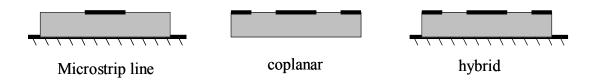

| Figure 2.4: Stripline, coplanar, and combination of the two                 | 13 |

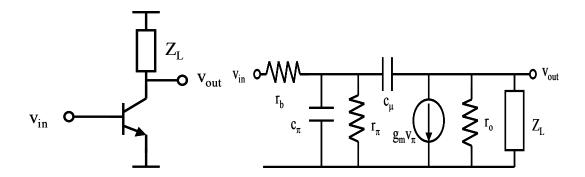

| Figure 3.1 Common-emitter configuration and simplified small signal model   | 18 |

| Figure 3.2 Common-base configuration                                        | 20 |

| Figure 3.3 Cascode configuration for (a) common-emitter and (b) common-base | 21 |

| Figure 3.4 Single balanced mixer                                            | 23 |

| Figure 3.5 Common-base configuration.                                       | 25 |

| Figure 3.6 Smith Chart with a matching example                              | 27 |

| Figure 3.7 Noise model for calculating amplifier's noise figure             | 30 |

| Figure 3.8 Ideal simultaneous noise and power match                         | 33 |

| Figure 3.9 Noise model for SiGe HBT                                         | 35 |

| Figure 3.10 Emitter degenerated input stage                                 | 38 |

| Figure 3.11 Effect of sweeping degeneration inductance                      | 39 |

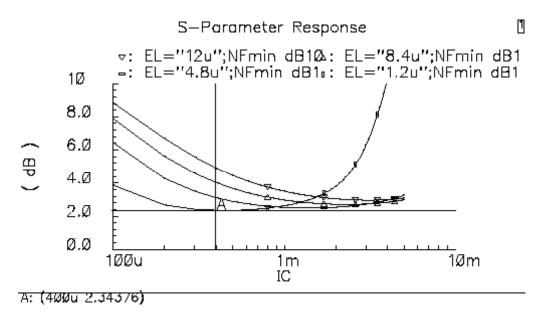

| Figure 3. 12 CE stage device size and bias current on NF <sub>min</sub>     | 39 |

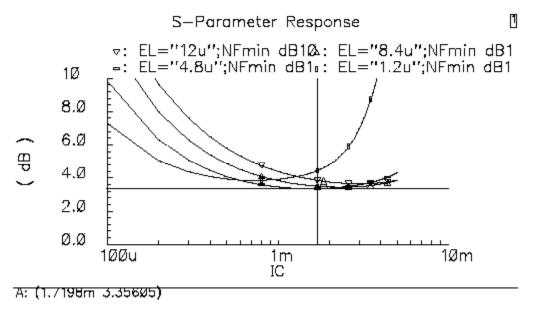

| Figure 3.13 CB stage device size and bias current on NF <sub>min</sub>      | 40 |

| Figure 3.14 Proposed parasitic-aware MM Wave IC design flow                 | 44 |

| Figure 3.15 Cases to test R extraction deck                                 | 46 |

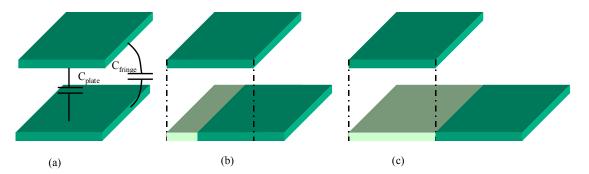

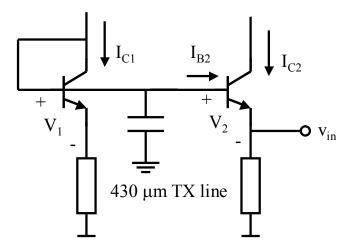

| Figure 3.1617 Capacitance extraction evaluation                             | 47 |

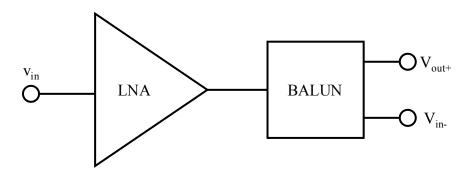

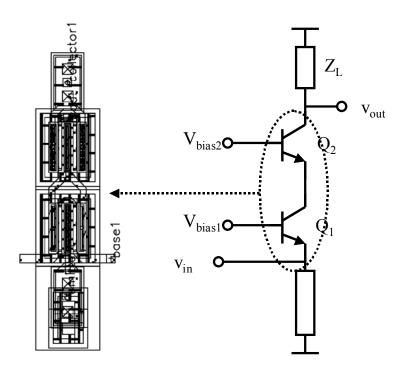

| Figure 4.1: LNA and Balun block diagram                                     | 50 |

| Figure 4.2: Biasing scheme for common emitter configuration.                | 52 |

| Figure 4.3: Biasing scheme for common-base                                  | 52 |

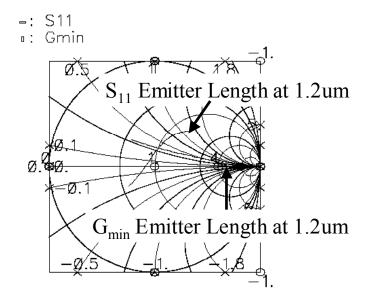

| Figure 4.4: G <sub>min</sub> and S <sub>11</sub> versus I <sub>c</sub>       | 53       |

|------------------------------------------------------------------------------|----------|

| Figure 4.5: $G_{min}$ and $S_{11}$ versus emitter length                     | 54       |

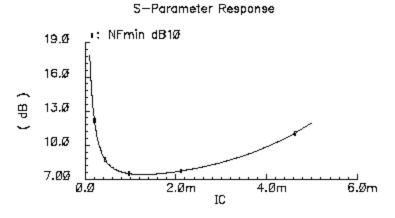

| Figure 4.6: NF <sub>min</sub> verus I <sub>C</sub>                           | 54       |

| Figure 4.7: Parastic-aware extraction for cascode connection                 | 55       |

| Figure 4.8: Complete schematic of 94 GHz LNA and Balun.                      | 56       |

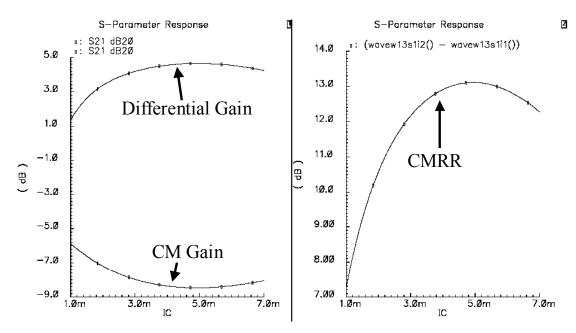

| Figure 4.9: CMRR test circuits at 94GHz. (a) CM (b)Differential Mode         | 58       |

| Figure 4.10: CMRR Simulation results                                         | 59       |

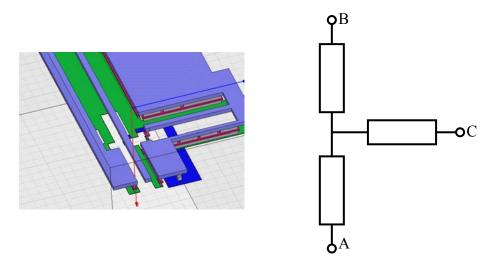

| Figure 4.11: T-junction HFSS setup and model                                 | 60       |

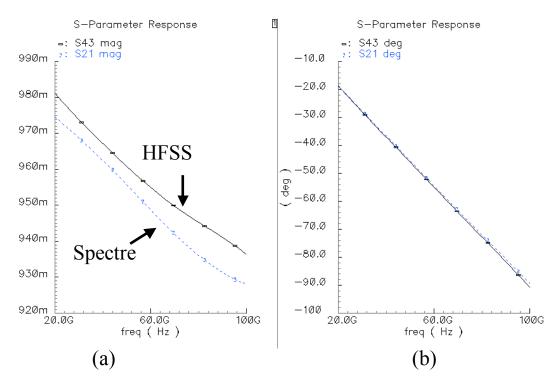

| Figure 4.12: Magnitude and phase of S-parameter from HFSS and Spectre        | 61       |

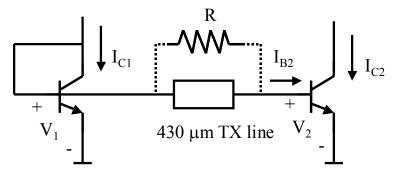

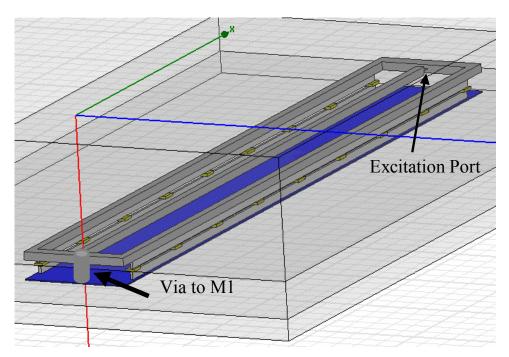

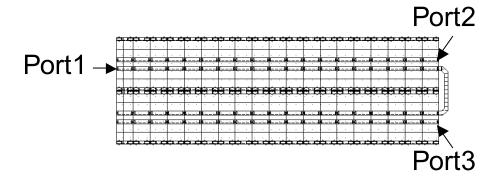

| Figure 4.13: Transmission line EM simulation model with vias                 | 62       |

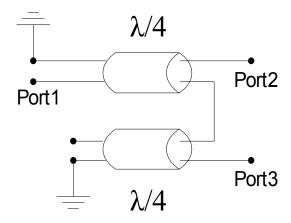

| Figure 4.14: Marchand balun circuit model                                    | 62       |

| Figure 4.15: Marchand balun circuit model                                    | 63       |

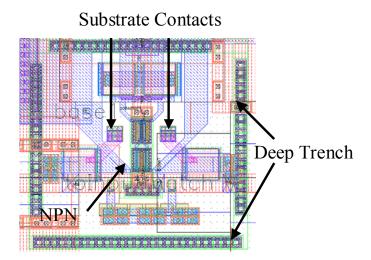

| Figure 4.16: Placement of deep trench isolation and substrate contacts       | 64       |

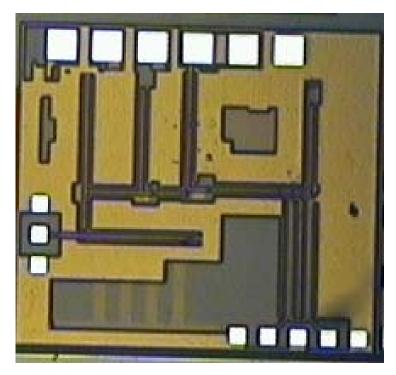

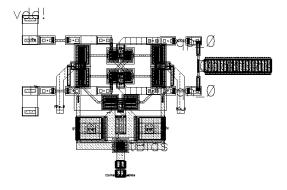

| Figure 4.17: LNA/Balun die photo                                             | 65       |

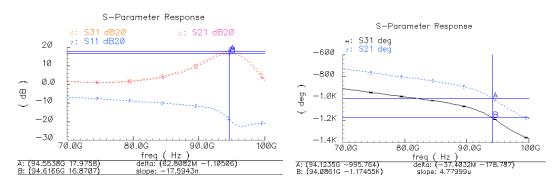

| Figure 4.18: S-parameter magnitude and phase                                 | 66       |

| Figure 4.19: 94 GHz LNA NF and NF <sub>min</sub>                             | 66       |

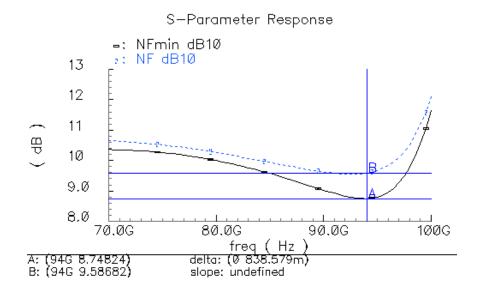

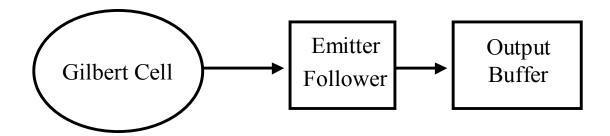

| Figure 4.20: Mixer block diagram                                             | 67       |

| Figure 4.21: Mixer core schematic                                            | 68       |

| Figure 4.22: Mixer core layout                                               | 68       |

| Figure 4.23: Level shifter and output buffer                                 | 69       |

| Figure 4.24: Mixer layout view                                               | 70       |

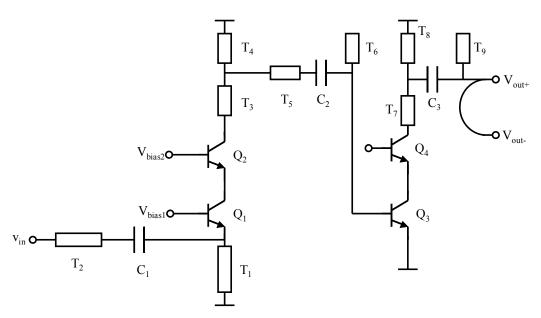

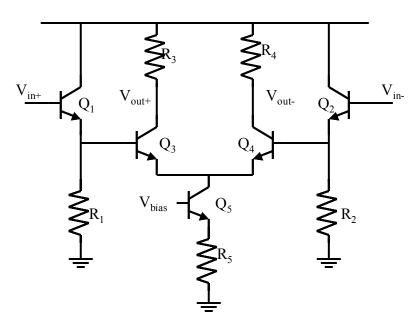

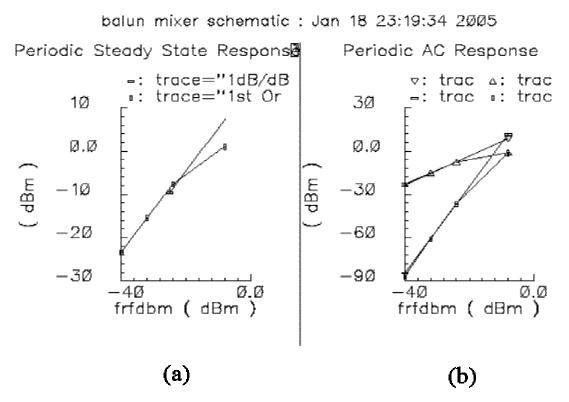

| Figure 5.1: Mixer simplified schematic                                       | 74       |

| Figure 5.2: Simulated gain and IIP3 design trade-off with various DC bias at | the base |

| of the quad                                                                  | 76       |

| Figure 5.3: Output buffer with 50 W termination and 25 W degeneration to g   | give 0dB |

| of gain                                                                      | 77       |

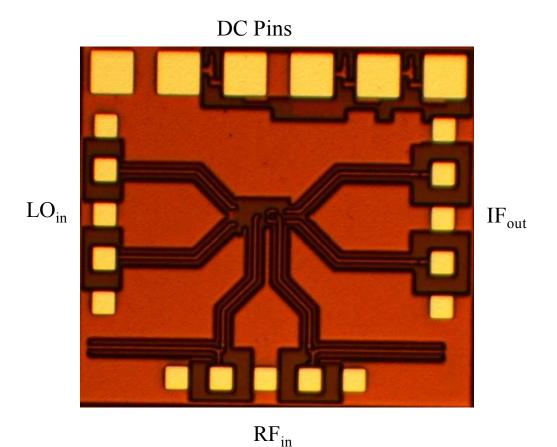

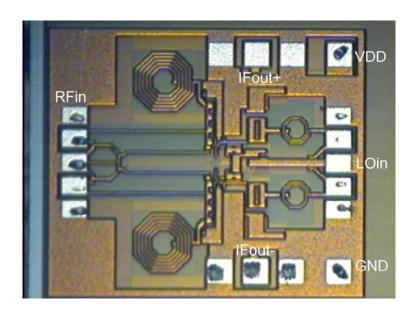

| Figure 5.4: Mixer die photo                                        | 78                   |

|--------------------------------------------------------------------|----------------------|

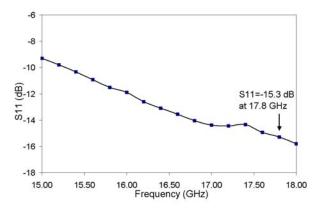

| Figure 5.5: Measured $S_{II}$ at RF port                           | 79                   |

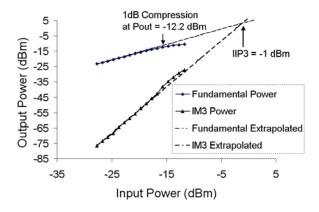

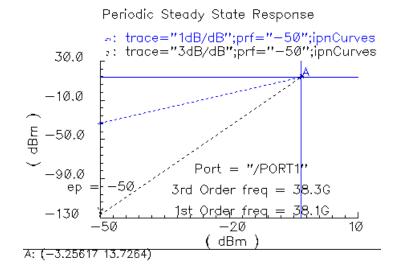

| Figure 5.6: Fundamental and third order intermodulation output po  | ower verses RF input |

| power                                                              | 79                   |

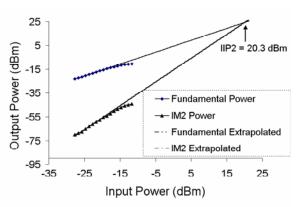

| Figure 5.7: Fundamental and second order intermodulation outp      | ut power verses RF   |

| input power                                                        | 79                   |

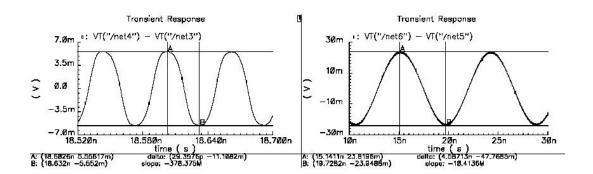

| Figure 5.8: Transient simulation plot for input and output magnitu | de and period of the |

| integrated mixer and VCO                                           | 84                   |

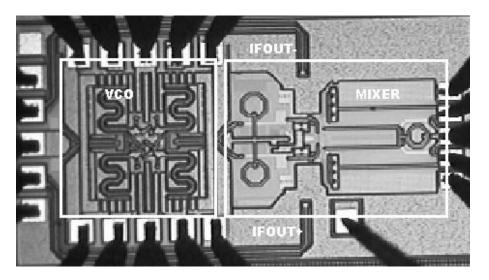

| Figure 5.9: Integrated mixer and VCO die photo                     | 85                   |

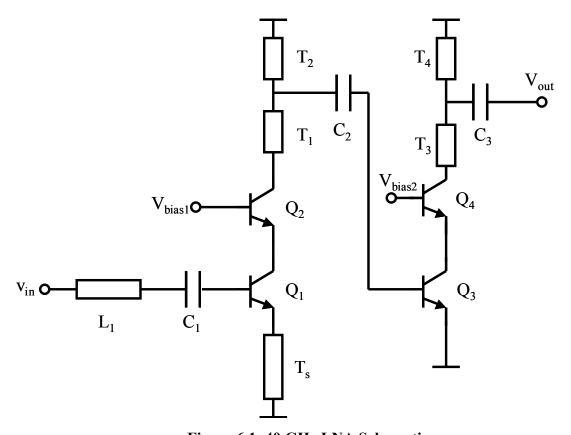

| Figure 6.1: 40 GHz LNA Schematic                                   | 89                   |

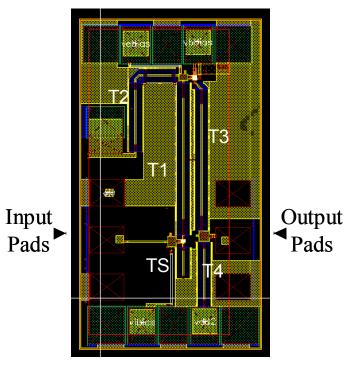

| Figure 6.2: 40 GHz LNA Layout                                      | 91                   |

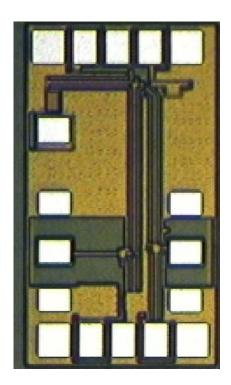

| Figure 6.3: 40 GHz LNA die photo                                   | 92                   |

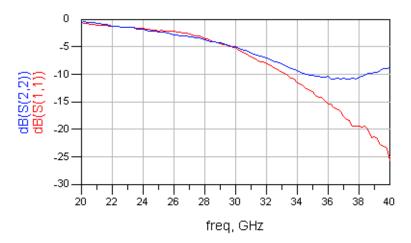

| Figure 6.4: $S_{11}$ and $S_{22}$ response                         | 93                   |

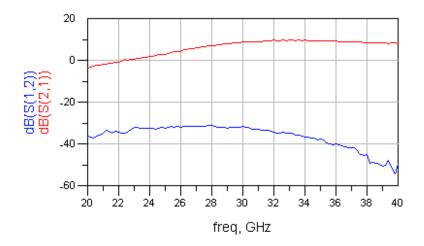

| Figure 6.5: $S_{21}$ Response                                      | 93                   |

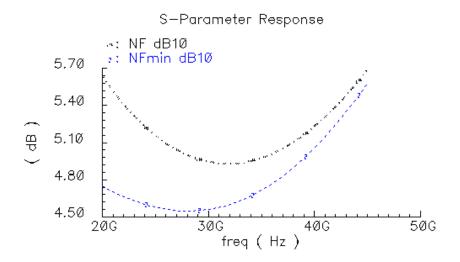

| Figure 6.6: LNA simulated NF and NF <sub>min</sub>                 | 94                   |

| Figure 6.7: LNA simulated IIP <sub>3</sub>                         | 94                   |

# **Chapter 1: Introduction**

### 1.1 Overview

Over the past ten years wireless communication industry has enjoyed tremendous growth that has been fueled by many factors such as breakthroughs in communication theory, innovations in digital signal processing, advancement of silicon based VLSI technology, proliferation of internet users, heavy investment from governments and industries, and demands from consumers for reliable and convenient mobile voice and data solutions. Compared to the old analog wireless technology, the new digital technology adopts many forms of digital modulation schemes to achieve efficient use of spectrum space, low bit error rate (BER), low power consumption, and low hardware cost. Despite the fact that there are many modulation schemes, wireless transceiver architecture has remained relatively stable. In a generic wireless transceiver system, a received signal from an antenna needs to be filtered and amplified before it is down converted to a signal at much lower frequency than its carrier frequency. The down converted signal then is digitized to be processed by digital signal processor, which gives output to other digital components to translate the signal into information people can recognize. The transmitting side is the roughly the reverse of the receiving process.

A simplified block diagram of a wireless communication system is shown in Figure 1.1. On the receiver side, a radio signal comes in and gets picked up by the antenna. Then the signal is amplified by the low noise amplifier (LNA), which

suppresses system noise for the subsequent stages. The amplified signal then enters the mixer, which down-converts signal from its carrier frequency – usually in the GHz range and thus difficult to process – to a much lower frequency or directly to DC. This could be achieved in more than one step, based on system specifications and The frequency synthesizer provides the exact carrier technology limitations. frequency for the mixer. Because the carrier frequency sometimes varies from one channel to another due to changes in existing transmitting environment, the frequency synthesizer has to be able to switch to the correct frequency within a reasonable amount of time. The down-converted signal then is digitized by the analog-to-digital converter that feeds the digital signal to DSPs. The transmitting side is roughly the reverse of the receiving side. Instead of down converting the modulated signal the mixer in a transmitter up-converts it to the carrier frequency. Then the power amplifier (PA) greatly boosts the signal power while keeping the signal relatively free of distortion. Finally the signal goes out into the air from the transmitting antenna. The general transceiver architecture discussed so far excludes components that interface with digital domain.

Figure 1.1: Example of a wireless transceiver system

### 1.2 Motivation

Given the fact that every wireless transceiver has to occupy a part of the radio spectrum, it is not difficult to realize that with ever-increasing number of wireless devices being used every day, radio spectrum becomes a precious resource. Recent spectrum auction price of more than two billion dollars for a total of 120 MHz of spectrum between 1.8 GHz and 1.9 GHz [1] shows how fierce the fight is for the right to have additional spectrum space. Because of the huge cost embedded in getting additional spectrum, many innovative solutions have surfaced to increase spectrum usage efficiency such as Ultra Wide Band, which covers a wide range of spectrum (3.1GHz to 10.6GHz) with very little interference to existing signals within the spectrum [2].

One important factor that contributes to spectrum shortage is that at present commonly used commercial bipolar or CMOS technologies can only handle signals below 10 GHz. Without a more advanced technology the only solution for satisfying increasing demands is to adopt more efficient modulation schemes. However, opportunities arise when FCC opened up spectrum at K and W bands. At such high frequencies allowed bandwidth is significantly higher than that at lower frequencies. Therefore without modifying existing modulation schemes the fact that the carrier frequency is located at higher frequency implies more bandwidth for data transmission. This solves the problem of crowded spectrum usage at below 10 GHz and enables faster wireless data transmission without sacrificing the number of available channels.

Cost and ability to integrate with digital components are important indicators of a successful technology for wireless transceiver chips. The recent development of SiGe technology that claims a maximum  $f_t$  of more than 200 GHz at IBM [3] and Infineon [4] makes it possible to have transceiver circuits using Silicon based

technology operating at millimeter wave range. Successful commercial development has been underway for applications in Collision Avoidance Radar (CAR) at 77GHz where transceiver architecture is relatively simple. With the help of sophisticated Electro-Magnetic (EM) wave simulators and state-of-art circuit simulators, it can be expected that millimeter wave wireless transceiver design based on SiGe will eventually achieve the accuracy and predictability that current low frequency design based on SiGe and CMOS enjoys.

### **1.3** Current Industry Development

### 1.3.1 Development at IBM

The technology IBM has developed features a 200 GHz  $f_t$  and 280 GHz  $f_{max}$  [3]. The minimum width of the base for a HBT is 0.12  $\mu$ m, which reduces capacitive parasitics and base resistance. What sets this technology apart from other high performance SiGe process is its capability to integrate 0.13  $\mu$ m CMOS process. The presence of CMOS technology makes this BiCMOS process more desirable for system level integration and cost reduction.

Since IBM has developed their SiGe technology with a 200 GHz  $f_t$ , IBM T. J. Watson Research Center has used this technology and published several papers that present circuits for collision avoidance radar that operates in the 77 GHz range. The circuits in those published papers include a power amplifier (PA) [5], a voltage controlled oscillator (VCO), and a low noise amplifier (LNA) [6]. The circuits utilize on-chip transmission lines and capacitors for matching networks. Measured results are given to show successful implementation of those components. There are also some LNA's that operate in the 60 GHz range, which is the spectrum for short distance wireless data communication.

In those papers what is remarkable is the low noise performance for the amplifiers (roughly 4.6 dB of noise figure for 60 GHz circuits and 5.6 dB of noise figure for 77 GHz operation). For VCO's the phase noise is measured at –100 dBc/Hz at 1 MHz offset for operations from 53 GHz to 85 GHz. However, the papers do not reveal the design process. They only present the simulated and measured results along with circuit schematics. In those papers, the authors also admit discrepancies between simulation results and measurement results. Some circuits have matching characteristics that deviate from original design targets. In wireless communication, a shift in optimal operating frequency means failure in design. Therefore the importance of accurately predicting the actual performance of a high frequency circuit can never be over-stated.

### 1.3.2 Development at Infineon

Infineon is another company that has led the commercial development of advanced SiGe technology. At 2004 BCTM Infineon published a paper on its SiGe technology that has 200 GHz  $f_t$  [4]. Roughly at the same time period when IBM published its papers on SiGe circuits at V and W bands, Infineon also published a paper on 77 GHz VCO [7]. The circuits that Infineon published include a resonate-tank based oscillator at 77 GHz and a mixer at 77 GHz [8]. The circuits perform roughly at the same level as IBM counterparts.

The technology developed at Infineon features a cut-off frequency of 200 GHz, a maximum oscillation frequency of 275 GHz, and a gate delay of 3.5 ps. The emitter width is shrunk to 0.14 µm in this technology to achieve faster frequency response and smaller base resistance. In addition, deep trench is used throughout the active area to

increase isolation between signal and substrate. The technology also features TaN thin film resistor and MIM capacitor on-chip.

In the descriptions of the circuits mentioned above the authors do not have a comprehensive approach to the design of MM Wave IC. Circuits are considered purely from small signal analysis point of view. There are no discussions of passive structures that affect the outcome of measurement results. There are also little discussions on optimization issues such as choice of circuit topology and device sizes. Without a clear understanding of all the components that play crucial roles in successful implementation of MM Wave IC, the design process can be daunting and full of pitfalls. In the remaining chapters there are detailed discussions dealing with all those issues that are unaccounted for in current research publications.

## 1.4 Chapters Overview

A novel design approach to the design of integrated circuits for millimeter wave transceiver front-ends is proposed in the following chapters. The new approach considers the effects of device models, circuit topology, passive models, and many other factors that impact actual circuit performance. This design method optimizes parameters that are usually beyond the traditional scope of radio frequency integrated circuits design and the optimization process itself is formulated and enables efficient design flow for some of the key blocks in a transceiver system.

The remaining chapters are organized as the following. Chapter 2 discusses the constraints of basic circuit building blocks such as SiGe fabrication process, device modeling, and passive modeling. Chapter 3 introduces the general design methodology for successful implementation of millimeter wave transceiver front-end circuit design. This chapter discusses in general amplifier and mixer blocks. Chapter

4 discusses a 94 GHz wireless receiver mixer and active balun in SiGe. Detailed design analysis and simulation as well as measurement results are presented. Chapter 5 presents an 18 GHz direct down-conversion double-balanced mixer and an integrated mixer VCO block in SiGe. This chapter is organized similarly as the previous chapter. Chapter 6 discusses a 40 GHz receiver LNA in SiGe. Chapter 7 concludes the dissertation with future research directions.

# Chapter 2: Constraints of Millimeter Wave Front-end IC Design

### 2.1 Overview

In this chapter constraints on the design of millimeter wave front-end integrated circuits are discussed. In the traditional radio frequency integrated circuit design signal wavelength is significantly smaller than device and passive structure dimensions. Therefore research efforts have been concentrated on circuit topology improvement and high Q inductor design. However, in the domain of millimeter wave wavelength becomes comparable to passive structure and device dimensions, thus introducing additional complexity when designing circuits. Furthermore, at high frequency silicon substrate becomes extremely lossy, and isolation between active components is a serious issue for a designer to consider.

This chapter discusses constraints on successful design of millimeter wave transceiver circuits in great detail. In additional to the aforementioned constraints, issues associated with modeling and simulation are also discussed. The goal of this chapter is to present difficulties a designer faces when designing circuits at very high frequencies, which leads to the remaining chapters that propose novel design solutions to overcome these problems along with several design examples to validate the proposed solutions.

### 2.2 Constraints from SiGe Device

Constraints from SiGe active devices are due to fabrication process and device modeling. Since some key fabrication parameters are protected commercial secrets, the following discussion is based on generic SiGe process. However, the generic SiGe process and device modeling is a good approximate of real data from different foundries mainly because SiGe HBT technologies share the same fundamental principles in active device operation. The conclusions drawn from the generic process therefore is applicable to all SiGe HBT based design.

### 2.2.1 Lossy Silicon Substrate

One factor that makes some III-V process technologies such as GaAs and InP attractive for millimeter wave IC design is their low-loss substrate. Given the small dimensions of modern processing technology, devices are placed very close to each other even though each has complete different functionality in the whole system. Inevitably cross-talk between adjacent devices becomes a serious issue in analog circuits where each circuit element is assumed to be isolated from one another. In addition, lossy substrate introduces finite resistance to ground, which may attenuate critical signals.

In order to have some appreciation for the difficulties involved in dealing with substrate cross-talk and signal loss, a realistic substrate model is described here. The parameters for the substrate model closely mimics the one used for the designs discussed in this dissertation. According to [9], SiGe substrate resistivity is  $20~\Omega \cdot cm$ , and substrate thickness is  $300~\mu m$ , both of which are important in determining the substrate model for circuit analysis.

A test structure for evaluating the substrate parasitics is shown in Figure 2.1. Substrate coupling between an  $80 \mu m \times 260 \mu m$  isolation box connected to terminal A

Figure 2.1: Substrate test structure

Figure 2.2: Substrate test structure circuit model

and a large substrate contact of size 120 µm x 200 µm connected to terminal B is considered. There is a shallow trench layer between the two terminals that reduces coupling between the two areas. The trench layer material is SiO<sub>2</sub>, which has much less conductivity then p- substrate. Figure 2.2 shows a model derived from substrate material parameters. The model is verified through actual measurement. In a more realistic setting, two devices may not occupy such a large area and therefore the RC network used to model coupling between two small devices will have much less capacitance and much more resistance. At low frequencies two devices placed far away from each other may very well be isolated. However, at high frequencies even several fF of capacitance can have some impacts on isolation and matching characteristics of a circuit.

### 2.2.2 High Frequency Device Modeling

Complexity of active device modeling increases with operating frequency. At high frequency a simple model often fails to consider many secondary physical effects that are critical for design success. In RFIC design, circuits are optimized according to each device's power, noise, linearity and small/large signal parameters. All those parameters are functions of device size, biasing point, temperature, process and frequency. Those dependencies are not always linear and often have to be determined by experimental data to fit original equations that may otherwise predict results deviating from measurement data.

Accurate device modeling is the key to the success of design of integrated circuits at high frequency. However, there is also a speed and accuracy trade-off between modeling and simulation. The best scenario that could be achieved is a simple but accurate model. To this end, there has been much research in the past to perfect models for SiGe HBT at high frequencies. One model presented by [10] is one step closer to the desired solution. The model is described in Figure 2.3.

Figure 2.3: SiGe HBT high frequency model

The model depicted in Figure 2.3 derives its parameters from actual tests performed under a stable environment for a single device. For various devices sizes more tests can be run to extrapolate those parameters at a higher level of accuracy. Some parameters are linearly extrapolated and some are not. Extrapolation method depends on both actual data points and device physics, and device physics often dictates relationships between device sizes and device parameters. With all the parameters in place, simulated S-Parameters match measurement results within 10% error at 40 GHz. In addition, there is also a noise model derived from measurement results that predicts noise figures of the device within 0.1 dB at 5GHz. However, the model generates much larger error in predicting noise figure at higher frequencies due to lossy substrate.

At low frequencies, the methods mentioned above can yield a reliable set of parameters for circuit simulation. However, what is noticeable in high frequency modeling is extracted device parameters have a strong dependency on test setup. This is mainly because at high frequencies passive structures that are necessary to connect the test equipment and the device under test contribute to the overall response of parameter extraction. An improperly de-embedded structure will lead to inaccurate modeling parameters. Thus for a circuit designer who does not have control over model parameters it is important to realize limitations imposed by foundry models and avoid situations where critical circuit performance is determined by device parameters that vary a lot with temperature, process, and bias conditions.

### 2.3 Constraints from Passive Elements

Passive circuit elements are critical components of MM Wave IC design. Due to lossy substrate in SiGe technologies compared to other high resistivity substrates,

passive elements have to shield signals from substrate as much as possible. Process determines backend layer thickness and this in turn limits the vertical dimension of passive structures. Given all these limitations, a combination of microstrip and coplanar transmission line becomes the ideal choice for on-chip transmission line for MM Wave IC design. Figure 2.4 shows the difference between microstrip line, coplanar line, and the combination of both, which is the ideal choice for high frequency applications. For microstrip line it is a convenient choice for monolithic process compared to other forms of transmission lines such as rectangular wave guides or stripline where a fully enclosed shape needs to be formed. However, because microstrip line has no ground shield at the top, the wave propagation on a microstrip line is in hybrid mode, namely TE and TM. This complicates the analysis and model accuracy of microstrip lines. In order to improve on microstrip line, a coplanar structure that introduces additional ground planes to the signal line can be combined to make a semi-enclosed box. The result is EM lines mostly confined by the surrounding ground structures and thus analysis of this structure is simplified and more accurate.

Figure 2.4: Stripline, coplanar, and combination of the two

### 2.3.1 Electric-Magnetic (EM) Modeling

Choosing the right structure that simplifies analysis is just the first step towards a full solution for designing passive structures. In very high frequencies, transmission lines are extensively used because they provide better isolation and can be controlled very easily by altering their dimensions. Accurate EM modeling plays an important part in determining the robustness of passive structures. The definition of passive structures discussed here needs to include other elements such as filters, capacitors, pads, etc, elements that are located in the back-end layers. Even though resistor constitutes a passive structure, for lack of control by the designer and its resistive property, it is does not need to be simulated by EM software.

For a complex structure, simple models that predict passive structure's frequency response fairly accurately at low frequencies often fail when they try to extrapolate the results for a more complex geometry at higher frequencies. Therefore it is necessary to use mesh-based EM simulation tools to have much more accurate predictions on a specific passive structure. However, running EM numerical simulations takes a lot of resources and usually becomes unrealistic for a large chip where many passive structures are laid out. Another challenge in using EM simulation is the complexity of simulation setup. Even though several EM simulation software vendors have come up with ways to simplify structure import from CAD tools familiar to circuit designers (Ansoftlinks from Ansoft Corporation, for example), the port setup, which is responsible for mimicking the real EM wave excitation, can be complicated and error-prone. Unfortunately, an incorrect port setup usually results in wrong simulation data and renders final circuit simulation results useless.

### 2.3.2 Parasitic Extraction

In current circuit design environment there are established methods to extract circuit parasitics associated with a particular layout. The extraction part of the simulation flow is facilitated by metal layer dimensions provided by a foundry, which are fed into some predetermined formula to calculate capacitance and resistance corresponding to that specific layout. Inductance extraction is trickier in a sense that it is defined in a loop and the return path needs to be known in order to extract the proper inductance. In addition, inductance is also affected by magnetic coupling between adjacent conductors. Furthermore, inductance is a frequency dependent parameter and an inductor's geometry usually dictates the dependency. Finally, skin effect and proximity effect can also contribute to extracted inductor quality factor. There has been concentrated research on inductance extraction and one of the most efficient and effective is FASTHENRY from MIT [11]. It presents an efficient solution to inductance extraction along with many others that are commercially available. However, all the available methods are not automated at the same level of RC extraction and therefore manual intervention in the design flow is required.

At very high frequency it becomes critical for any extraction method to account for any parasitic component existing in the layout for critical signal paths. In reality, however, extraction methods competent for low frequency extraction often fail at high frequencies. The complexity associated with inductance extraction introduces additional level of uncertainty in back-annotated circuit simulation. A solution is needed for successful implementation of MM Wave IC circuit design, which has to avoid the problems of inaccuracy of regular RLC extraction programs at high frequency, and yet at the same time does not introduce significant increase in simulation time and effort.

### 2.4 Conclusion

This chapter discusses the limitations that a designer has to face in order to successfully design an MM Wave IC given today's technology. Limitations consist of several aspects in a design cycle. Models of SiGe devices at high frequencies are derived from data extracted from device under test at certain conditions. Those data are extrapolated to fit all sizes and all operating conditions. At high frequencies improper de-embedded test setup can skew device parameters by a large margin, thus making it less reliable. Silicon substrate also presents another problem because of its low resistivity. Therefore signals can easily be coupled to unwanted paths and as a result, actual measurement results will be different from that of simulation if the effect is not modeled. Passive structure is another important aspect of MM Wave IC design. Traditional low frequency extraction tools are not able to account for all the electrical and magnetic interactions but at the same time, more accurate CAD tools demand much longer simulation time and are prone to mistakes in simulation setup.

The following chapters will address issues discussed in this chapter and several design examples are presented to illustrate how optimized design methodology can make designs more robust and design process more efficient.

# **Chapter 3: Design Methodology for Millimeter Wave Integrated Circuits**

### 3.1 Overview

In this chapter a novel design methodology for millimeter wave integrated circuits is proposed. The chapter first discusses the impact of circuit topology on robustness of MM Wave IC circuit design. Two main blocks (LNA and mixer) in a wireless transceiver system are considered for this purpose. Since matching is closely related to device sizes and bias conditions, optimization is discussed next after topology choice. In addition to circuit elements, there are also layout components that need to be analyzed and optimized. Another area of the design process is simulation. Modeling of passive structures, extraction of substrate coupling as well as interconnects, and integration of simulation environment are all considered and a solution for simplifying the simulation process is proposed. The general discussion of this chapter presents a novel approach that uses numerical and circuit analysis to achieve a design methodology that can be applied to many other LNA and mixer designs that operate in the millimeter wave range in different SiGe Technologies.

# 3.2 Analysis of Circuit Topology Trade-offs

### 3.2.1 Topology for Low Noise Amplifiers (LNA)

LNA's are a crucial component in a wireless transceiver system. It is the first block in a system that provides gain to the incoming signal and therefore suppresses

noise. A good LNA must have low noise, high gain, and high linearity and consume as little power as possible. Furthermore, LNA's must achieve good input and output power match so that power transfer is maximized at desired frequencies. Since signals from antenna are single-ended, LNA needs to take single-ended data and output either single-ended or differential signals. Several configurations can be considered for this type of application.

The most common configuration for an amplifier is common-emitter. Figure 3.1 shows an NPN HBT is connected in this configuration. This is the simplest way to amplifier a signal. With its simplicity, there are many serious drawbacks to prevent its use. Consider the small signal equivalent of the common-emitter circuit on its left. For a complete small signal analysis to find the transfer function, it can be shown as

$$\frac{v_{out}}{v_{in}} = \frac{s - \frac{g_m}{c_\mu}}{c_\pi r_b [s^2 + s(\frac{1}{c_\pi \cdot r_b \| r_\pi} + \frac{1}{(c_\mu + c_\pi) \cdot Z_L \| r_0} + \frac{g_m}{c_\pi}) + (\frac{1}{c_\pi \cdot r_b \| r_\pi \cdot Z_L \| r_o})]}. \quad (3.1)$$

From this equation the complicated but complete representation of all the major small

Figure 3.1 Common-emitter configuration and simplified small signal model

signals does not give much insight into the transfer function. However, by lumping the Miller capacitance  $c_{\mu}$  to the input, the expression can be simplified to have only the sum of gain adjusted  $c_{\mu}$  and  $c_{\pi}$  as the dominant pole in this circuit. From this pole it is easy to see that the transfer function is dominated by the emitter to collector capacitance  $c_{\mu}$  and circuit power gain is significantly affected.

Another problem with this kind of configuration is that the circuit can be potentially unstable at high frequencies. This is due to the fact that the presence of  $c_{\mu}$  constitutes a feedback network for the amplifier. The K factor, which measures the stability of a given circuit by calculating S-parameters, has a component for  $S_{12}$ , which is the reverse gain path for the two port network used in deriving the expression for K. K is given as follows.

$$K = \frac{1 + |\Delta|^2 - |S_{11}|^2 - |S_{22}|^2}{2|S_{11}||S_{12}|},$$

(3.2)

where  $\Delta = S_{11} S_{22} - S_{12} S_{21}$ . If K > 1 and  $\Delta < 1$ , the circuit is unconditionally stable.

Since this common-emitter configuration has so many drawbacks, it is not realistic to use this simple configuration to design a high frequency circuit. Therefore it is worthwhile to explore other possibilities.

The next circuit configuration under consideration is common-base. Common-base configuration has the benefit of duplicating input current to the output. With the simplified small signal analysis used in the previous common-emitter configuration, the transfer function can be shown to be

$$\frac{v_{out}}{v_{in}} = \frac{g_m z_L}{1 + s c_u z_L},\tag{3.3}$$

Figure 3.2 Common-base configuration

where resistance between base and emitter and collector to emitter is omitted. What this simplified equation shows is the pole of the transfer function is solely decided by load and  $c_{\mu}$ . Compared to the common emitter case, it is obvious that the Miller effect is eliminated. In terms of stability,  $S_{12}$  can be seen as an isolation parameter for this configuration and in this case it will be the inverse of the gain transfer function. Isolation degrades with increasing frequency and the corner frequency is proportional to  $c_u Z_L$ . If  $Z_L$  is inductive, there potentially can be a point where inductance and capacitance resonate and isolation is well controlled. The conclusion from this simplified analysis shows that common base configuration is better in high frequency operation in that it does not generate Miller capacitance and the reverse isolation is better than common-emitter configuration.

One transistor configuration is the easiest to analyze. However, in order to further enhance circuit performance, other circuit topology needs to be analyzed to find an optimal solution for amplifier design.

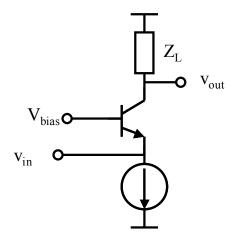

Following the discussion above, it is obvious that in high frequency operation, Miller capacitance needs to be avoided as much as possible. This in turn means the collector and the base of a transistor cannot see voltage gain. Another type of amplifier topology that avoids voltage swing on the collector-base junction is cascode. For cascode configuration, it can be seen as a combination of a common-emitter or common base stage with common-base stage. Two possible configurations are shown in Figure 3.3.

In Figure 3.3 (a) has common-emitter and common-base configuration. The benefit of this type of configuration is that  $Q_2$  shields any voltage swing seen by  $Q_1$ , therefore eliminating Miller effect. In terms of stability, the path from  $v_{out}$  to  $v_{in}$  is further enhanced by the transistor stack-up. The downside of this topology is reduced linearity due to reduced output swing, which depends on available headroom for a given power supply.

Figure 3.3 Cascode configuration for (a) common-emitter and (b) common-base

A quantitative way of illustrating its advantage is shown below in equation (3.4). Again, transfer function is used to demonstrate the effect of  $c_{\mu}$  on its frequency response. In (3.4) many simplifications are taken so that an intuitive equation can be derived to show the fact that one more transistor cascoded with a common-emitter essentially has the same transfer function as the common-base configuration. Therefore Miller effect is avoided and reverse isolation is enhanced.

$$\frac{v_{out}}{v_{in}} = -\frac{g_{m1} \cdot z_L}{1 + \frac{z_L}{r_{o1}} + sc_{\mu 2} z_L}$$

(3.4)

Another configuration is shown in Figure 3.3 (b) where the first input stage is common-base stage instead of a common-emitter stage. The cascode structure makes it have the same benefits enjoyed by (a). However, this is a redundant effort because the first common-base stage by Q<sub>1</sub> already shields the transistor from seeing the collector-base capacitance. The advantage of this type of configuration lies in input matching, which is discussed in the following sections.

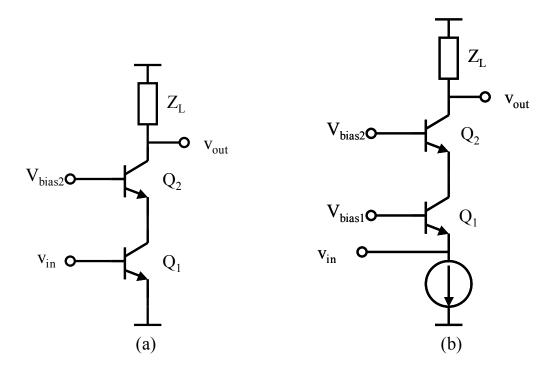

### 3.2.2 Topology for Mixers

Mixer down-converts or up-converts base band signal to the carrier frequency. Some key specs for mixer are conversion gain, linearity, noise figure, and power consumption. A good design practice should consider all aspects of mixer design and balance competing specs. Most commonly seen mixers include single balanced mixer and double balanced mixer. Single balanced mixer takes single-ended input signal and local oscillator signal and output a differential signal. Double-balanced mixer uses differential signal for input and output. The main difference between the choice of single-ended signal and differential signal is linearity. Since single ended signal does

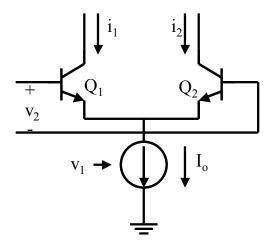

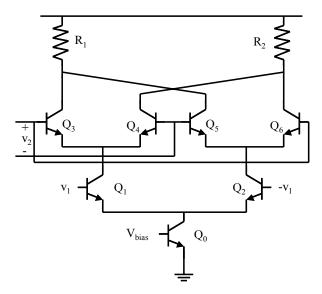

not suppress second order distortion, linearity performance is usually worse than differential operation. For this purpose, double-balanced mixer is always a better choice for linearity purpose. Another advantage represented by double-balanced design is its ability to suppress feed-through. Feed-through is a measure of unwanted signal leakage. Leakage occurs when local oscillator signal can be traced at input or output. Due to local oscillator's large input voltage swing, inevitably it will find a path to input or output. A well-designed mixer needs to suppress this unwanted signal from a topology that is independent of other circuit parameters. A single balanced mixer is shown in Figure 3.4.

In Figure 3.4  $v_1$  is the input signal and  $v_2$  is the local oscillator signal.  $v_1$  modulates current  $I_0$  supplied to transistors  $Q_1$  and  $Q_2$ .  $v_2$  also modulates currents in the differential pair  $i_1$  and  $i_2$ . The difference in the output currents from the mixer is then given by

$$i_1 = \frac{I_o}{1 + e^{-\nu_2 / \nu_T}} \tag{3.5}$$

Figure 3.4 Single balanced mixer

$$i_2 = \frac{I_o}{1 + e^{\nu_2/\nu_T}} \tag{3.6}$$

Thus, the difference in the output currents from the mixer is given by

$$i_o = i_1 - i_2 = I_o \left( \frac{1}{1 + e^{-\nu_2/\nu_T}} - \frac{1}{1 + e^{\nu_2/\nu_T}} \right) = I_o \tanh \frac{\nu_2}{2\nu_T}$$

(3.7)

This can converted to a differential voltage with equal load resistors in the collectors. For small input signals, if  $v_2 \ll v_T$ , then

$$i_o \approx I_o \frac{v_2}{2v_T} \tag{3.8}$$

Since it is assumed that the current  $I_o$  is modulated by  $v_1$ , which can be replaced by  $I_o+g_{mc}v_1$ , where  $g_{mc}$  is the transconductance of the current source, then

$$i_o = (I_o + g_{mc}v_1)\tanh\frac{v_2}{2v_T} = I_o \tanh\frac{v_2}{2v_T} + g_{mc}v_1 \tanh\frac{v_2}{2v_T}$$

(3.9)

It is obvious to see that the signal representing local oscillator  $v_2$  shows up at the output for this configuration, whereas if output can somehow become differential, the effect will be eliminated structurally.

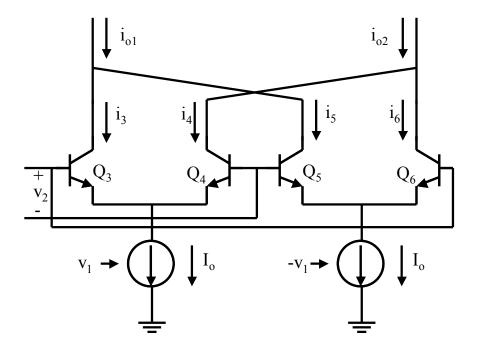

In Figure 3.5 a double balanced mixer topology is presented. Its differential structure completely eliminates feed-through from local oscillator port. Intuitively, this structure employs four switching transistors instead of two in the single balanced case, which at any moment has at least two transistors combine modulated signals from the differential input. This combination of differential signal can cancel any components that are common to each of the signal path, thus reducing feed-through from the local oscillator port.

Figure 3.5 Common-base configuration

Following the previous discussion on output current generated by mixing input and local oscillator signals, the output current for double balanced mixer can be derived easily. The output current for the second differential pair is given by

$$i_o' = i_6 - i_5 = I_o \tanh \frac{v_2}{2v_T} - g_{mc}v_1 \tanh \frac{v_2}{2v_T}.$$

(3.10)

Therefore the total differential current is

$$i_{out} = i_o - i_o' = 2g_{mc}v_1 \tanh\frac{v_2}{2v_T}$$

(3.11)

This removes the  $v_2$  feed-through term that was present in (3.9).

Another type of mixer is sub-harmonic mixer. Sub-harmonic mixer uses several different topologies such as anti-parallel pair [12], resistive mixer [13], or using passives to achieve 180-degree phase shift for input signal combined with

identical LO signal for sub harmonic mixing [14]. In the past, sub-harmonic mixers are good choice for mixers operating in the millimeter wave range since they use higher harmonic contents to mix with RF signal, thus avoids limitation set by active devices' cut-off frequency. However, the disadvantage of using sub-harmonic mixer is its low conversion gain. This is an intuitive conclusion because the higher harmonics of the mixing function has lower amplitude than the fundamental. Along with lower conversion gain, input noise cannot be effectively suppressed and therefore the SNR of such mixer suffers. With the emergence of new SiGe process that has an  $f_t$  of more than 200 GHz, circuits operating in the 60 GHz or the 77 GHz range can be biased such that active devices can still contribute significant current gain. This enables mixer topology to use the switching characteristic of active devices to get better conversion gain and SNR.

# 3.3 Matching Considerations

The concept of matching comes from the fact that maximum power transfer is achieved when source impedance and load impedance are equal if they are real or conjugate of each other if they have imaginary parts. In a wireless system antenna are designed to have an impedance of 50  $\Omega$  and this usually sets the source impedance for LNA. For components that do not have to interface with off-chip signal transfers, an arbitrary impedance can be found. This impedance is usually higher than 50  $\Omega$  to reduce the power drain associated with driving low impedance.

# 3.3.1 Matching Network

In order to match the impedance looking into a circuit to 50  $\Omega$ , impedance transformation network is needed. The idea behind impedance transformation is that for a given non-zero impedance, a network of L's and C's at low frequency or a network of stubs (transmission lines terminated to ground or open) connected in series

or in parallel with the given impedance can alter the total impedance looking into the circuit. Since there is a choice between LC matching network and stub matching network, limitations of each need to be discussed to justify the proper use of a particular network.

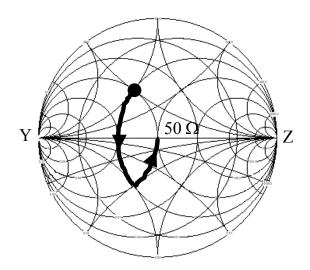

If an unmatched impedance has a real part, theoretically it can be matched to 50  $\Omega$  by any L and C network. For an unmatched impedance z = x + jy ( $x \ne 0$  or  $\infty$ ), there are several possible ways of construction a matching LC network using two elements. The first connection could be series or shunt L/C and the second can be a series or shunt L/C. In Figure 3.6, one particular example is given on Smith Chart. Smith Chart is a convenient way of designing matching network [15]. For every point on the chart, there is a corresponding impedance. The Y circles represent a shunt connection and the Z circles represent a series connection. For an inductor connected in series with a load, the total impedance is moved clockwise on the Z circle. For a capacitor connected in series with a load, the total impedance is moved counter-clockwise. Shunt connected inductor and capacitor follows similar rules to move around Smith

Figure 3.6 Smith Chart with a matching example

Chart. In Figure 3.6, it is easy to see that for any given point, there is always a path to the center of the circle, which represents  $50 \Omega$ .

Mathematically it can be proved that for a complex number with a real part, combinations of series and/or shunt connection of  $I/j\varpi C$  and  $j\varpi L$  will create a value that has only a real part. However, one limitation of the LC network is that the inductance and capacitance of on-chip components are limited to certain values due to their limited dimensions. [16] gives a mathematical expression on how large an area on Smith Chart covers given a specific source and load impedance and maximum and minimum values of L and C.

For millimeter wave applications, however, simple on-chip inductors and capacitors have many secondary effects and usually those secondary effects cannot be ignored. For spiral inductors typically used in radio frequency applications, an accurate model needs to consider many secondary effects such as skin effect, proximity effect, substrate capacitance, metal resistance, and interline/cross-under coupling capacitance [17]. As its experimental results show, at high frequencies on-chip inductors have diminished inductance due to capacitive coupling. Skin effect also reduces the quality factor (Q) of inductors to a level that is not useful for most of the applications. According to these limitations, spiral inductors are not suited for millimeter wave circuits.

On the other hand, stub matching provides an excellent way of constructing a matching network on-chip. Because operating frequencies for millimeter wave range are in the tens of Gig hertz range, signal wavelength is reduced to dimensions that are comparable to the on-chip device size, which enables on-chip stub matching network to be implemented. In a typical SiGe process, distance between the top layer metal and the bottom layer is roughly in the range of 10's of microns. With a dielectric constant of 4.1 for SiO<sub>2</sub>, it is straightforward to calculate the unit inductance and

capacitance for a transmission line that has both side and bottom ground shield. For a transmission line, the wavelength of a signal traveling through is given by

$$\lambda = \frac{2\pi}{\omega\sqrt{LC}}\,,\tag{3.12}$$

where L and C is unit inductance and capacitance. As frequency increases, signal wavelength is shortened. Experimental data show that for a 100 GHz signal the wavelength on a transmission line can be 1500  $\mu$ m [18], which is comparable to the chip size and can be conveniently implemented on chip.

With its feasibility established, on-chip transmission line provides many benefits that regular passive devices cannot. As mentioned earlier, the benefit of having transmission line on-chip is its use of shields to reduce coupling to substrate and other components. Furthermore, transmission line offers a flexible way of matching a particular impedance by using a tapered line, which directly transforms one impedance to another without additional matching network. One difficulty associated with on-chip transmission line is the return path. Without a ground plane, the return path goes through substrate and because substrate has frequency dependent parameters that are hard to define precisely, leading to large errors in its modeling behavior [19]. With a ground shield, transmission lines behave mostly the way models predict, proving the usefulness of the shield.

To further enhance the quality of transmission line's Q, other techniques have been reported. One of such techniques is to have a floating bottom shield instead of a connected bottom shield [20]. This technique predicts that by using floating metals to link equally opposing electric field emitting from the passive component and its current-return path, the floating shield stays at 0 V without an explicit ground reference. This overcomes the difficulty of designing a 0 V (explicitly) grounded

shield on silicon-based MM Wave IC. Floating shields for passive devices are physically separated and thereby minimize unwanted coupling between devices.

In order to do stub matching, Smith Chart is an intuitive way to derive stub length. With transmission lines, a load impedance can travel on a constant SWR circle, which is concentric with Smith Chart. For shorted stub, it behaves like an inductor on Smith Chart. As its length increases, it moves along clockwise following the constant reactance circle. Similarly, an open stub resembles a capacitor and it moves along the constant susceptance circle.

# 3.3.2 Active Device Matching Considerations

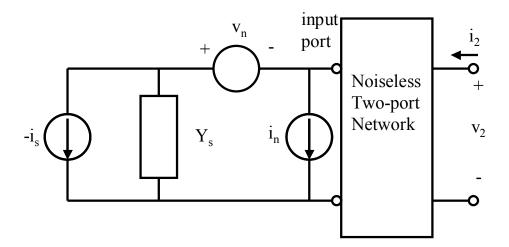

Even though matching network can transform almost any given input impedance to match that of the source, there is an additional dimension of issues for designing active devices. As discussed before, the idea of having a properly matched input impedance maximizes power transfer from source to load. In an amplifier or a mixer design, power transfer is not the only spec that determines performance. Noise

Figure 3.7 Noise model for calculating amplifier's noise figure

consideration is equally important in evaluation of a front-end component. In order to optimize noise performance of a given amplifier, the concept of noise matching needs to be introduced. To define a noise performance parameter, the concept of noise figure (NF) is used. NF is defined as the ratio of the total available noise power at the output of a network to the available noise power at the output due to thermal noise from the input termination resistor.

Figure 3.7 describes a generic noise model for a two-port network. Noise sources are lumped to the input and the two-port network itself is noiseless for simplicity.

The total output noise power is proportional to the mean square of the short-circuit current  $(\overline{i_{sc}^2})$  at the input port of the noise free amplifier, while the noise power due to the source alone is proportional to the mean square of the source current  $\overline{i_s^2}$ . Therefore the NF is given by

$$F = \frac{\overline{i_{sc}^2}}{\overline{i_s^2}} \,. \tag{3.13}$$

Since

$$i_{sc} = -i_{s} + i_{n} + v_{n}Y_{s}, (3.14)$$

it follows that the mean square of  $i_{sc}$  is given by

$$\overline{i_{sc}^{2}} = \overline{(-i_{s} + i_{n} + v_{n}Y_{s})^{2}} = \overline{i_{s}^{2}} + \overline{(i_{n} + v_{n}Y_{s})^{2}} - 2\overline{i_{s}(i_{n} + v_{n}Y_{s})}$$

(3.15)

Since the noise from the source and the noise from the network are uncorrelated, the term that contains the multiplication of  $i_n$  and  $i_s$  has to be zero. After shifting some terms around, equation (3.13) becomes

$$F = 1 + \frac{\overline{(i_n + v_n Y_s)^2}}{\overline{i_s^2}}$$

(3.16)

There is some correlation between the external source  $v_n$  and  $i_n$ . So in can be written as a composition of two parts, one correlated to  $v_n$  and one that is not. To link in and  $v_n$ , another coefficient  $Y_c$  can be defined such as the correlated part of in is  $Y_cv_n$ . Substitute the new expression for in into (3.16). The new expression for F becomes

$$F = 1 + \frac{\overline{(i_{nu} + (Y_c + Y_s)v_n)^2}}{\overline{i_s^2}}$$

(3.17)

The noise produced by the source is related to the source conductance by

$$\overline{i_s^w} = 4kT_oG_sB, \qquad (3.18)$$

where  $G_s = \text{Re}[Y_s]$ . The noise voltage can be expressed in terms of an equivalent noise resistance  $R_n$  as

$$\overline{v_n^2} = 4KT_o R_n B \tag{3.19}$$

and the uncorrelated noise current can be expressed in terms of an equivalent noise conductance  $G_u$ , which is

$$\overline{i_{nu}^2} = 4kT_oG_uB \tag{3.20}$$

Substitute (3.18), (3.19), and (3.20) into (3.17) with  $Y_c = G_c + jB_c$  and  $Y_s = G_s + jB_s$  and the new expression for F is

$$F = 1 + \frac{4kT_oG_uB + |G_s + jB + G_c + jB_c|^2 4kT_oR_nB}{4kT_oG_sB}$$

(3.21)

$$=1+\frac{G_u}{G_s}+\frac{R_n}{G_s}[(G_s+G_c)^2+(B_s+B_c)^2]$$

(3.22)

To minimize noise contribution,  $B_s$  needs to be equal to  $-B_c$ . Furthermore, the expression can be minimized by choosing a  $G_s$  that gives the local minimum for the equation. To derive this local minimum, a derivative of F with respect to  $G_s$  can be found and the expression for  $G_s$  that gives the minimum value of F is

$$G_s = \sqrt{G_c^2 + \frac{G_u}{R_n}} \tag{3.23}$$

In order to satisfy both maximum power transfer and minimum noise figure, the input impedance looking into the active devices needs to be designed in such way that when matching network is attached it can achieve simultaneous power and noise match. Because noise match equations derive optimal values for the source impedance, and source impedance is usually fixed to 50  $\Omega$ , the design problem becomes how to find an input impedance for a given circuit that has optimal noise and power impedance located at points symmetrical to the x-axis.

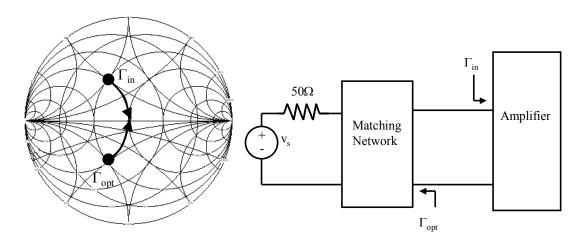

Figure 3.8 demonstrates the ideal case of simultaneous power and noise match. For a two-port network, there exists a value for optimal source reflection coefficient  $\Gamma_{opt}$ . Since this value refers to impedance looking into the matching network from the amplifier, and  $\Gamma_{in}$  refers to the impedance looking into the amplifier, the two values have to be symmetrical around the x-axis on the Smith chart, i.e.  $\Gamma_{opt} = \text{conj}(\Gamma_{in})$ .

With the goal of achieving simultaneous power and noise match, the next step would be to find the relationship between optimal source reflection coefficient and input impedance. Since both values depend on device size, circuit topology, bias

Figure 3.8 Ideal simultaneous noise and power match

conditions, and process technology as well as ambient temperature, and their correlation is not intuitive, it is useful to derive a formula that links both values with all the parameters that a designer has control over. Thus design time and accuracy can be greatly improved.

First, the most important parameter for this type of optimization is circuit topology. Different circuit topology results in changes in the inherent connection between input impedance and optimal source reflection coefficient, given that all other parameters are held constant. Therefore it is imperative to fix the design within a universally applicable topology so that a designer does not need to derive the complex formula every time a design changes.

As mentioned earlier, among many amplifier topologies, common emitter and common base with a cascode device is the most useful topology for MM Wave IC application. Therefore it is useful to formulate the relationship between optimal noise match and power match for those two configurations.

First, it is useful to derive input impedance for a common-emitter with cascode configuration. For the circuit in Figure 3.3 (a), the input impedance  $Z_{in}$  looking into the base of  $Q_1$  is

$$Z_{in} = r_{b1} + \frac{r_{\pi 1}}{1 + j\omega r_{\pi 1} [c_{\mu 1} (1 + \frac{g_{m1}}{g_{m2}}) + c_{\pi 1}]}$$

$$= r_{b1} + \frac{r_{\pi 1}}{1 + \omega r_{\pi} c_{lump}} - j \frac{r_{\pi}^{2} \omega c_{lump}}{1 + \omega^{2} r_{\pi}^{2} c_{lump}^{2}}$$

(3.24)

where  $c_{lump} = c_{ul}(1+g_{ml}/g_{m2})+c_{\pi l}$ . The expression for  $Z_{in}$  clearly shows that the effect of cascode has minimum impact on input impedance.

To derive an expression for the optimal source reflection coefficient, there need to be a noise model for SiGe HBT device and an analytical expression for input referred noise. It is possible to include the cascoded device's noise model into the

final equation, however, the cascode transistor  $Q_2$  has a current gain of 1 and this forces the current coming into the emitter of  $Q_2$  to equal the current coming out of the collector of  $Q_2$ . Therefore a noise current source between the collector and the emitter does not change output noise [21]. Therefore, the cascode device can be treated as a noiseless network connected to a noise common-base stage.

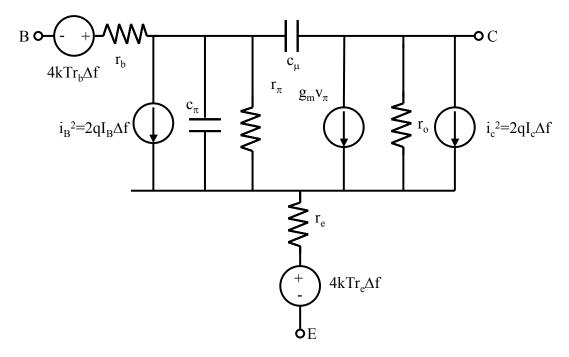

Figure 3.9 shows the small signal and noise model of a SiGe HBT transistor. This model can be used to derive the minimum noise figure as well as  $\Gamma_{opt}$ . From [22], the theoretical equations for noise related parameters are given below.  $R_n$  is noise resistance,  $Y_{sop}$  is the optimal source impedance for noise matching,  $F_{min}$  is the minimum noise figure, and  $Y_{xy}$  is the Y parameter of the noiseless two-port network.

$$R_n = C_{A11} (3.25)$$

Figure 3.9 Noise model for SiGe HBT

$$Y_{sop} = G_{sop} + jB_{sop} = \sqrt{\frac{C_{A22}}{C_{A11}} - (\frac{\text{Im}\{C_{A12}\}}{C_{A11}})^2} + j\frac{\text{Im}\{C_{A12}\}}{C_{A11}}$$

(3.26)

$$F_{MIN} = 1 + 2(\text{Re}\{C_{A12}\} + C_{A11}G_{sop})$$

(3.27)

$$C_{A11} = \frac{\overline{v_n^2}}{4kT\Delta f} = \frac{\overline{i_c^2}}{4kT\Delta f |Y_{21}|^2} + (r_E + r_B)$$

(3.28)

$$C_{A21} = C_{A12}^* = \frac{\overline{v_n^* i_n}}{4kT\Delta f} = \frac{Y_{11}\overline{i_c^2}}{4kT\Delta f |Y_{21}|^2}$$

(3.29)

$$C_{A22} = \frac{\overline{i_n^2}}{4kT\Delta f} = \frac{|Y_{11}|^2 \overline{i_c^2}}{4kT\Delta f |Y_{21}|^2}$$

(3.30)

In these substitutions,  $i_{c2}$  is the shot noise due to collector current and  $i_{B2}$  is the shot noise due to base current.  $r_E$  and  $r_B$  are internal emitter and base resistance respectively. With all the parameters in place, the general equation for  $Y_{sop}$  can be derived.

$$Y_{sop} = \sqrt{\frac{I_B |Y_{21}|^2 + I_C |Y_{11}|^2}{2V_T |Y_{21}|^2 (r_E + r_B) + I_C} - \left(\frac{I_c \operatorname{Im}\{Y_{11}\}}{2V_T |Y_{21}|^2 (r_E + r_B) + I_C}\right)^2} - j \frac{I_C \operatorname{Im}\{Y_{11}\}}{2V_T |Y_{21}|^2 (r_E + r_B) + I_C}}$$

(3.31)

$$F_{MIN} = 1 + \frac{I_C}{V_T \mid Y_{21} \mid^2} \left( \sqrt{\left[1 + \frac{2V_T \mid Y_{21} \mid^2 (r_E + r_B)}{I_C}\right] \left[ \mid Y_{11} \mid^2 + \frac{I_B \mid Y_{21} \mid^2}{I_C} \right] - \left( \operatorname{Im} \{Y_{11}\} \right)^2} + \operatorname{Re} \{Y_{11}\} \right)$$

(3.32)

Equation (3.31) gives the relationship between Y parameters of a two-port network and the optimal source impedance. As discussed earlier, the ideal case is when  $Z_{sopt} = Z_{in}^*$ . But with the above equation, it is difficult to directly use it to find the optimal

matching point.  $Y_{sop}$  can be transformed to  $Z_{sop}$  where it consists of a real and imaginary part. The process of this transformation is omitted because it is purely mathematical manipulation. The result of this transformation is that the real part of  $Z_{sop}$  scales with the inverse of emitter length and decreases with increase in frequency.

Another observation from this transformation the relationship between the sign of the imaginary part of  $Z_{in}$  and  $Z_{sop}$  can be derived relative to each other. To have a good noise match, those two imaginary parts need to have opposite signs. Mathematical manipulation of the expressions gives that  $S_{II}$  of the two-port network needs to remain in the left half of the Smith chart.

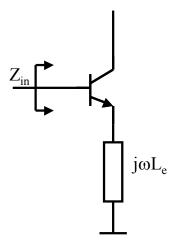

The main problem with (3.31) is that  $S_{II}$  of a SiGe HBT device is related to  $Z_{sop}$ . From optimization point of view, this is the worst case because with so many variables involved and many circuit specs to meet, completely correlated circuit parameters are difficult to be simulated or solved independently. A designer usually have limited resources on simulation and it is reasonable only if there are two or three variables to be simulated at the same time. Therefore it is important to devise a way so that the two parameters become less correlated or uncorrelated. In this particular case, an emitter degenerated inductance is sought to provide this desired property.

Figure 3.10 shows the input stage modified but an emitter degeneration inductor. Ideally this inductor does not add additional noise, therefore the minimum NF is not affected. With the addition of the degeneration inductor, the new input impedance becomes

$$Z_{in} = r_{b1} + \frac{r_{\pi 1}}{1 + j\omega r_{\pi 1} [c_{\mu 1} (1 + \frac{g_{m1}}{g_{m2}}) + c_{\pi 1}]} + j\omega L_e$$

(3.33)

Figure 3.10 Emitter degenerated input stage

$L_e$  directly influences the imaginary part of the input impedance only. It can also be demonstrated that  $L_e$  only changes the imaginary part of  $Z_{sop}$ , leaving the matching of the real part for other circuit parameters. Given the difficulty in solving the equations for a pure quantitative solution, computer simulation is needed to find the exact solution for optimal bias point and device sizes for low noise operation. The derivation above provides the first qualitative understanding of matching requirements.

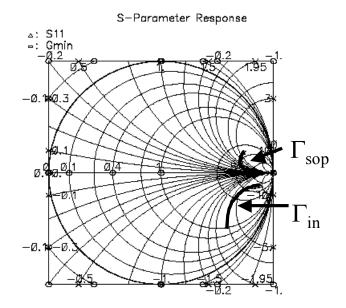

(3.31) and (3.32) predict that noise figure is a function of bias current and device size. It is useful then to use a sample device constructed in the cascode configuration to illustrate the influence that those parameters have on device noise performance. Figure 3.11 shows the effect of sweeping  $L_e$ , the emitter degeneration inductance from 0 to 1 nH, on  $\Gamma_{sop}$  and  $\Gamma_{in}$  for a transistor biased at 1 mA with emitter length at 0.12  $\mu$ m and width at 2.4  $\mu$ m. The circuit is simulated at 40 GHz. As indicated by previous derivation,  $L_e$  enables a more flexible matching optimization for  $\Gamma_{sop}$  and  $\Gamma_{in}$ .  $\Gamma_{in}$  changes more rapidly than  $\Gamma_{sop}$ , which facilitates matching.

Figure 3.11 Effect of sweeping degeneration inductance

Figure 3.12 shows the effect of device geometry and bias current on minimum

Figure 3. 12 CE stage device size and bias current on  $NF_{\text{min}}$

noise figure. Various devices are chosen and the x-axis shows the bias current. It is interesting to note that for each device size, there exists a range for bias current to have a relatively constant minimum noise figure. When bias current is too little, a transistor does not have enough current gain to offset the internal noise. When bias current is too large, base and collector shot noise dominates and noise figure goes up abruptly. Another fact revealed by Figure 3.12 is for this particular process noise due to base resistance is not a dominant noise source. Theoretically base resistance is a function of emitter length. As emitter length increase, base resistance goes down due to larger area to carry current. In this plot, the smallest device has the lowest noise figure, which proves the fact that noise power due to base resistance is small.

The above discussion has concentrated on common-base cascode configuration for low noise amplifier. The other suitable topology which uses common base as the first gain stage can be analyzed in a similar way. For simplicity reasons the equations are not given here. Simulation with the same device size and bias current for minimum noise figure in Figure 3.13, however, shows that for the same device size

Figure 3.13 CB stage device size and bias current on NF<sub>min</sub>

and bias current, the common base configuration has a higher minimum noise figure. This is mainly due to the fact that collector shot noise directly appears at the input whereas in the common emitter case, it needs to be transformed to the equivalent noise source. In doing so, the transconductance gain needs to be removed to reflect the fact that the real noise source is not at the input.

In terms of matching for optimal noise and power, the common base configuration is harder to achieve because there is no similar leverage such as  $L_e$  in the common emitter case that can change one parameter a lot more effective than others, which simplifies optimization tasks. But given the fact that common base input stage has a low input impedance, matching to  $50~\Omega$  is relatively easy.

# 3.3.3 Circuit Optimization

Given the previous discussions on circuit topology trade-offs and matching considerations, a general procedure for circuit optimization is outlined. A topology is chosen first according to the frequency and specific design requirements. At millimeter frequency range there are not many options since additional devices will add more noise and some topologies that rely on feedback are vulnerable to many parasitic effects that can change the loop dynamics. Once a topology is fixed, the next step would be to adjust device sizes and bias current, as those two parameters have the most dominant effects on noise and power match. In the case of common-base input stage, the use of emitter degeneration inductance decouples otherwise strongly correlated circuit parameters and thus simplifies optimization tasks. However, in the case of common-base configuration, minimum noise figure is higher and optimization is more difficult. This optimization process involves simulation over different device sizes and bias currents until a simultaneous match is found.

# 3.4 Physical Layout Considerations

In RFIC design, a good circuit on schematic is only the first step. A poorly designed layout can easily ruin a circuit that has good simulation results. In order to have a successful silicon chip, a designer has to pay attention to various components during layout. For MM Wave IC design, many issues are unique because the wavelength of the signal approaches the dimensions of circuit components, thus demanding more rigorous layout disciplines.

Most RF circuitry does not involve many transistors in the design. In addition, the presence of passives requires large space to be dedicated to those space-hungry components such as inductors and transmission lines. As a result, devices from different gain stages tend to be isolated from each other. It is a common practice to have the shortest distant from the input pad to the output pad so that unwanted interference or parasitics can be avoided.

Substrate contacts are very crucial in isolating active devices and reducing cross-talk. There have to be substrate contacts around sensitive components to maintain a good ground. A good practice is to arrange a network of substrate contacts and make a large ground plane that covers as much space as possible on-chip with substrate contacts connected to this large ground.

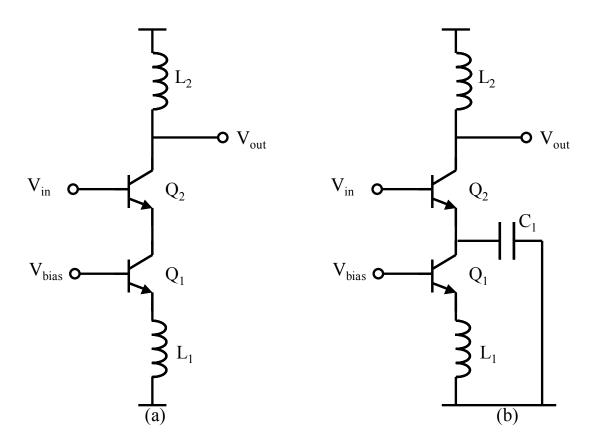

Vias are also important in that the actual length of a via or vias can approach a large fraction of the wavelength. If unaccounted for, it will change measurement data and make simulation results less accurate. In a typical SiGe process the distance from a top layer metal, usually thick metal with good conductivity and small ground capacitance, to the device is approximately of 10  $\mu$ m. For a signal at 100GHz a quarter  $\lambda$  on-chip is roughly 400  $\mu$ m. With both vias needed to get signal up to the top layer metal and down requires 20  $\mu$ m of distance, 5% of a quarter wavelength. As