## USING DYNAMIC BINARY INSTRUMENTATION TO CREATE FASTER, VALIDATED, MULTI-CORE SIMULATIONS

#### A Dissertation

Presented to the Faculty of the Graduate School of Cornell University

in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

by Vincent Michael Weaver May 2010 © 2010 Vincent Michael Weaver ALL RIGHTS RESERVED

# USING DYNAMIC BINARY INSTRUMENTATION TO CREATE FASTER, VALIDATED, MULTI-CORE SIMULATIONS

#### Vincent Michael Weaver, Ph.D.

#### Cornell University 2010

The Memory Wall continues to be a problem with modern systems design. While the steady increase in processor speeds has abated somewhat, Moore's Law continues to provide more transistors to chip designers. This leads to an increase in the number of processors and threads located per chip, which increases the demands on memory systems. Current simulation technology is not able to keep up, leading to sacrifices in methodology and accuracy in order to get results in reasonable time.

Because cycle-accurate simulators are so slow, various methods for reducing execution time can be used. Unfortunately these methods can introduce variations in results of between 10-50% when compared to full reference input sets. Limitations of academic simulators also constrain the architectures under study, with results generated for obsolete or uninteresting systems.

We analyze the performance and accuracy of various limited-execution methodologies. We investigate how deterministic execution affects the measurement of error. We then evaluate using Dynamic Binary Instrumentation (DBI) as an alternative to cycle-accurate simulation. We compare our results to actual systems using hardware performance counters. We look first at a simple 32-bit RISC system, and then look at more complex 64-bit x86 based systems. Finally we investigate the feasibility of using the same methodology for modern multi-processors simulations.

#### **BIOGRAPHICAL SKETCH**

Vincent Weaver was born in 1978 and grew up in Joppatowne, Maryland. He attended Joppatowne Elementary and Magnolia Middle schools before moving on to The John Carroll School. He received his B.S. in Electrical Engineering from the University of Maryland College Park in December of 2000. After graduation he briefly worked at Frontpath, a maker of tablet PCs located in Billerica Massachusetts. The dot-com bust caught up with the company, and after a round of layoffs Vince returned to Maryland and worked as a contractor for the U.S. Army creating web front-ends for legacy Fortran applications. In the Fall of 2003 he entered the M.S./Ph.D. program at Cornell University. He obtained a M.S. degree in Electrical and Computer Engineering from Cornell in January of 2009 and his Ph.D. in May of 2010. Vince is a Linux enthusiast who is often accompanied by guinea pigs. He enjoys retro-computing and can program in over 20 types of assembly language.

To Kristina and Elena, for their unfailing support.

ःःः ध्रिष्ठं

#### **ACKNOWLEDGMENTS**

First and foremost I would like to thank my advisor, Sally McKee, for her leadership and guidance throughout my time in grad school. Without her help and support none of this would have been possible. Most notable is her amazing ability to accumulate computing clusters, without which this work would have not been finished in a reasonable amount of time. I would like to thank my other committee members, Rajit Manohar and David Albonesi for their insights and feedback that have been instrumental in improving this thesis. In addition I would like to thank Bruce Jacob from the University of Maryland. It was his computer organization and computer architecture classes that set me on the path that resulted in this research.

I also would like to thank all of the members of the Fusion group, past and present, for all their help and support. This includes Martin, Pete, Brian, Chris, Cat, Karan, and Major as well as many others who were not around as long but were just as important.

This work was helped by many open source software projects. I would like to thank the developers of the Linux kernel, especially Linus Torvalds. I would like to thank the perfmon2 developers, especially Stéphane Eranian, as well as the developers of Qemu, Valgrind, and m5.

Additional thanks to the Intel Corporation for donating processors which are used in our Sampaka and Domori clusters.

Part of this work is supported by the National Science Foundation under Grants 0509406 and 0325536 as well as by NSF CCF Award 0702616 and NSF ST-HEC Award 0444413.

## TABLE OF CONTENTS

|   | _     | ' 1                                      | iii |

|---|-------|------------------------------------------|-----|

|   |       |                                          | iv  |

|   | Ack   | nowledgments                             | V   |

|   |       | e of Contents                            | vi  |

|   | List  | of Tables                                | Х   |

|   | List  | of Figures                               | xii |

| 1 | Intro | oduction                                 | 1   |

| 2 | Rela  | ited Work                                | 5   |

|   | 2.1   | Reduced Execution Validations            | 5   |

|   | 2.2   | SimPoint Validation                      | 6   |

|   | 2.3   | Performance Counter Validation           | 9   |

|   | 2.4   |                                          | 11  |

|   |       |                                          | 11  |

|   |       |                                          | 11  |

|   |       | 2.4.3 Qemu                               | 12  |

|   |       | 2.4.4 TAXI                               | 12  |

|   | 2.5   | Multi-core Simulation                    | 12  |

|   |       | 2.5.1 CMP\$im                            | 13  |

|   |       | 2.5.2 Other                              | 13  |

|   | 2.6   |                                          | 14  |

|   | 2.7   | Simulator Validations                    | 15  |

|   | 2.8   | Multi-processor Phase Detection          | 17  |

|   | 2.9   | Deterministic Execution                  | 18  |

|   | 2.10  | Performance Counter based CPI Prediction | 19  |

| 3 | Met   | hods of Reducing Simulation Time         | 21  |

|   | 3.1   | · · · · · · · · · · · · · · · · · · ·    | 22  |

|   | 3.2   |                                          | 23  |

|   | 3.3   |                                          | 23  |

|   | 3.4   | Statistics-based Sampling                | 23  |

|   | 3.5   | SimPoint                                 | 24  |

|   |       | 3.5.1 BBV Generation                     | 26  |

|   |       | 3.5.2 x86 Evaluation                     | 27  |

|   |       | 3.5.3 x86_64 Results                     | 36  |

|   |       | 3.5.4 Cross-Platform MIPS Results        | 38  |

|   |       | 3.5.5 Summary                            | 42  |

|   | 3.6   |                                          | 43  |

| 4 | Sing | le-Core Vali | dation Concerns                    | 45  |

|---|------|--------------|------------------------------------|-----|

|   | 4.1  | Hardware F   | Performance Counters               | 45  |

|   |      | 4.1.1 Perfo  | ormance Counter Evaluation         | 47  |

|   |      | 4.1.2 Sour   | ces of Hardware Counter Variation  | 49  |

|   |      | 4.1.3 Cou    | nter Variation Findings            | 52  |

|   |      |              | n-machine results                  | 53  |

|   |      | 4.1.5 Inter  | -machine Results                   | 54  |

|   | 4.2  | Determinist  | ic Execution                       | 57  |

|   |      | 4.2.1 Virtu  | aal Memory Layout                  | 57  |

|   |      |              | em Effects                         | 61  |

|   |      |              | rces of DBI Tool Variation         | 61  |

|   | 4.3  | Summary .    |                                    | 64  |

| 5 | 32-E | it RISC Resi | ults                               | 65  |

|   | 5.1  |              | -accurate Simulator                | 68  |

|   | 5.2  |              | Iardware                           | 70  |

|   | 5.3  |              | Simulator                          | 71  |

|   | 5.4  |              | 5                                  | 72  |

|   | 5.5  |              |                                    | 73  |

|   | 0.0  |              | olute Results                      | 73  |

|   |      |              | tive Results                       | 78  |

|   |      | _            | mary                               | 81  |

| 6 | 61_B | it CISC Resi | ulte                               | 84  |

| U | 6.1  |              | differences                        | 84  |

|   | 6.2  |              | U Features                         | 85  |

|   | 6.3  |              | ns                                 | 86  |

|   | 6.4  |              | Methodology                        | 90  |

|   | 0.1  |              | rind DBI-based Simulator           | 90  |

|   |      | _            | Cycle-accurate Simulator           | 91  |

|   |      |              | rence Hardware                     | 93  |

|   |      |              | chmarks                            | 95  |

|   | 6.5  | Absolute Re  |                                    | 95  |

|   | 0.0  |              | se Behavior Results                | 97  |

|   |      |              | nstruction Cache                   | 97  |

|   |      |              | Accesses per Thousand Instructions | 98  |

|   |      |              | Pata Cache                         | 99  |

|   | 6.6  |              |                                    | 103 |

|   | 6.7  |              | lictor                             | 104 |

|   | 6.8  | CPI          |                                    | 105 |

|   | 6.9  | 011          | sults                              | 106 |

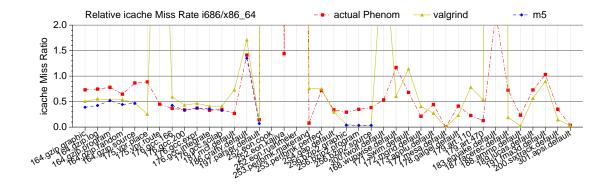

|   | 0.7  |              | nstruction Cache                   | 106 |

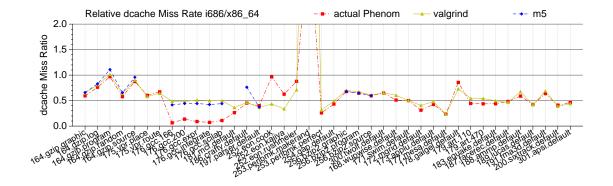

|   |      |              | Pata Cache                         | 107 |

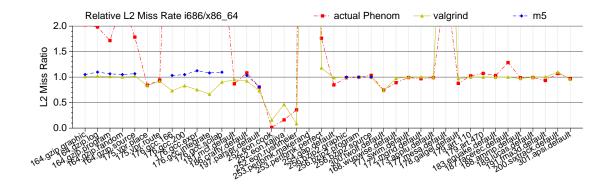

|   |      | 693 I2C      |                                    | 107 |

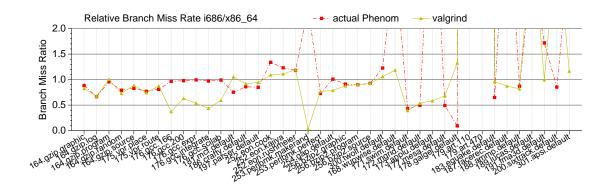

|   | 6.9.4 Branch Predictor                                                                                                                                                                                                              | 109                             |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 7 | Multi-Core Validation Concerns7.1 Performance Counters7.2 Deterministic Execution                                                                                                                                                   |                                 |

| 8 | Multi-Core Results         8.1       Methodology          8.1.1       Performance Counters          8.1.2       DBI Simulation          8.1.3       Cycle-accurate Simulation          8.2       Results          8.3       Summary | 115<br>115<br>116               |

| 9 | Conclusion and Future Work9.1 Results Summary9.2 Future Work9.3 Conclusion                                                                                                                                                          | 122                             |

| A | A.1 Benefits of Code Density                                                                                                                                                                                                        | 124<br>127<br>129<br>133<br>135 |

| В | Cache Latencies                                                                                                                                                                                                                     | 138                             |

| C | Instruction Counts                                                                                                                                                                                                                  | 141                             |

| D | Simulation Timings                                                                                                                                                                                                                  | 153                             |

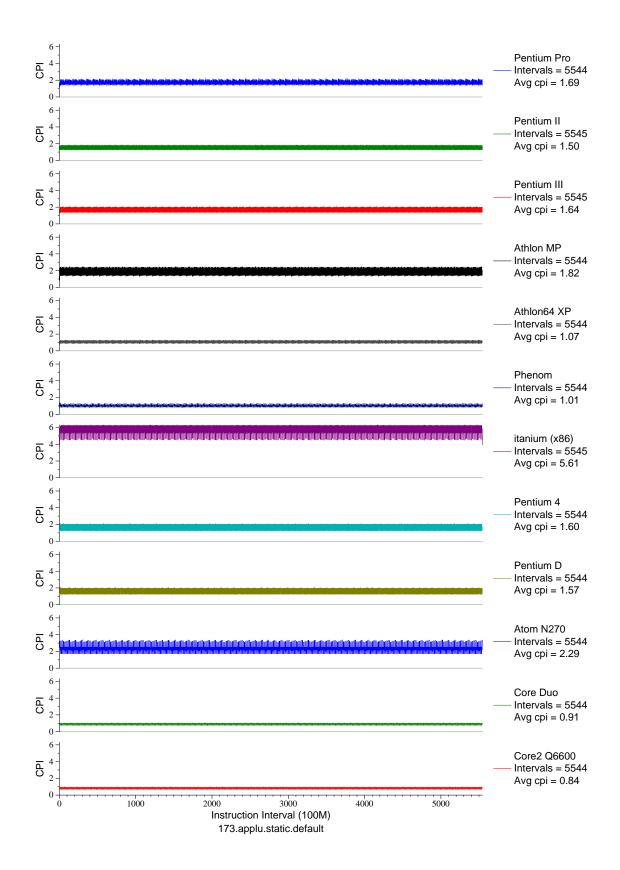

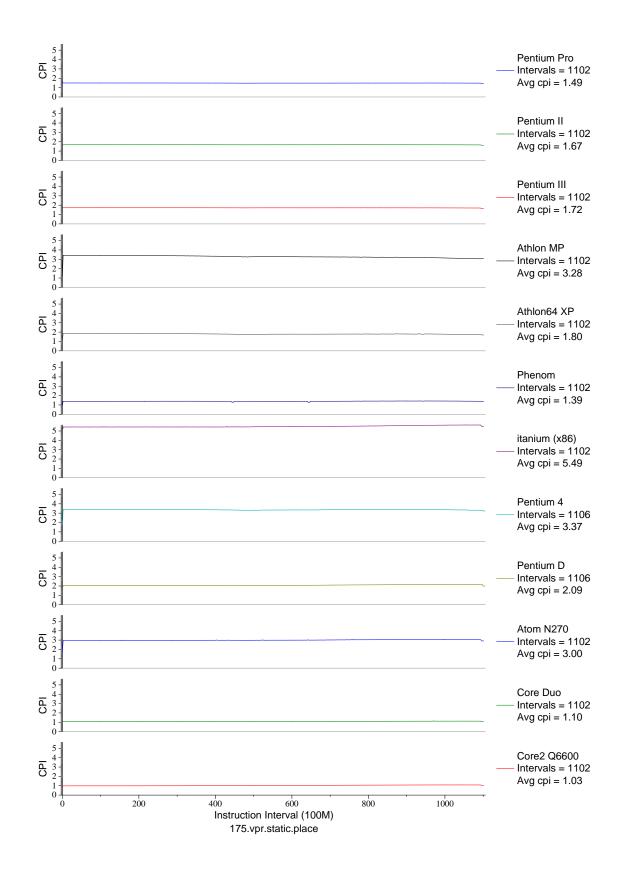

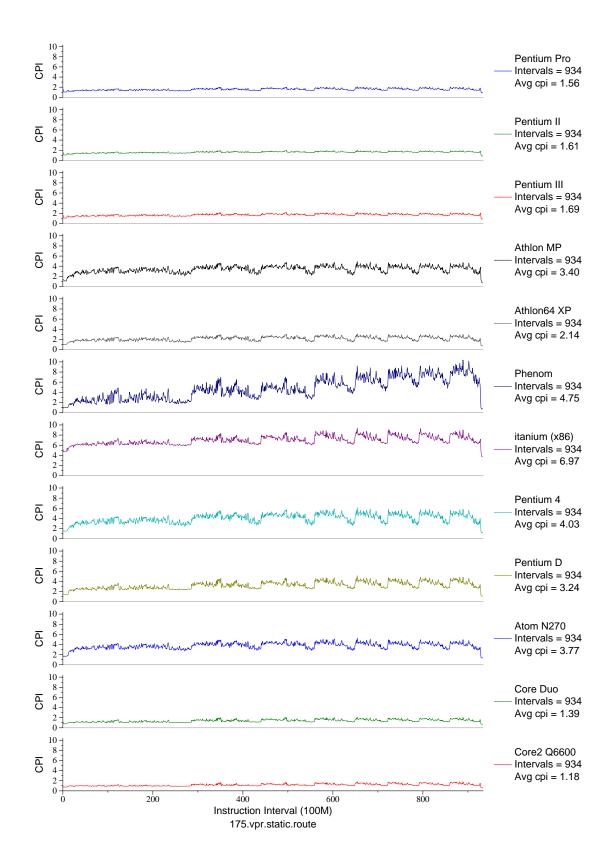

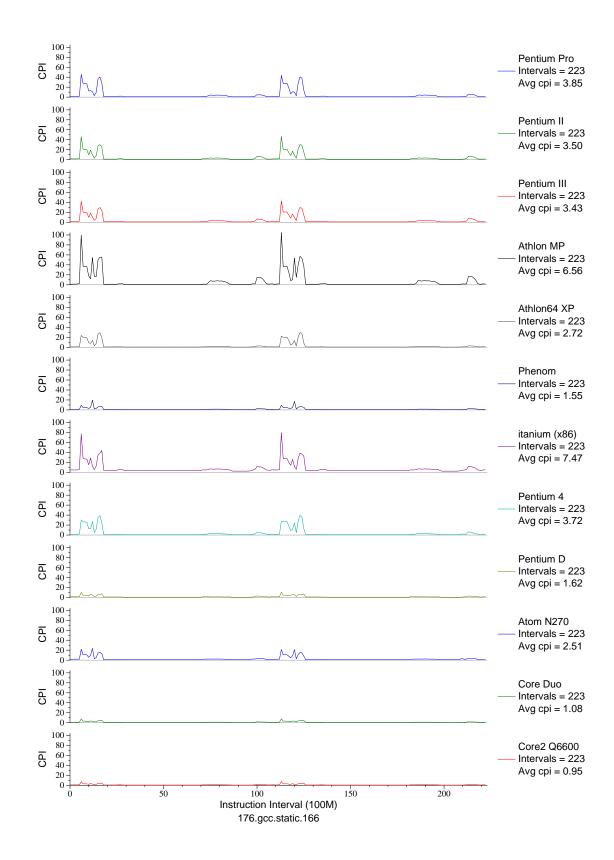

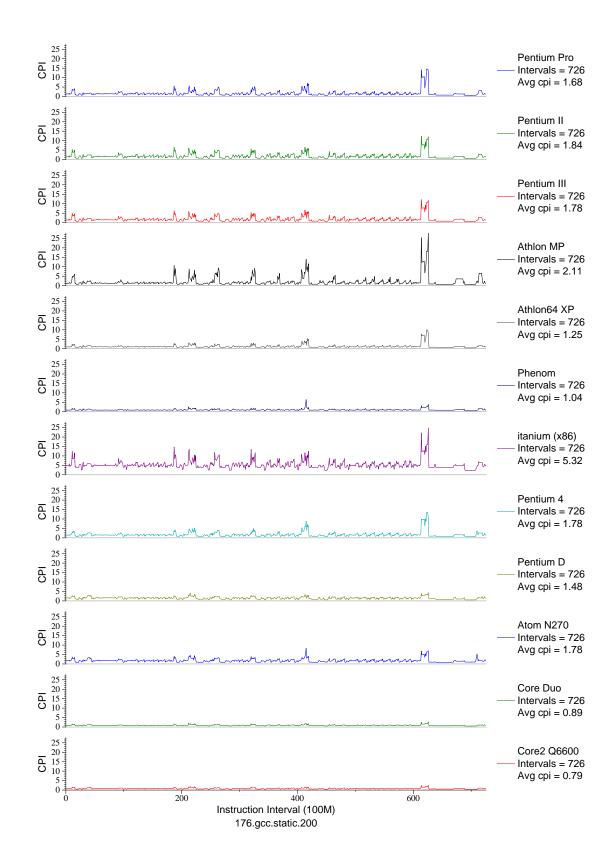

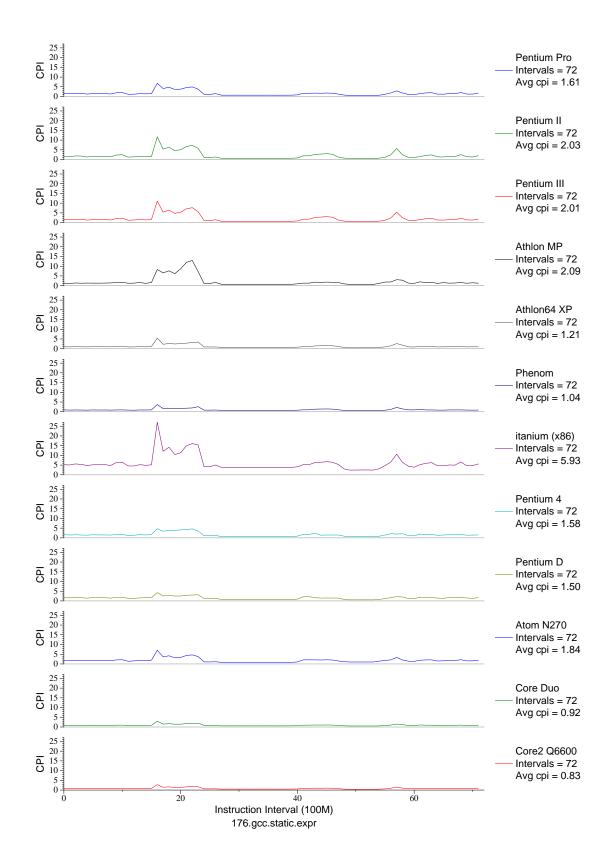

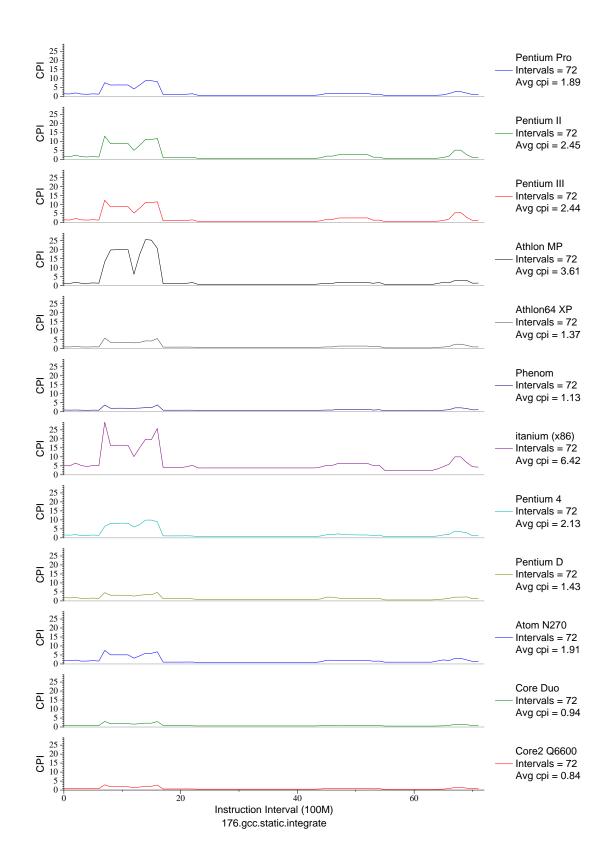

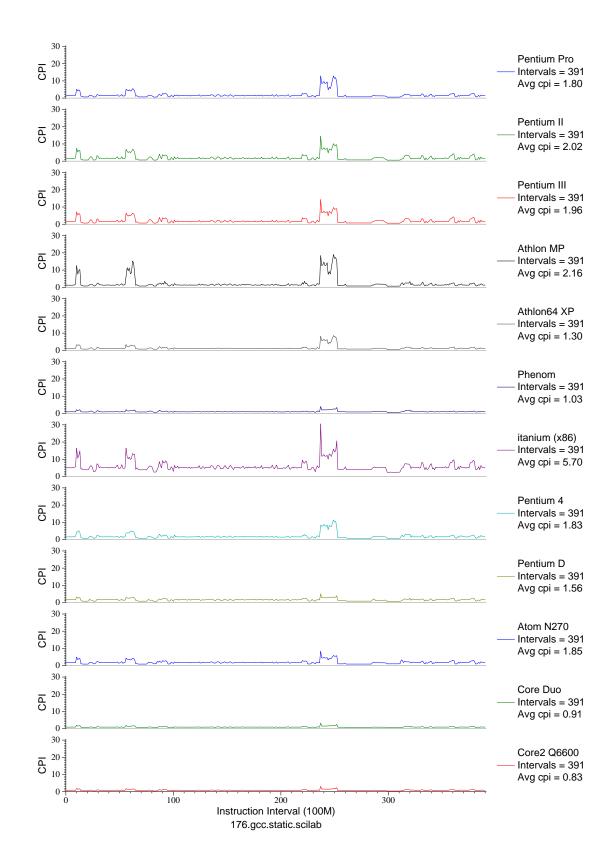

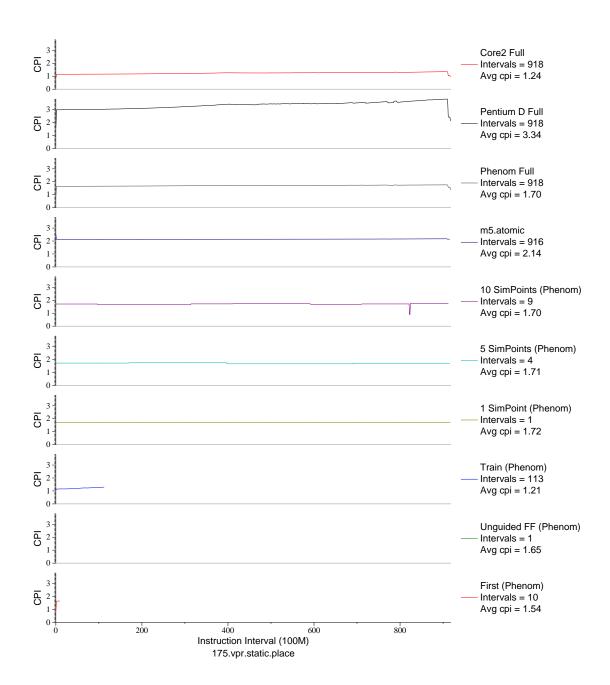

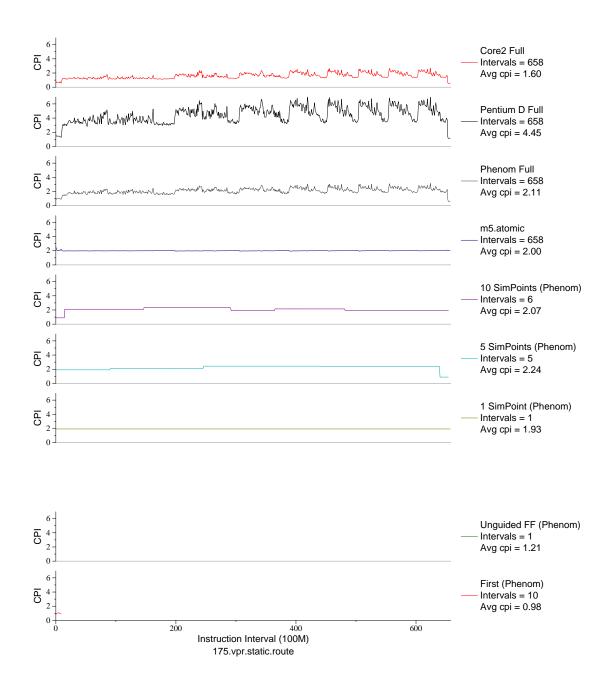

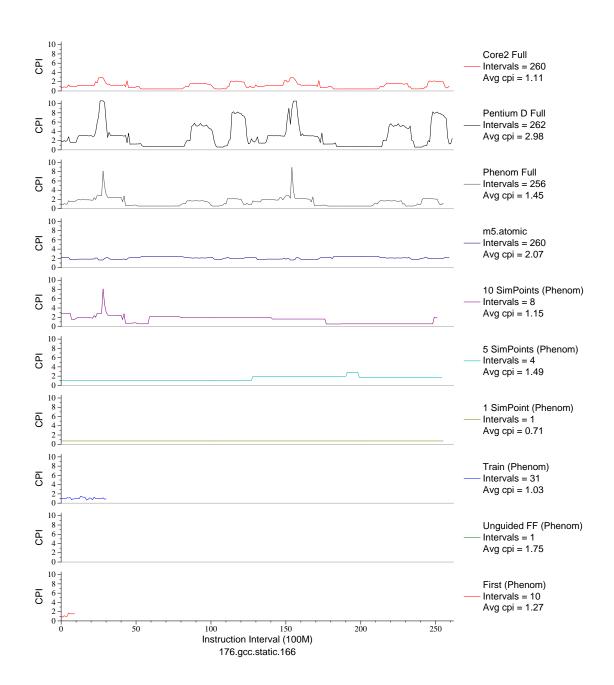

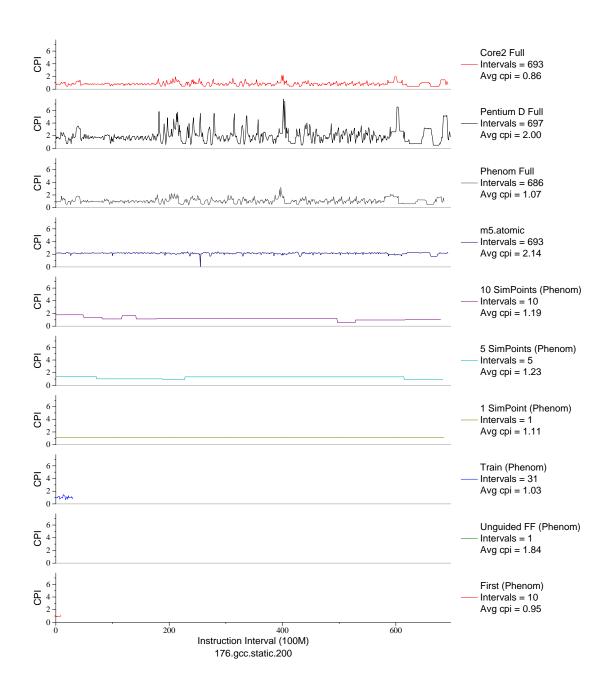

| Е | CPI Phase Plots         E.1 32-bit x86                                                                                                                                                                                              | 164<br>164<br>213               |

| F | Multi-architecture Phase Plots                                                                                                                                                                                                      | 254                             |

| G | L1 Data Cache Accesses per Instruction Phase Plots                                                                                                                                                                                  | 279                             |

| Н | L1 Data Cache Accesses per $\mu$ op Phase Plots                                                                                                                                                                                     | 320                             |

| I  | Valgrind exp-bbv Tool Code Listing    | 341 |

|----|---------------------------------------|-----|

| J  | Qemu BBV Patch Code Listing           | 353 |

| K  | R12000 Branch Predictor Kernel Module | 363 |

| L  | SESC R12000 Configuration File        | 364 |

| Bi | Bibliography                          |     |

## LIST OF TABLES

| 3.1<br>3.2               | Machines used for x86 SimPoint evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29<br>36       |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4.1<br>4.2               | Machines used for this study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48             |

| 12                       | other implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50             |

| 4.3                      | Potential overcounted dynamic instructions due to the rep prefix (only benchmarks with more than 10 billion are shown)                                                                                                                                                                                                                                                                                                                                                                                              | 62             |

| 5.1<br>5.2<br>5.3        | Configuration of SGI Octane2 machine used for comparison Comparison of simulation times                                                                                                                                                                                                                                                                                                                                                                                                                             | 69<br>73       |

| 5.4                      | only a portion of the 48 available benchmark/input combinations). Summary of relative results. The relative results compare the relative results when moving from 2-bit branch predictor to either taken or static. The error shown is the relative error between the relative average means of all benchmarks on actual hardware versus the predicted relative average means of the simulated results. The results represent the 33 of the SPEC CPU 2000 benchmarks which ran to completion on all three platforms | 83             |

| 6.1<br>6.2<br>6.3<br>6.4 | Hardware performance counters used for $\mu$ op experiments Number of uops required for an assortment of x86 instructions . Configuration of AMD Phenom machine used for comparison . Hardware performance counters used for our experiments. We did not use all of the counters listed. Some of the counters have known errata. We gathered this list from PAPI [102] and the AMD and Intel reference manuals [10, 72]                                                                                             | 87<br>89<br>91 |

| A.1<br>A.2               | Summary of investigated architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 125<br>129     |

| B.1<br>B.2               | L1 Cache latencies on Fusion group machines                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| C.1<br>C.2               | Retired instructions for Alpha SPEC CPU2000, showing Qemu and m5 results                                                                                                                                                                                                                                                                                                                                                                                                                                            | 143            |

| C.2                      | Qemu and actual hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 144            |

| C.3  | Retired instructions for PPC SPEC CPU 2000, showing Qemu              |     |

|------|-----------------------------------------------------------------------|-----|

|      | and Valgrind results                                                  | 145 |

| C.4  | Retired instructions for SPARC SPEC CPU2000, showing actual           |     |

|      | hardware and Qemu results                                             | 146 |

| C.5  | Retired instructions for SPARC SPEC CPU2006, showing actual           |     |

|      | hardware and Qemu results (part 1)                                    | 147 |

| C.6  | Retired instructions for SPARC SPEC CPU2006, showing actual           |     |

|      | hardware and Qemu results (part 2)                                    | 148 |

| C.7  | Retired instructions for x86 SPEC CPU2000, showing both Qemu          |     |

|      | and actual hardware                                                   | 149 |

| C.8  | Retired instructions for x86 SPEC CPU2006, showing Pin, Val-          |     |

|      | grind, and Qemu and Pentium D (part 1)                                | 150 |

| C.9  | Retired instructions for x86 SPEC CPU2006, showing Pin, Val-          |     |

|      | grind, and Qemu and Pentium D (part 2)                                | 151 |

| C.10 | Retired instructions for x86_64 SPEC CPU2000, showing both            |     |

|      | Qemu and actual hardware                                              | 152 |

| D.1  | Summary of slowdown compared to Pentium D node running                |     |

|      | x86_64 binaries.                                                      | 155 |

| D.2  | x86 32-bit versus 64-bit run time anomaly for sixtrack. Some          |     |

|      | benchmarks perform markedly worse when compiled as 64-bit             | 156 |

| D.3  | Elapsed times for running the SPEC CPU 2000 benchmarks on             |     |

|      | various Alpha simulators. <i>domori</i> is time on our reference Pen- |     |

|      | tium D machine. <i>bmul</i> is an actual Alpha 21264 system           | 157 |

| D.4  | Elapsed times for running the SPEC CPU 2000 benchmarks on             |     |

|      | various MIPS simulators. domori is time on our reference Pen-         |     |

|      | tium D machine. hershey is an actual MIPS R12000 system. The          |     |

|      | pre-compiled SPEC benchmarks from the SESC site are used;             |     |

|      | some (such as gzip) are modified to have shorter run-times,           |     |

|      | which is why the R12000 runs them faster than the Pentium D           | 158 |

| D.5  | Elapsed times for running the SPEC CPU 2000 benchmarks on             |     |

|      | various SPARC simulators. domori is time on our reference Pen-        |     |

|      | tium D machine. <i>niagara</i> is an actual SPARC niagara system      | 159 |

| D.6  | Times for x86 architecture                                            | 160 |

| D.7  | Times for x86_64 architecture comparing simulators                    | 161 |

| D.8  | Times for x86_64 DBI                                                  | 162 |

| D.9  | Times for x86_64 DBI utilities running cache simulations              | 163 |

## LIST OF FIGURES

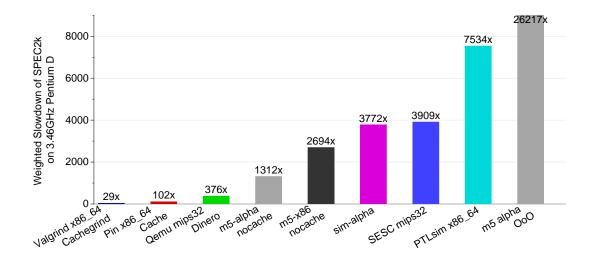

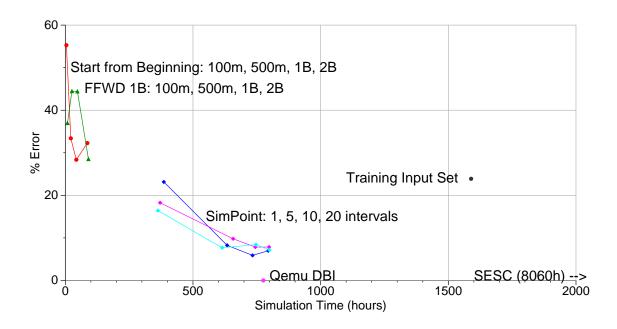

| 1.1  | Weighted slowdowns of various simulators when running SPEC CPU2000                                                                                                                       | 2   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

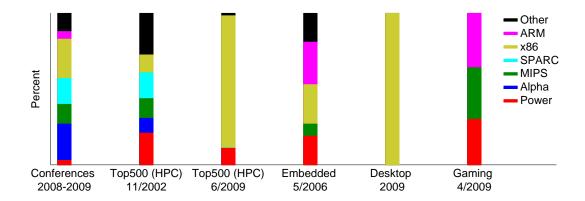

| 1.2  | Instruction set diversity across various domains. Recent computer architecture conference papers (ICCD'09, ISCA'09, MI-                                                                  |     |

|      | CRO'08 and ASPLOS'09) match years-old high-performance computing diversity rather than modern trends in computing                                                                        | 3   |

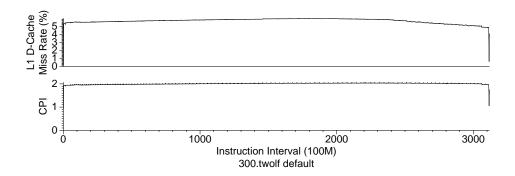

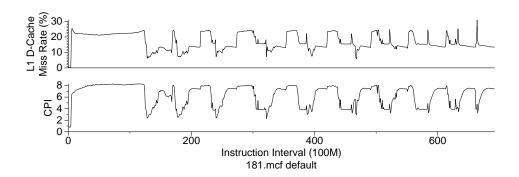

| 3.1  | L1 Data Cache and CPI behavior for twolf: behavior is uniform, with one phase representing the entire program                                                                            | 25  |

| 3.2  | L1 Data Cache and CPI behavior for mcf: several recurring phases are evident                                                                                                             | 25  |

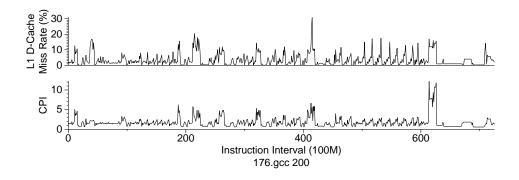

| 3.3  | L1 Data Cache and CPI behavior for gcc. 200: this program exhibits complex behavior that is hard to capture with phase de-                                                               | 0.5 |

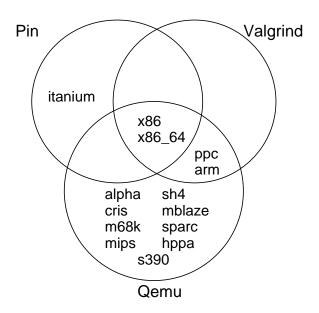

| 3.4  | Architectures supported by Pin, Qemu, and Valgrind: x86 is the ideal platform for comparison, as it is well supported by all three                                                       | 25  |

| 3.5  | of the tools                                                                                                                                                                             | 28  |

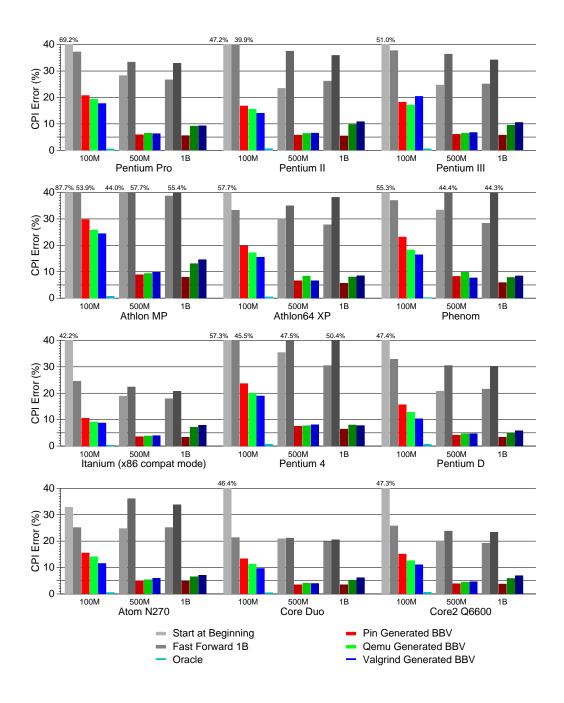

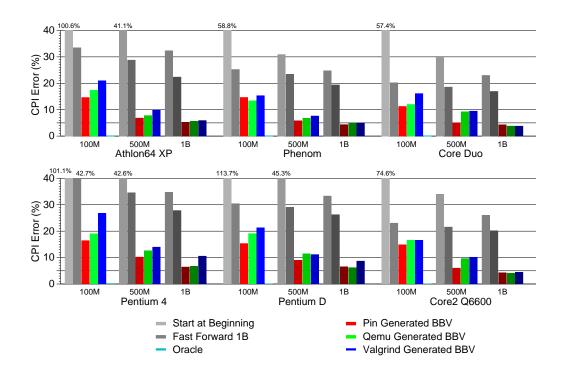

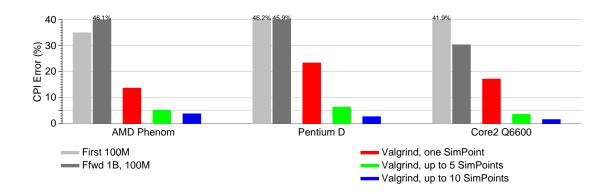

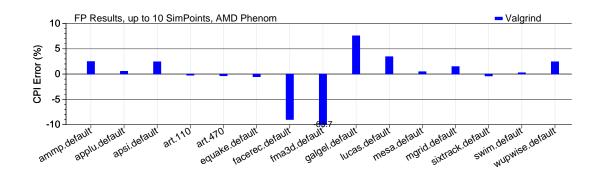

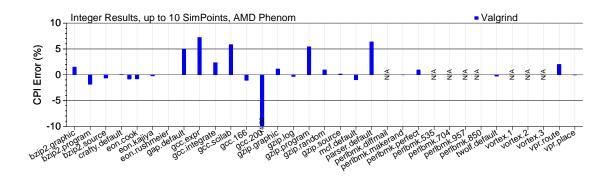

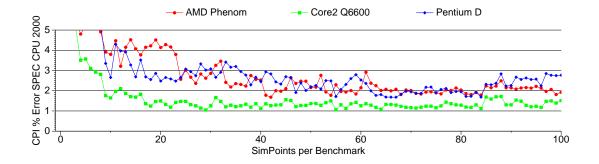

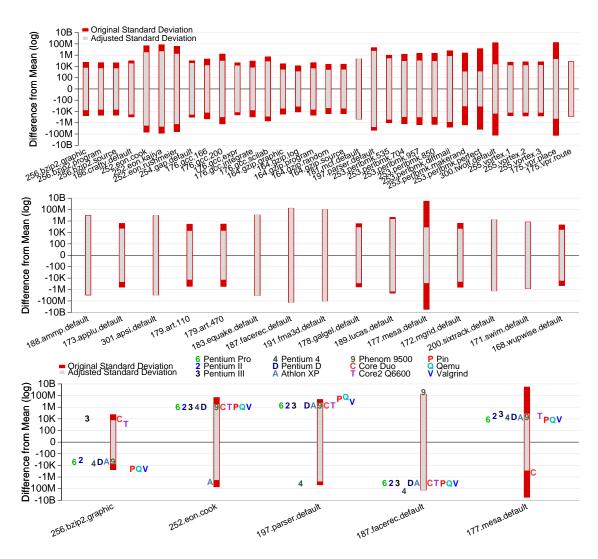

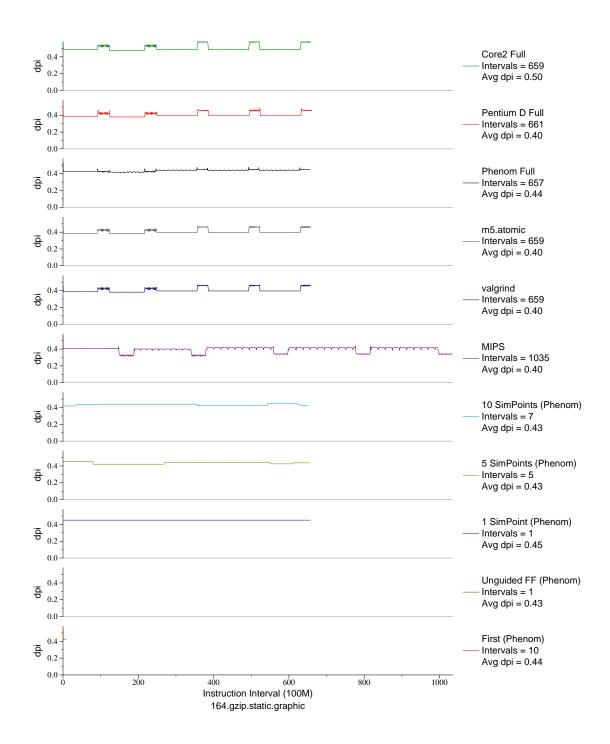

|      | guided fast-forward, and SimPoint selected intervals on various x86 machines.                                                                                                            | 30  |

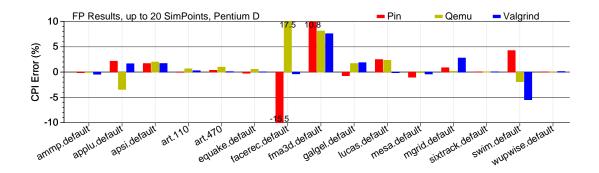

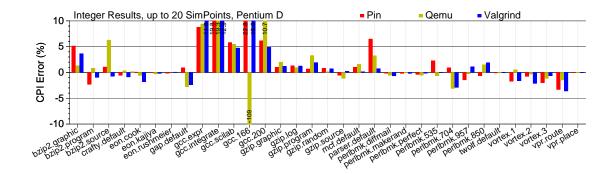

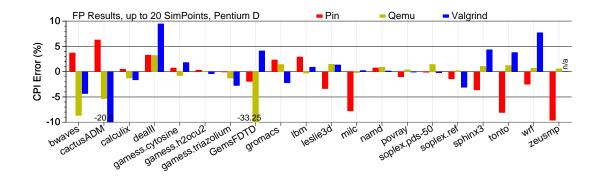

| 3.6  | Percent error in CPI on a Pentium D when using up to 20 Sim-Points on CPU2000 FP: the error with facerec and fma3d is due to extreme swings in the phase behavior that SimPoint has      |     |

| 3.7  | Percent error in CPI on a Pentium D when using up to 20 Sim-Points on CPU2000 INT: the large error with the gcc benchmarks is due to spikes in the phase behavior that SimPoint does not | 31  |

| 3.8  | capture well                                                                                                                                                                             | 31  |

| 3.9  | intervals                                                                                                                                                                                | 34  |

| 3.10 | in the way the tools count instructions                                                                                                                                                  | 35  |

| 3.11 | by SimPoint                                                                                                                                                                              | 35  |

|      | using first, unguided fast-forward, and SimPoint selected intervals                                                                                                                      | 37  |

| 3.12 | x86_64 CPI Error for SPEC CPU2000 floating point benchmarks.                                                                | 38 |

|------|-----------------------------------------------------------------------------------------------------------------------------|----|

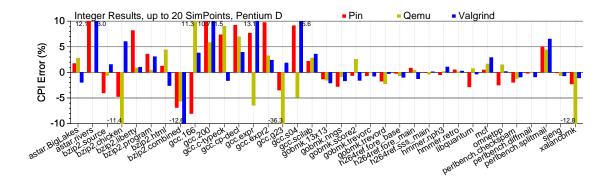

| 3.13 | x86_64 CPI Error for SPEC CPU2000 integer benchmarks                                                                        | 38 |

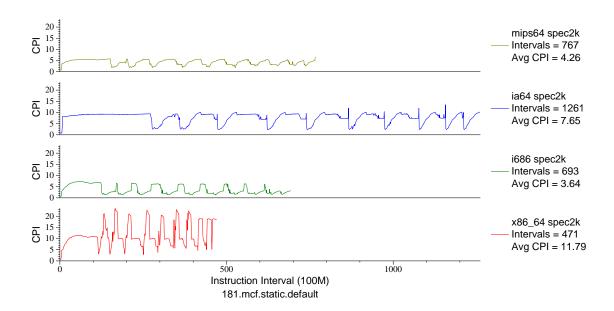

| 3.14 | Phase plot for mcf across various architectures. While the phases                                                           |    |

|      | look similar, the interval numbers are not                                                                                  | 39 |

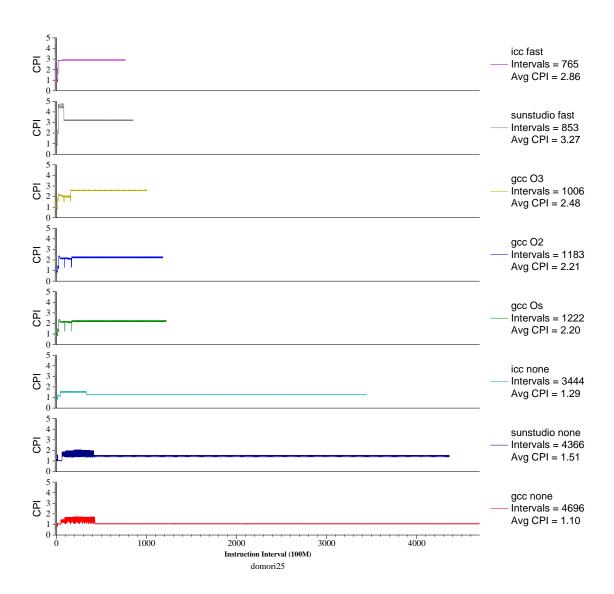

| 3.15 | Phase plot for equake across various compilers are compile op-                                                              |    |

|      | tions. The interval numbers vary widely                                                                                     | 40 |

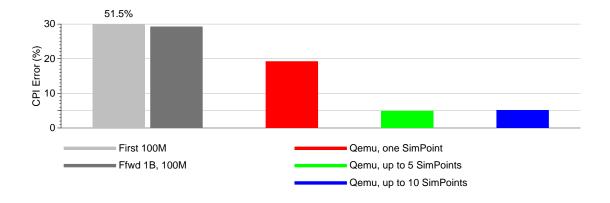

| 3.16 | MIPS R12000 SimPoint results for SPEC CPU2000. The BBVs for                                                                 |    |

|      | the SimPoints were generated cross-platform on an x86 machine                                                               |    |

|      | using Qemu                                                                                                                  | 41 |

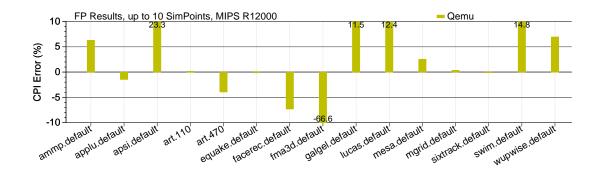

| 3.17 | MIPS CPI Error for SPEC CPU2000 floating point                                                                              | 42 |

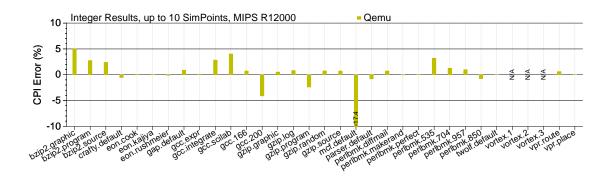

| 3.18 | MIPS CPI Error for SPEC CPU2000 integer benchmarks                                                                          | 42 |

| 3.19 | Percent average CPI error for SPEC CPU2000 as more SimPoints                                                                |    |

|      | are added per benchmark. After 20 SimPoints the average does                                                                |    |

|      | not decrease, even up to 100 points per benchmark (this is equiv-                                                           | 11 |

|      | alent to running 2% of all of the benchmarks)                                                                               | 44 |

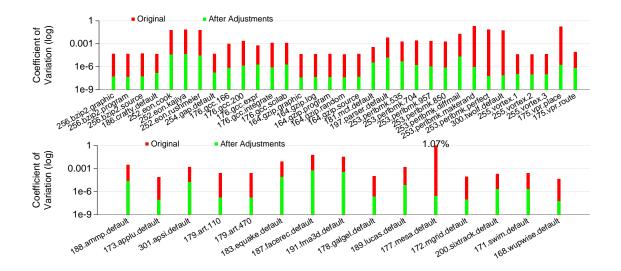

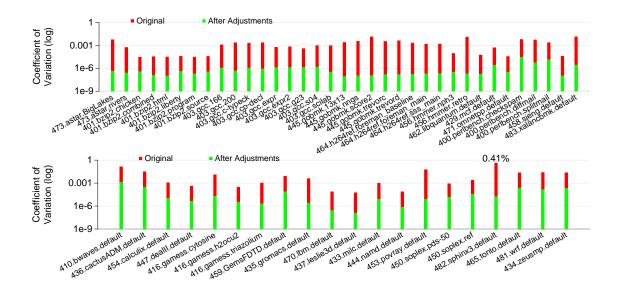

| 4.1  | SPEC 2000 Coefficient of variation. The top graph shows integer                                                             |    |

|      | benchmarks, the bottom, floating point. The error variation from                                                            |    |

|      | mesa, perlbmk, vpr, twolf and eon are primarily due to the                                                                  |    |

|      | fldcw miscount on the Pentium 4 systems. Variation after our                                                                |    |

|      | adjustments becomes negligible                                                                                              | 51 |

| 4.2  | SPEC 2006 Coefficient of variation. The top graph shows inte-                                                               |    |

|      | ger benchmarks, bottom, floating point. The original variation                                                              |    |

|      | is small compared to the large numbers of instructions in these                                                             |    |

|      | benchmarks. The largest variation is in sphinx3, due to fldcw                                                               |    |

|      | instruction issues. Variation after our adjustments becomes or-                                                             |    |

|      | ders of magnitude smaller                                                                                                   | 52 |

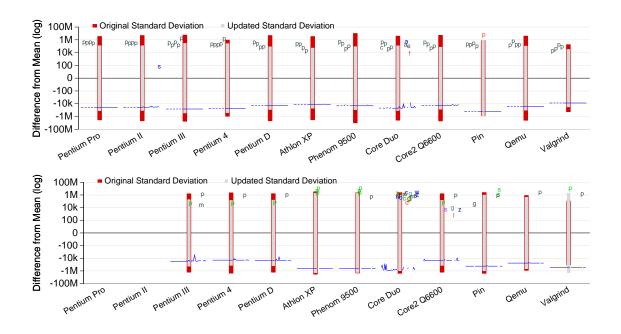

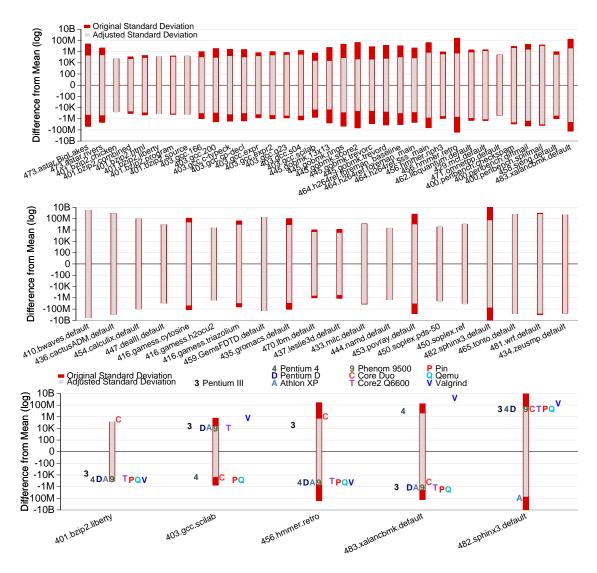

| 4.3  | Intra-machine results for SPEC CPU2000 (above) and CPU2006                                                                  |    |

|      | (below). Outliers are indicated by the first letter of the bench-                                                           |    |

|      | mark name and a distinctive color. For CPU2000, the perlbmk                                                                 |    |

|      | benchmarks (represented by gray 'p's) are a large source of vari-                                                           |    |

|      | ation. For CPU2006, the perlbench (green 'p') and povray                                                                    |    |

|      | (gray 'p') are the common outliers. Order of plotted letters for                                                            |    |

|      | outliers has no intrinsic meaning, but tries to make the graphs                                                             |    |

|      | as readable as possible. Horizontal lines summarize results                                                                 |    |

|      | for remaining benchmarks (they're all similar). The message                                                                 |    |

|      | here is that most platforms have few outliers, and there's much consistency with respect to measurements across benchmarks; |    |

|      | Core Duo and Core2 Q6600 have many more outliers, especially                                                                |    |

|      | for CPU2006. Our technical report provides detailed perfor-                                                                 |    |

|      | mance information — these plots are merely intended to indi-                                                                |    |

|      | cate trends. Standard deviations decrease drastically with our                                                              |    |

|      | updated methods, but there is still room for improvement                                                                    | 54 |

|      |                                                                                                                             | -  |

| 4.4        | Inter-machine results for SPEC CPU2000. We choose five representative benchmarks and show the individual machine differences contributing to the standard deviations. Often there is a single outlier affecting results; the outlying machine is often different. DBI results are shown, but not incorporated into standard                 |     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | deviations.                                                                                                                                                                                                                                                                                                                                 | 55  |

| 4.5        | Inter-machine results for SPEC CPU2006. We choose five representative benchmarks and show the individual machine differences contributing to the standard deviations. Often there is a single outlier affecting results; the outlying machine is often different. DBI results are shown, but not incorporated into the standard deviations. | 56  |

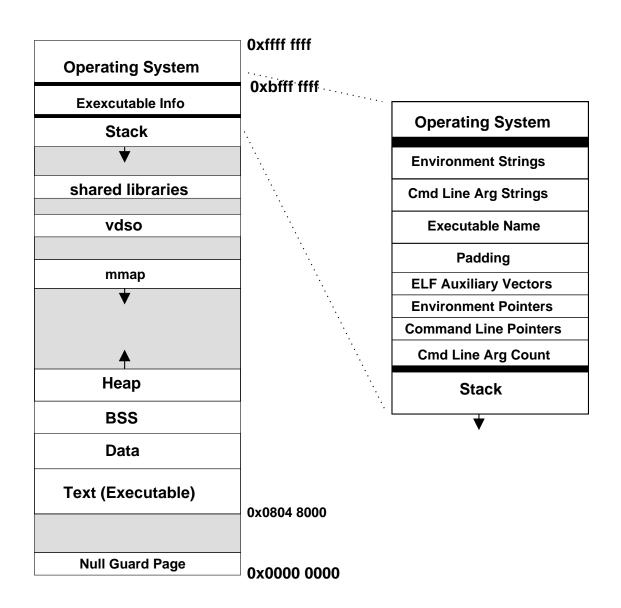

| 4.6        | The typical layout of virtual memory for a process on 32-bit x86                                                                                                                                                                                                                                                                            |     |

| 1.0        | Linux. If process space randomization is enabled, then the BSS,                                                                                                                                                                                                                                                                             |     |

|            | Heap, mmap and stack can have different offsets                                                                                                                                                                                                                                                                                             | 58  |

| <b>-</b> 1 |                                                                                                                                                                                                                                                                                                                                             |     |

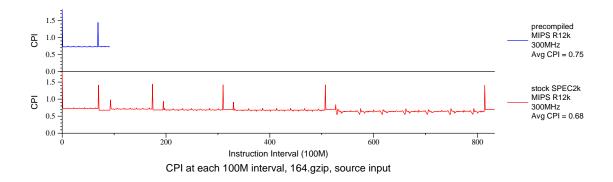

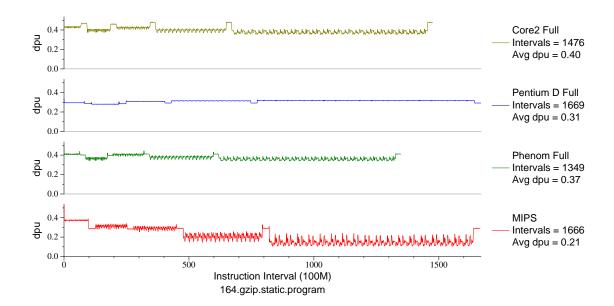

| 5.1        | The precompiled SPEC 2000 benchmarks available from the SESC website have potentially been modified to reduce runtime. A phase chart gathered with hardware performance counters shows behavior of the provided precompiled binary on top and that of a binary was compiled from original SPEC sources (with                                |     |

|            | that of a binary we compiled from original SPEC sources (with gcc) on bottom                                                                                                                                                                                                                                                                | 72  |

| 5.2        | 0 ,                                                                                                                                                                                                                                                                                                                                         | 12  |

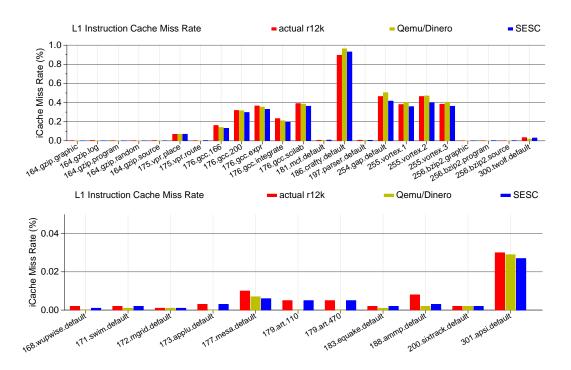

| 3.2        | Instruction cache miss rate with integer benchmarks above and floating point below                                                                                                                                                                                                                                                          | 74  |

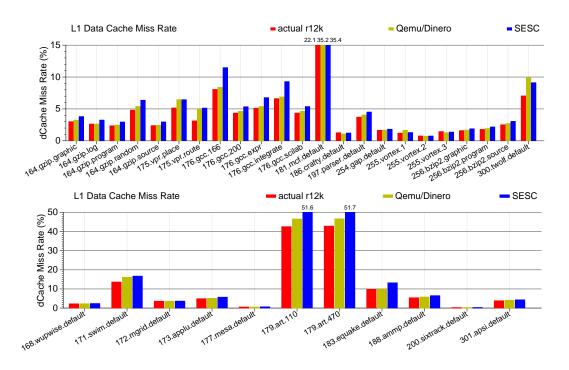

| 5.3        | L1 data cache miss rate with integer benchmarks above and                                                                                                                                                                                                                                                                                   | , . |

|            | floating point below.                                                                                                                                                                                                                                                                                                                       | 75  |

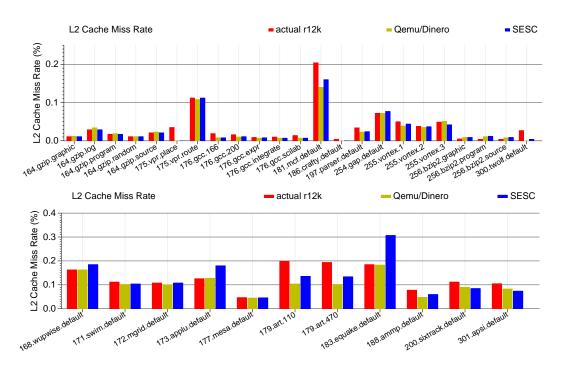

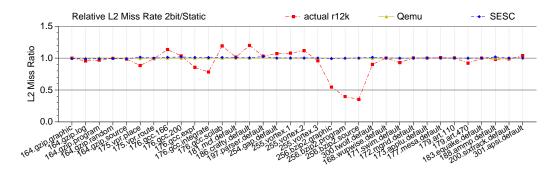

| 5.4        | L2 cache miss rate with integer above and floating point below. None of the simulations captures mcf's behavior well. None of                                                                                                                                                                                                               |     |

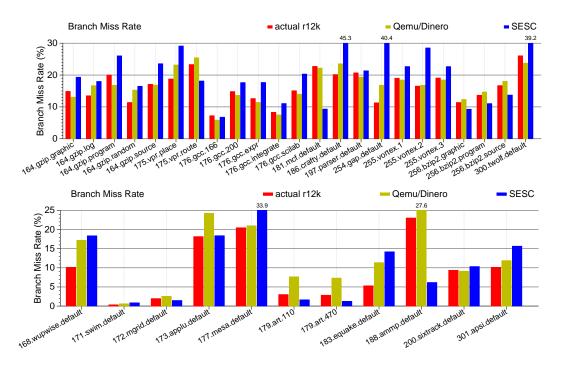

| 5.5        | the simulation methods predicts the art benchmarks well Branch miss rate with integer above and floating point below. The hardware can have up to four outstanding branches; Qemu                                                                                                                                                           | 76  |

|            | and SESC do not model wrong-path execution.                                                                                                                                                                                                                                                                                                 | 77  |

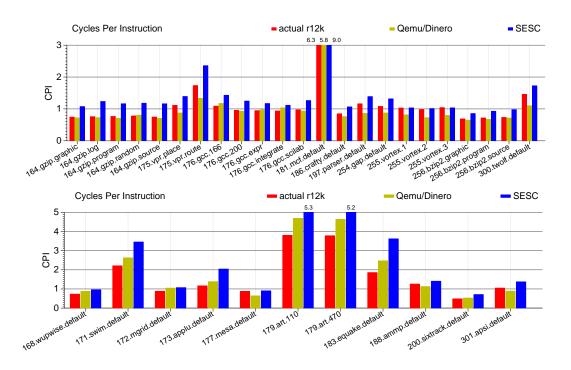

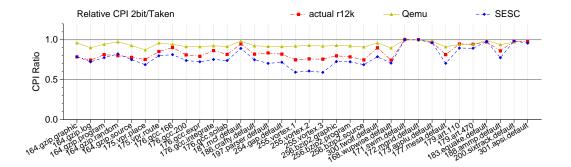

| 5.6        | CPI results with integer above and floating point below                                                                                                                                                                                                                                                                                     | 78  |

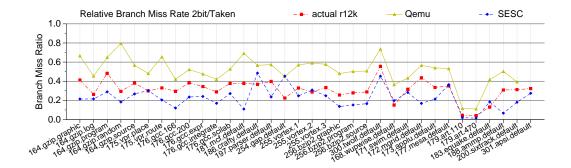

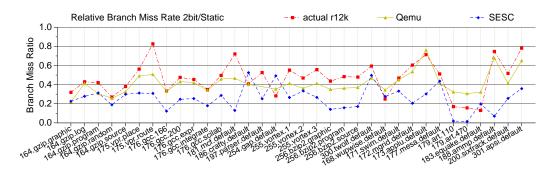

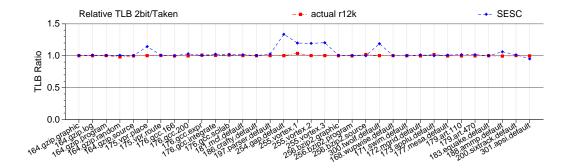

| 5.7        | Always taken branch predictor miss rate, normalized against dynamic two-bit results.                                                                                                                                                                                                                                                        | 70  |

| E 0        |                                                                                                                                                                                                                                                                                                                                             | 79  |

| 5.8        | Static branch predictor miss rate, normalized against dynamic two-bit results                                                                                                                                                                                                                                                               | 79  |

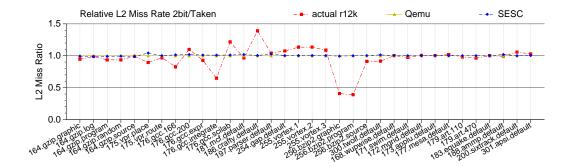

| 5.9        | L2 cache miss rates with the always-taken predictor, normalized                                                                                                                                                                                                                                                                             | 19  |

| J.)        | against two-bit results                                                                                                                                                                                                                                                                                                                     | 80  |

| 5.10       | L2 cache miss rates with the static predictor, normalized against                                                                                                                                                                                                                                                                           | 00  |

| J.10       | two-bit results.                                                                                                                                                                                                                                                                                                                            | 80  |

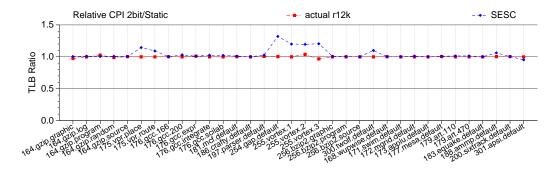

| 5.11       |                                                                                                                                                                                                                                                                                                                                             | 81  |

| 5.12       | •                                                                                                                                                                                                                                                                                                                                           | 81  |

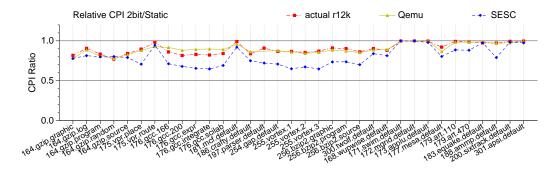

|            | CPI with always taken normalized against two-bit results                                                                                                                                                                                                                                                                                    | 82  |

| 5.14       | CPI with static predictor normalized against two-bit results                                                                                                                                      | 82  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

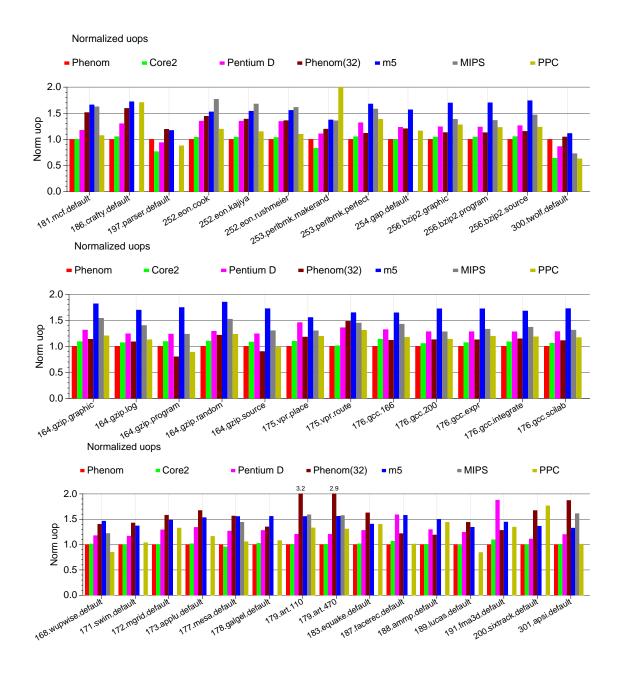

| 6.1<br>6.2 | Data cache accesses per $\mu$ op for gzip.program Normalized $\mu$ ops per benchmark for three x86_64 implementations, a 32-bit x86, the m5 simulator, and two representative RISC                | 87  |

| 6.3        | architectures                                                                                                                                                                                     | 88  |

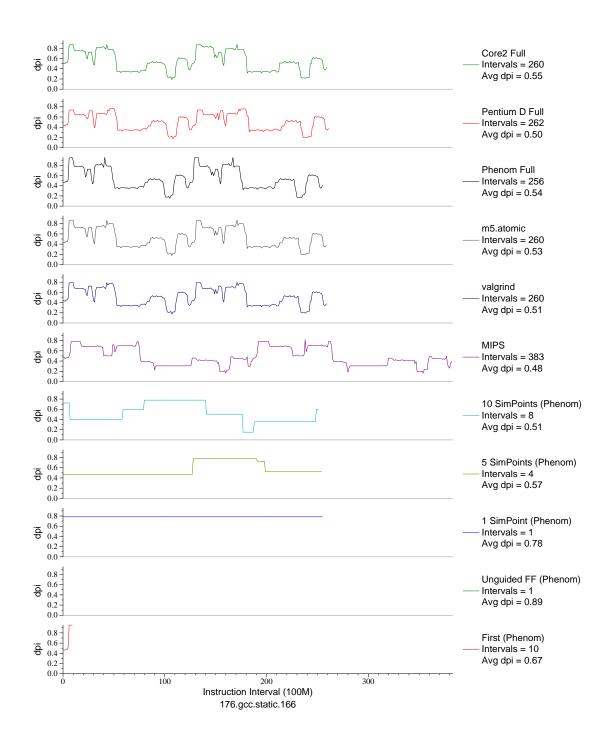

|            | cache accesses per instruction is consistent across all actual machines, as well as the simulators. The MIPS results are very different. SimPoint results are shown for comparison                | 96  |

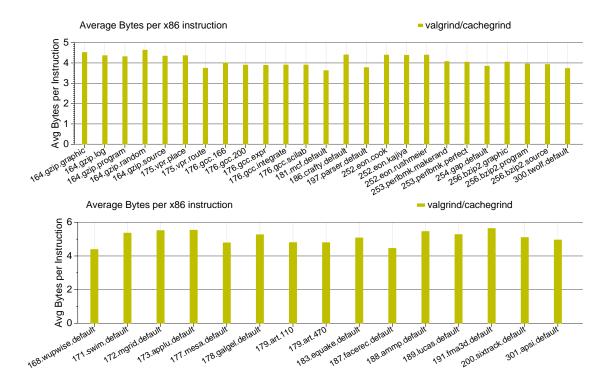

| 6.4        | Average bytes per x86 instruction. For integer benchmarks the average is 4.0, for floating point it is 5.1. These values are needed when extrapolating cache miss rates when given only total re- | 0.0 |

| <i>(</i>   | tired instruction count.                                                                                                                                                                          | 98  |

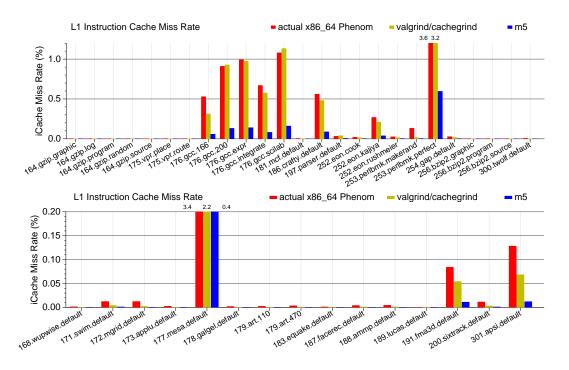

| 6.5        | Instruction cache miss rate with integer benchmarks above and floating point below                                                                                                                | 99  |

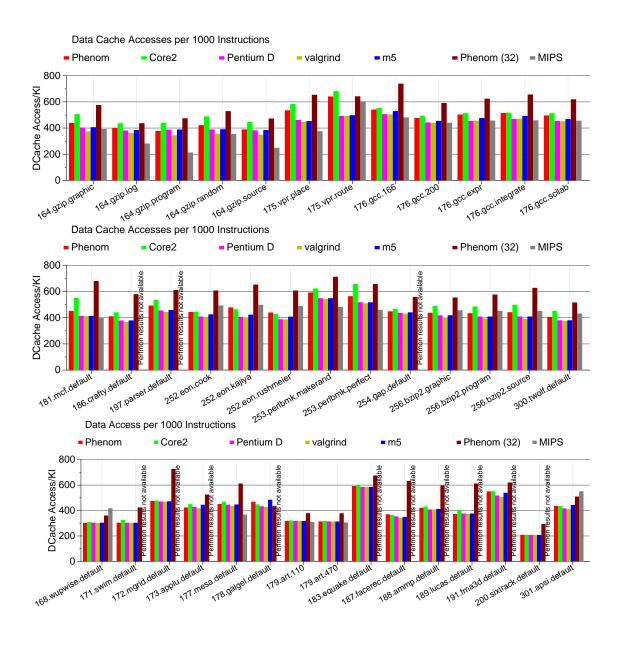

| 6.6        | Data Accesses per Thousand Instructions for the SPEC CPU2000                                                                                                                                      |     |

|            | benchmarks                                                                                                                                                                                        | 100 |

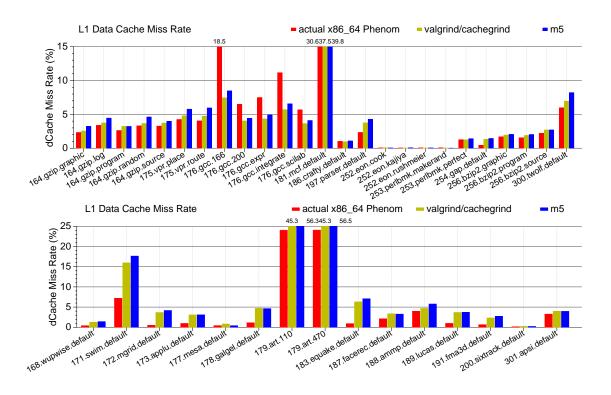

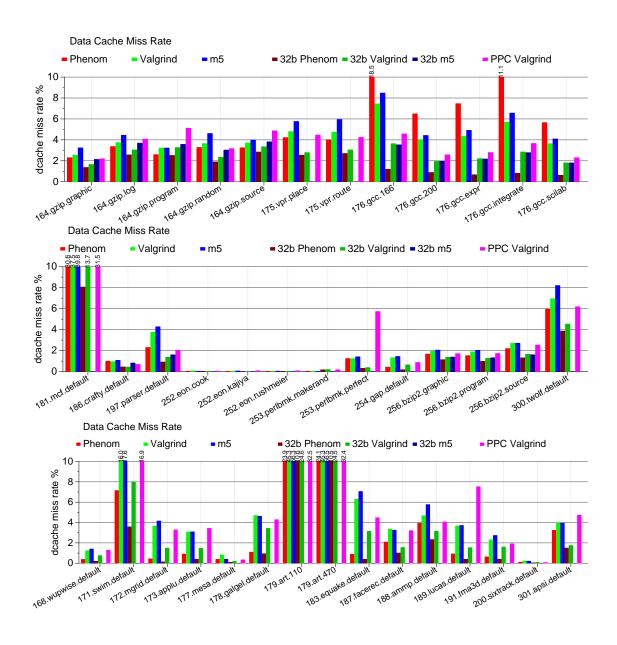

| 6.7        | L1 data cache miss rate with integer benchmarks above and                                                                                                                                         |     |

|            | floating point below.                                                                                                                                                                             | 101 |

| 6.8        | Deache miss rates for Phenom-style cache                                                                                                                                                          | 102 |

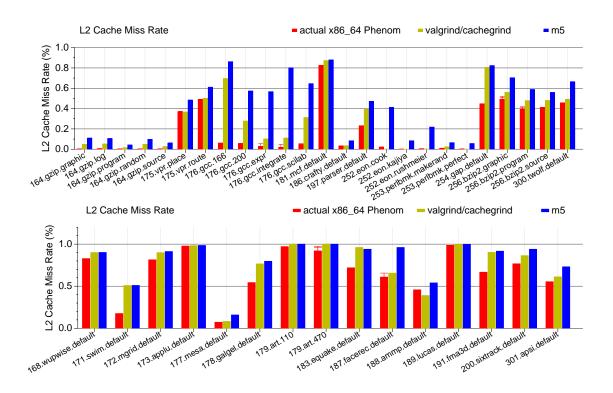

| 6.9        | L2 cache miss rates, actual and simulated. The simulators are                                                                                                                                     |     |

|            | pessimistic; in the case of gcc severely so                                                                                                                                                       | 103 |

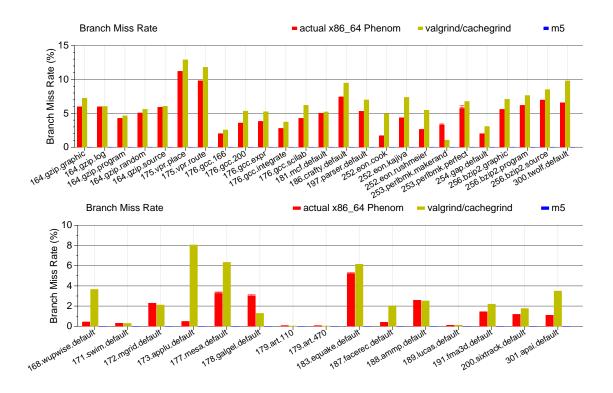

| 6.10       | Branch predictor results for Valgrind and actual hardware. m5                                                                                                                                     |     |

|            | currently cannot simulate branch prediction for x86_64                                                                                                                                            | 104 |

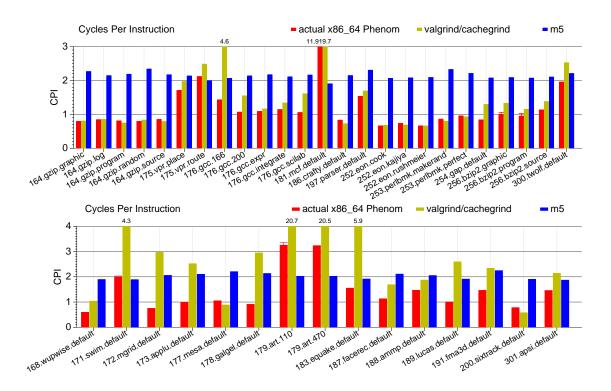

| 6.11       | CPI results with integer above and floating point below. Val-                                                                                                                                     |     |

|            | grind cycle times are estimated based on cache and branch pre-                                                                                                                                    |     |

|            | dictor behavior.                                                                                                                                                                                  | 105 |

| 6.12       | Relative instruction cache miss rate ratios when moving from 32-                                                                                                                                  | 401 |

|            | bit to 64-bit                                                                                                                                                                                     | 106 |

| 6.13       | Relative L1 data cache miss rate ratios when moving from 32-bit                                                                                                                                   | 107 |

| . 1 1      | to 64-bit                                                                                                                                                                                         | 107 |

| 6.14       | O                                                                                                                                                                                                 | 100 |

| ( 1 F      | to 64-bit                                                                                                                                                                                         | 108 |

| 6.15       |                                                                                                                                                                                                   | 100 |

| (1)        | bit to 64-bit                                                                                                                                                                                     | 108 |

| 6.16       | Relative CPI ratios when moving from 32-bit to 64-bit                                                                                                                                             | 109 |

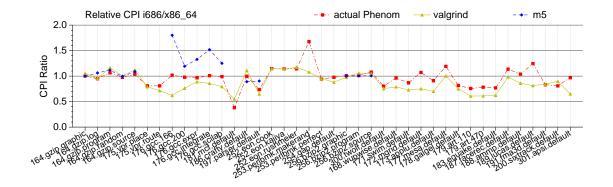

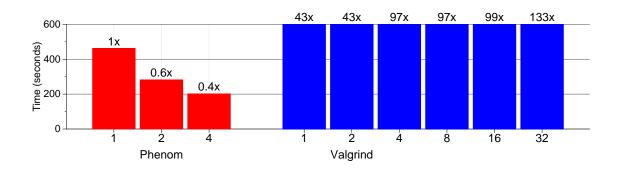

| 8.1        | equake_m run times for varying number of threads, both on ac-                                                                                                                                     |     |

|            | tual hardware and Valgrind                                                                                                                                                                        | 116 |

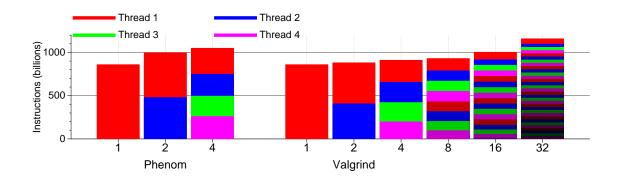

| 8.2        | equake_m retired instruction counts for varying number of                                                                                                                                         |     |

|            | threads, both on real hardware and Valgrind                                                                                                                                                       | 117 |

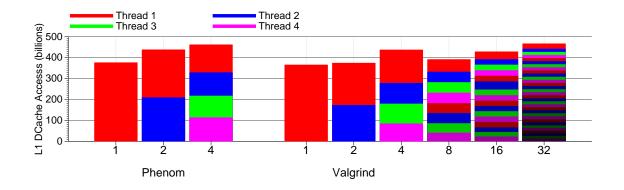

| 8.3        | equake_m L1 dcache access counts for varying number of                                                                                                                                            |     |

|            | threads, both on real hardware and Valgrind                                                                                                                                                       | 118 |

| 9.1          | on SPEC CPU2000, assuming perfect simulation                                                                                    | 21               |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|------------------|

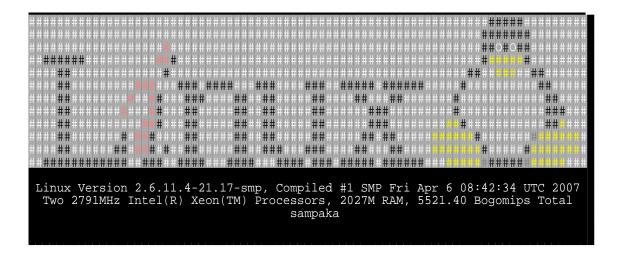

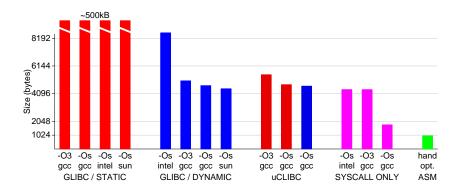

| A.1<br>A.2   | Sample output from the linux_logo benchmark                                                                                     | 24               |

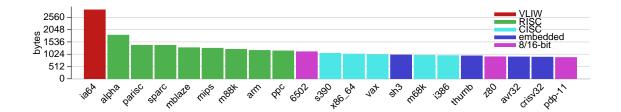

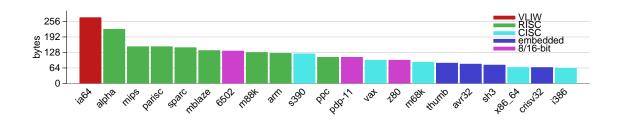

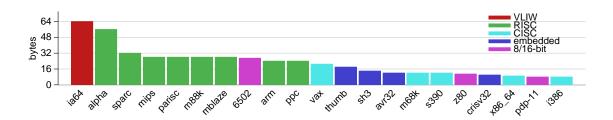

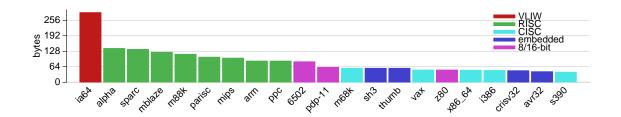

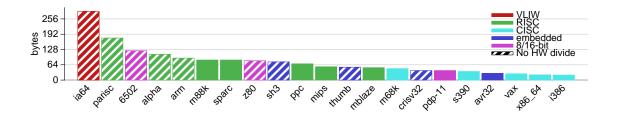

|              | so does not strictly reflect code density)                                                                                      | 30               |

| A.3          | 1                                                                                                                               | 30               |

| A.4          | Size of string concatenation code (machines with auto-increment                                                                 |                  |

|              | addressing modes and dedicated string instructions perform                                                                      | •                |

| ۸ ۵          | ,                                                                                                                               | 30               |

| A.5          | Size of string searching code (unaligned load instructions help, since four bytes at arbitrary offsets can be compared at once. |                  |

|              |                                                                                                                                 | 30               |

| A.6          | Size of integer printing code (hardware divide helps code density) 13                                                           |                  |

| A.7          | Total size of generated executables, stripped of debugging infor-                                                               |                  |

|              | 11 00 0                                                                                                                         | 34               |

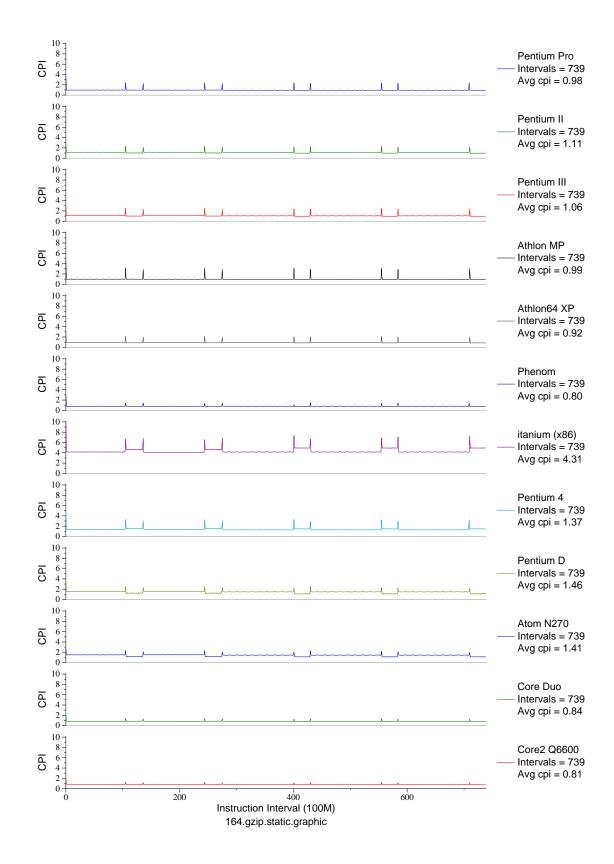

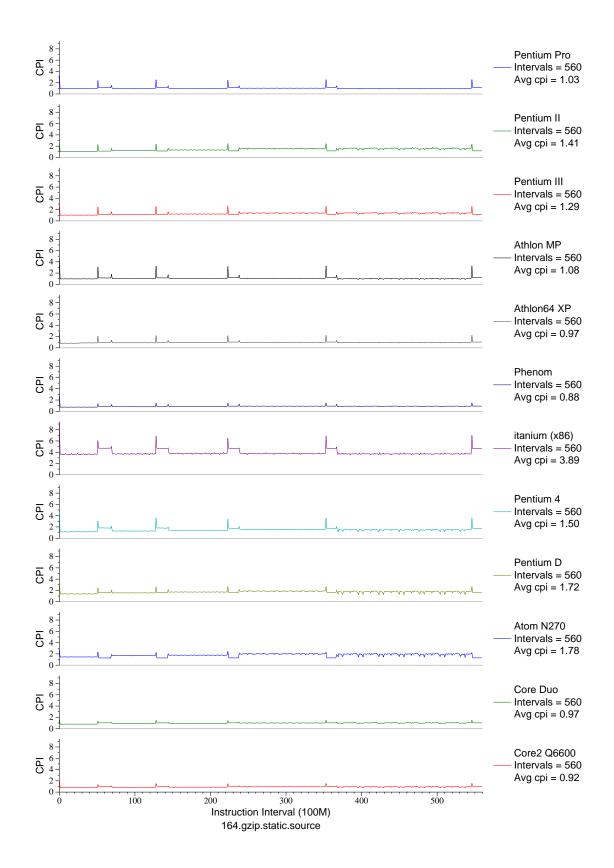

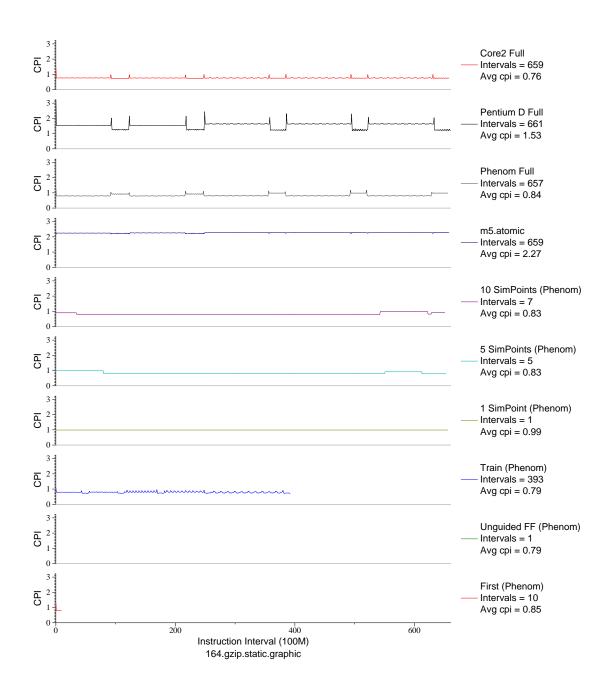

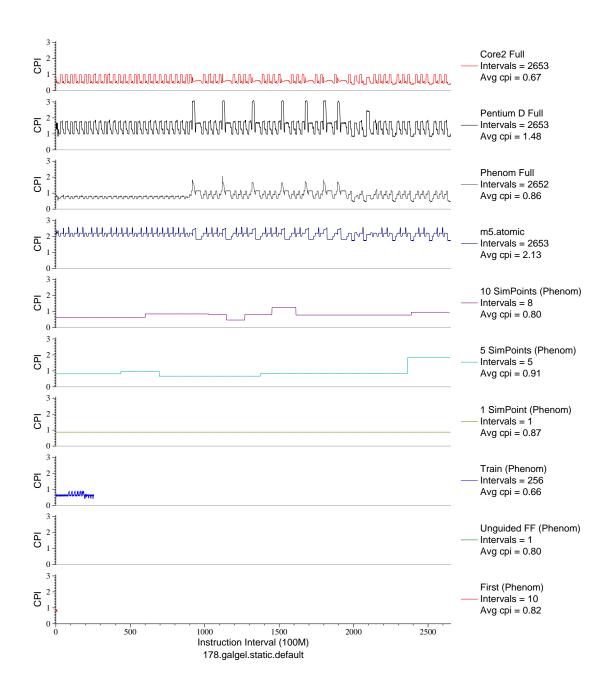

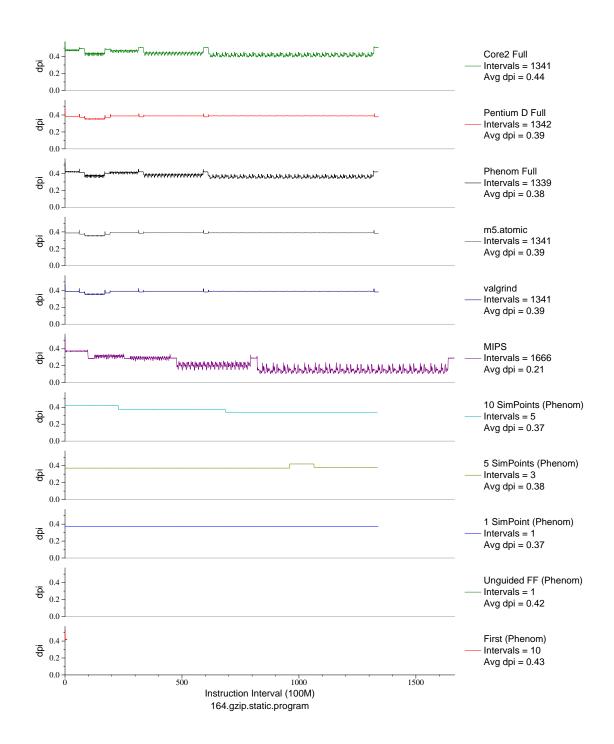

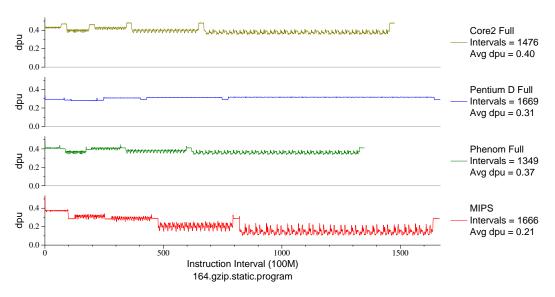

| E.1          | CPI phase plot for gzip.graph (INT, C, Compression) 10                                                                          | 65               |

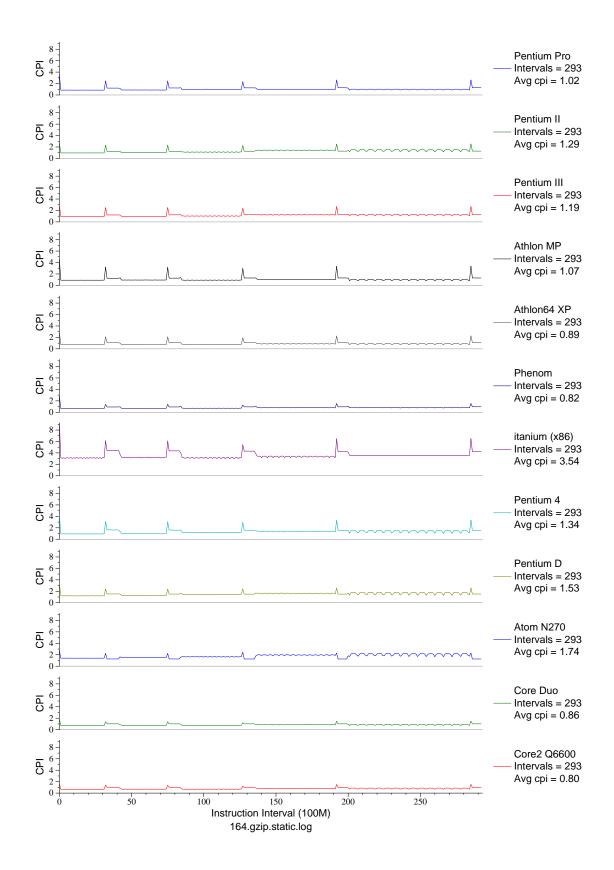

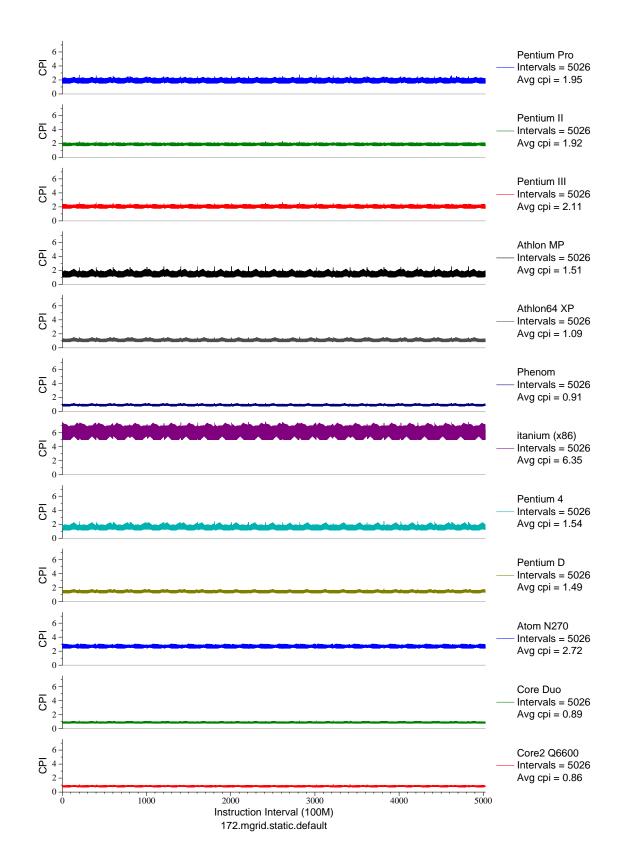

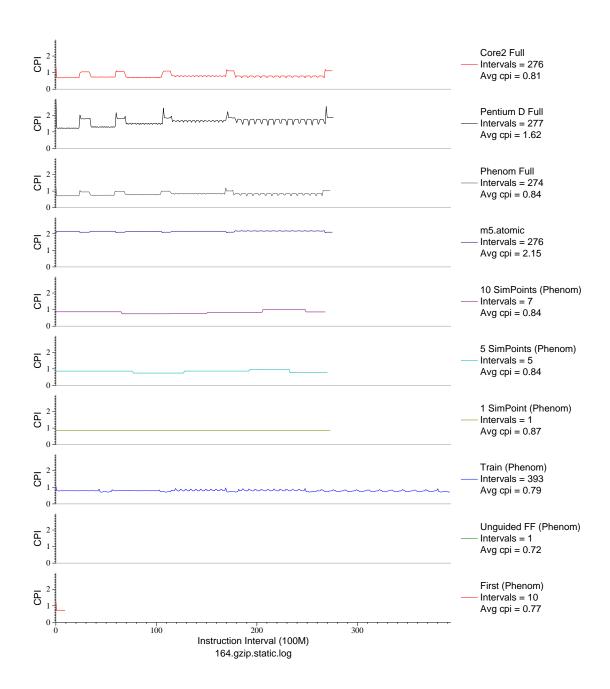

| E.2          |                                                                                                                                 | 66               |

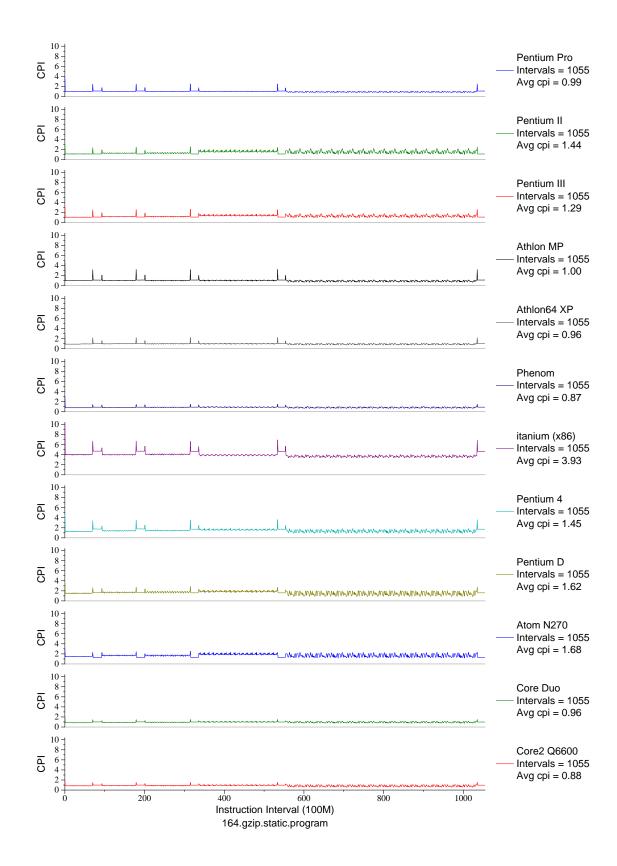

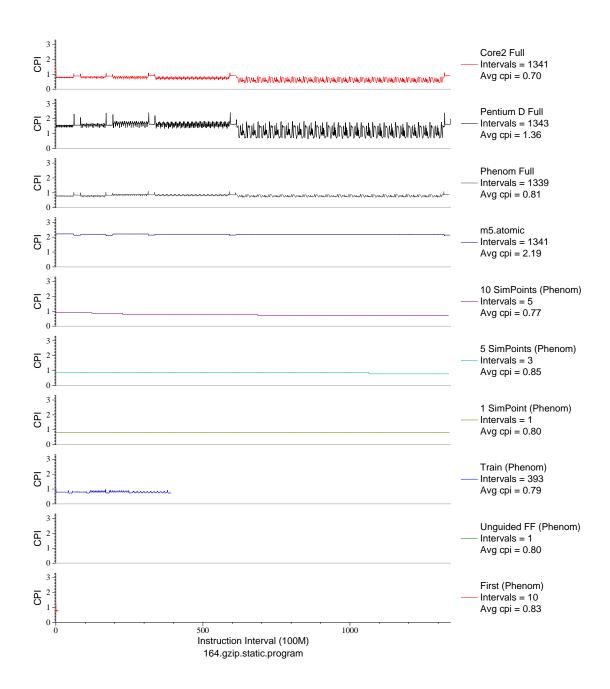

| E.3          |                                                                                                                                 | 67               |

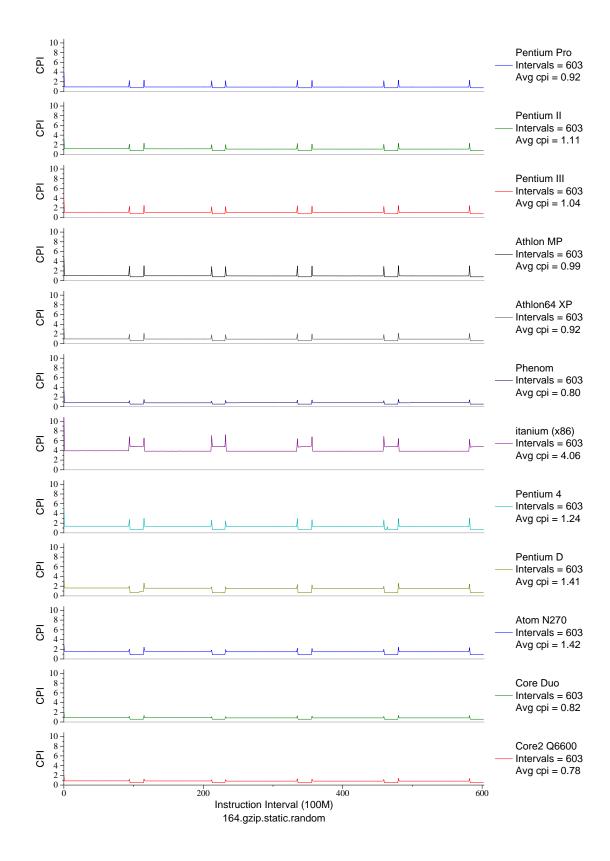

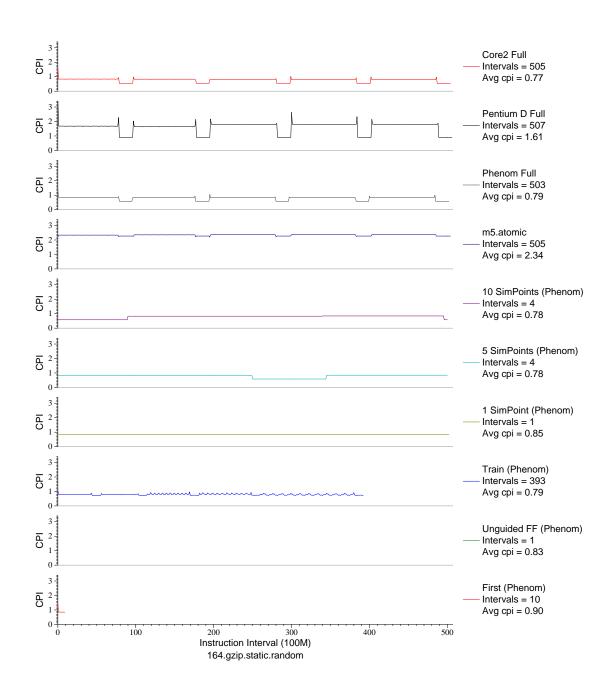

| E.4          | 1 1 ' ' ' 1 '                                                                                                                   | 68               |

| E.5          | <u> </u>                                                                                                                        | 69               |

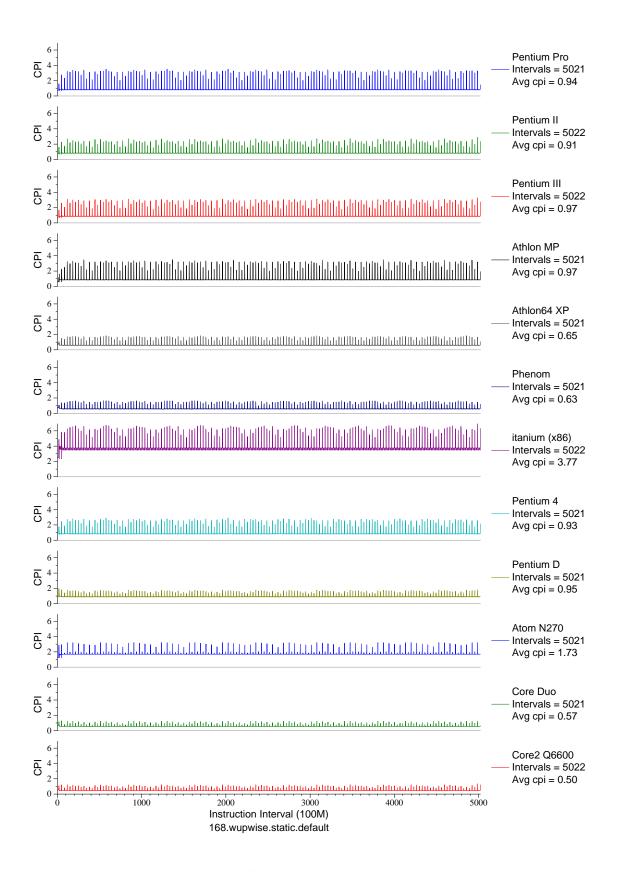

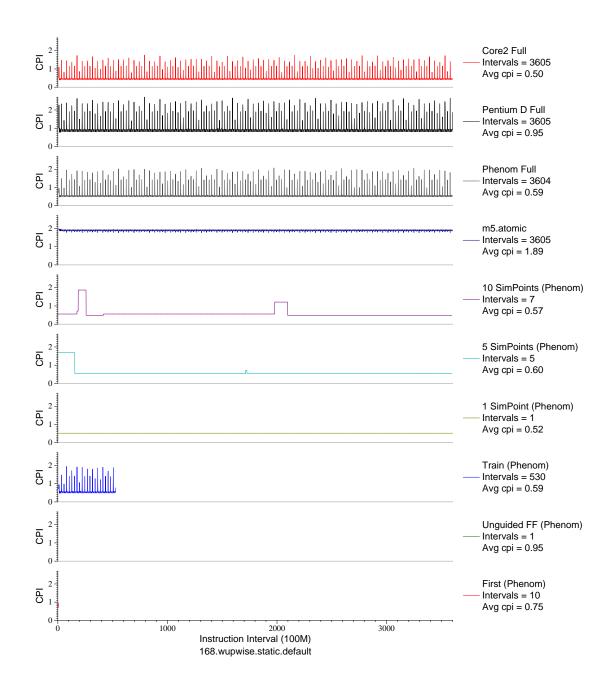

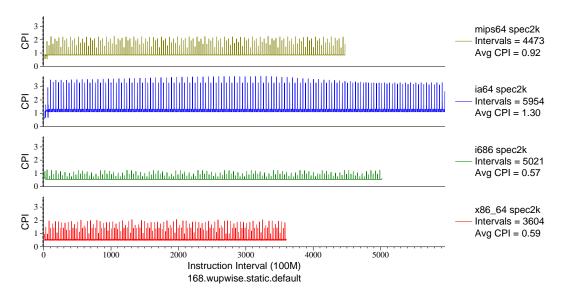

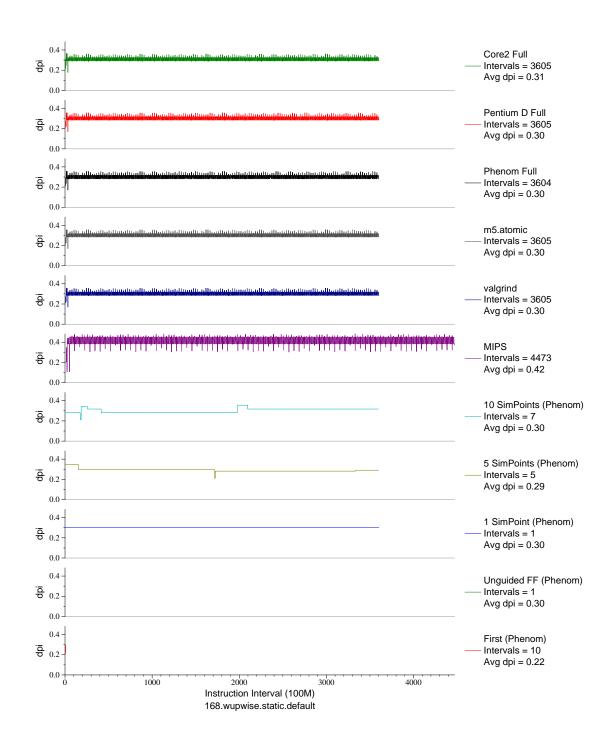

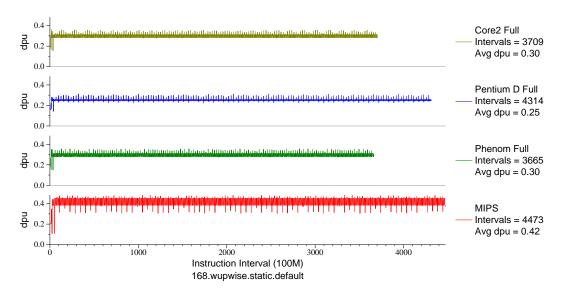

| E.6          | CPI phase plot for wupwise (FP, F77, Quantum Chromodynamics)17                                                                  |                  |

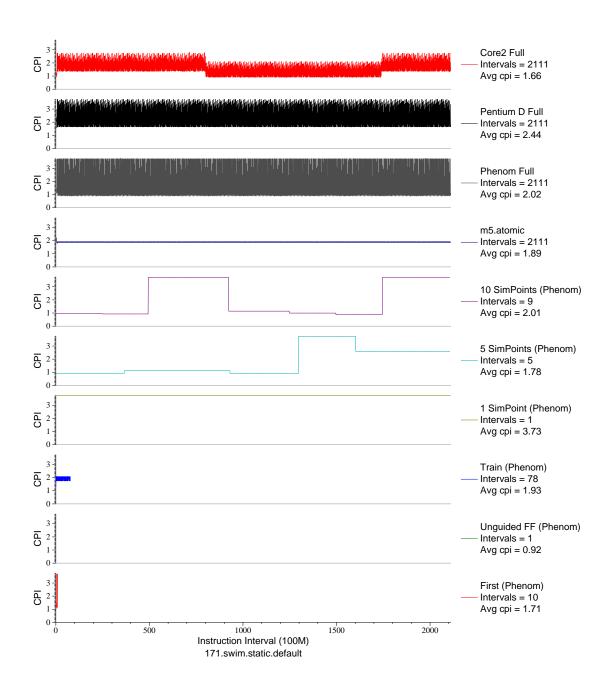

| E.7          | 1 1 , , ,                                                                                                                       | 71               |

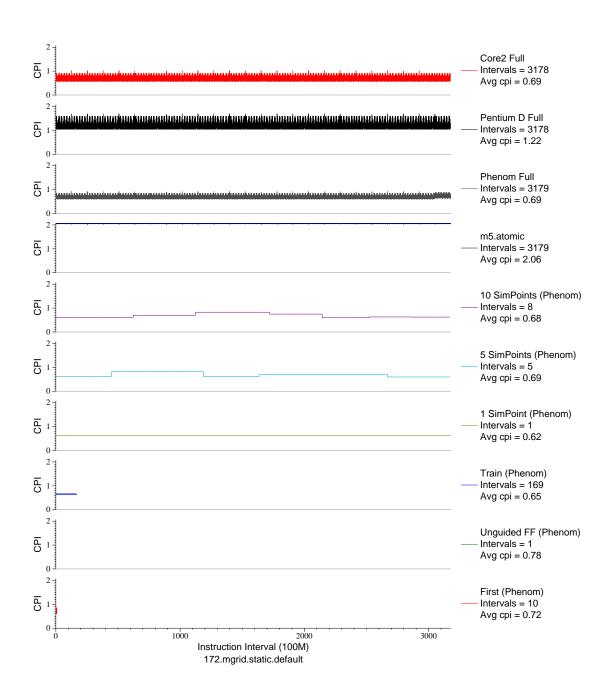

| E.8          |                                                                                                                                 | 72<br><b>-</b> 2 |

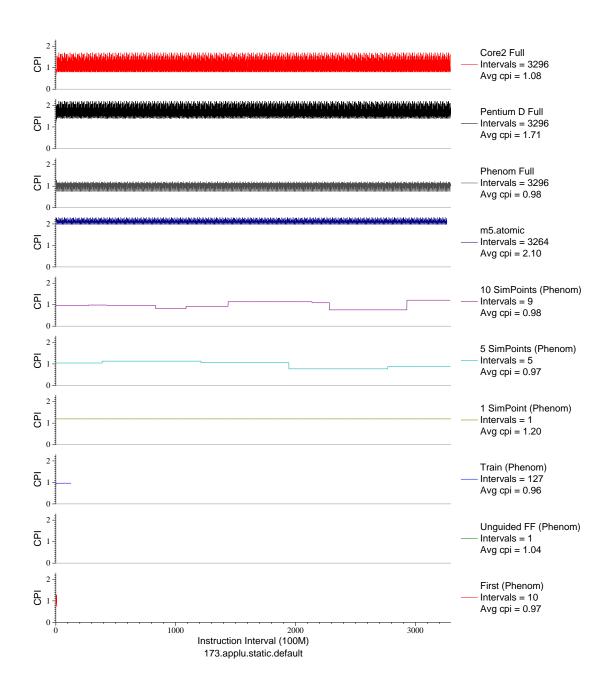

| E.9          | 1 1 \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                                                                           | 73<br>- 4        |

| E.10         | 1 1 \ \ / /                                                                                                                     | 74<br>75         |

| E.11         |                                                                                                                                 | 75<br>76         |

| E.12         | 1 1 ,                                                                                                                           | 76<br>77         |

| E.13<br>E.14 |                                                                                                                                 | 77<br>78         |

| E.14<br>E.15 |                                                                                                                                 | 70<br>79         |

|              | CPI phase plot for gcc.sci (INT, C, C Compiler)                                                                                 |                  |

|              |                                                                                                                                 | 81               |

|              | · · ·                                                                                                                           | 82               |

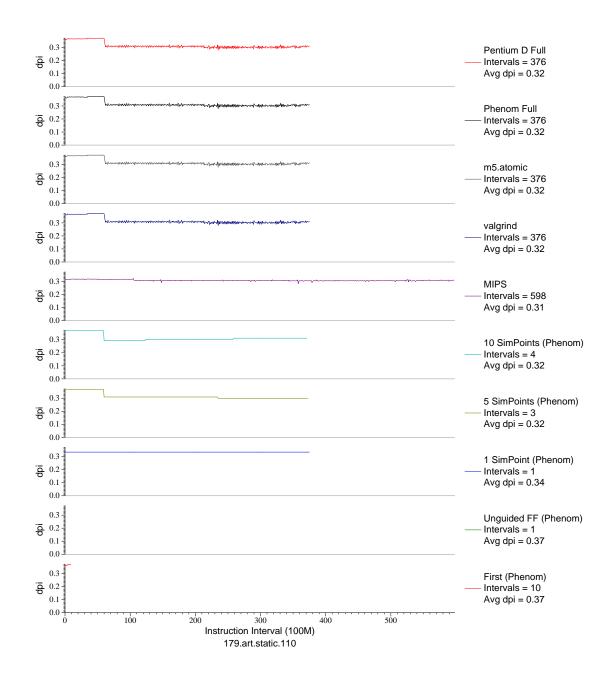

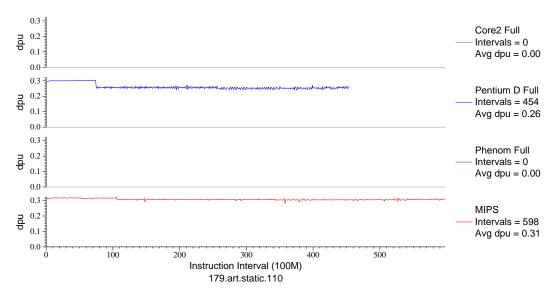

|              | CPI phase plot for art . 110 (FP, C, Neural Networks) 18                                                                        |                  |

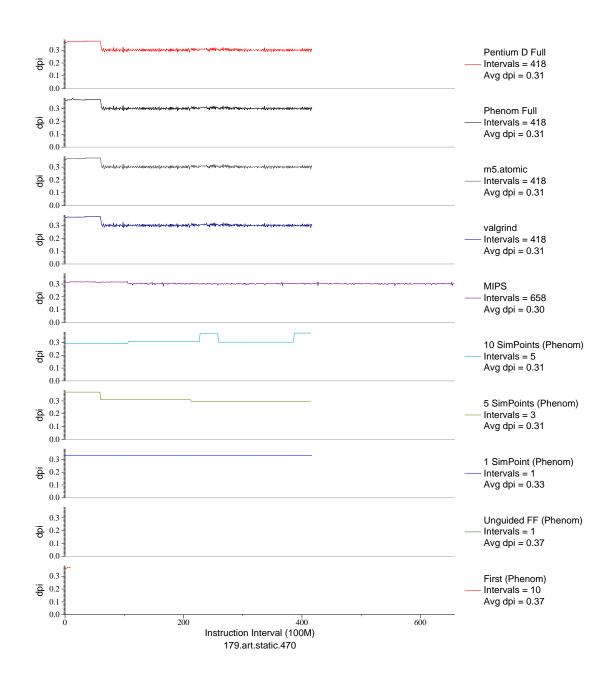

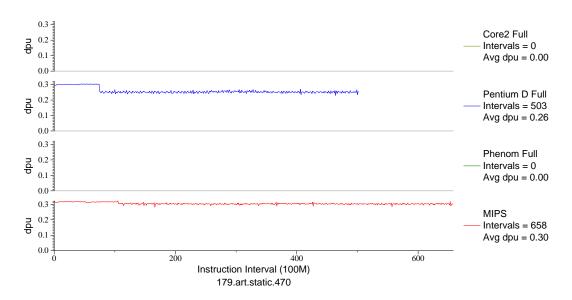

|              | CPI phase plot for art . 470 (FP, C, Neural Networks) 18                                                                        |                  |

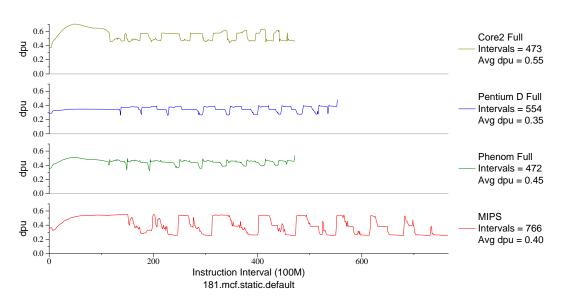

|              |                                                                                                                                 | 85               |

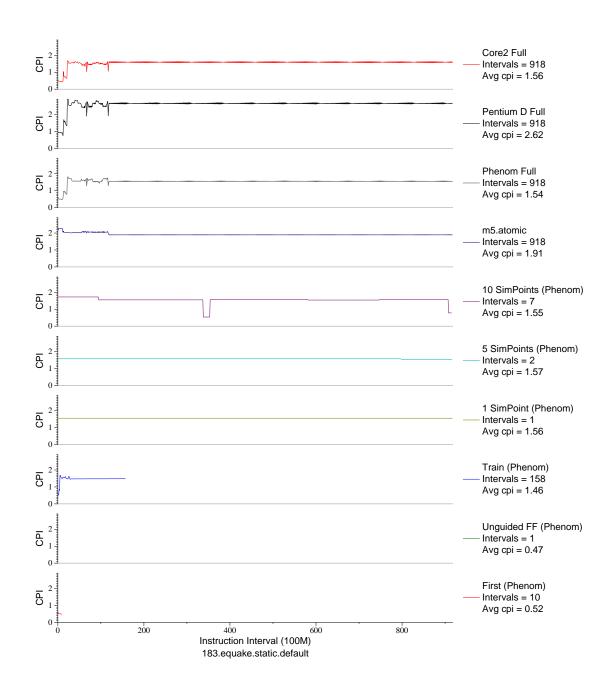

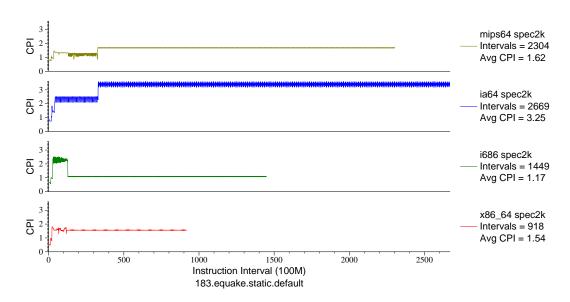

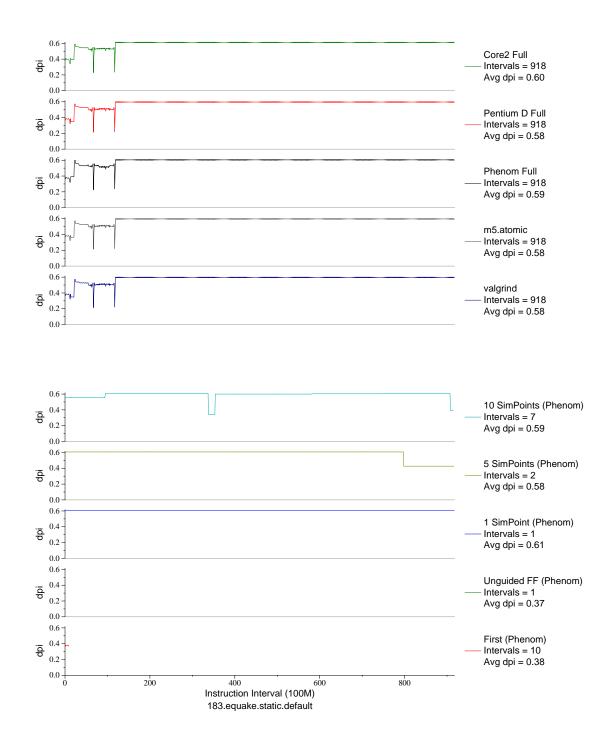

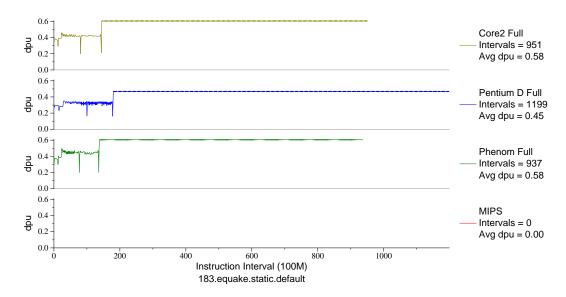

| E.22         | CPI phase plot for equake (FP, C, Seismic Propogation) 18                                                                       | 86               |

|              |                                                                                                                                 | 87               |

|              | 1 1 , , , , , , , , , , , , , , , , , ,                                                                                         | 88               |

|              | 1 1 = \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                                                                         | 89               |

|              | 1 1 , , , , ,                                                                                                                   | 90               |

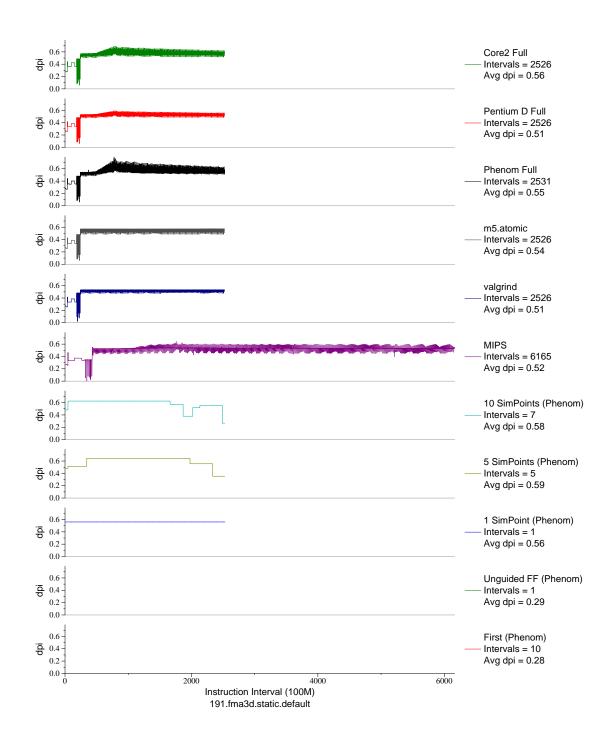

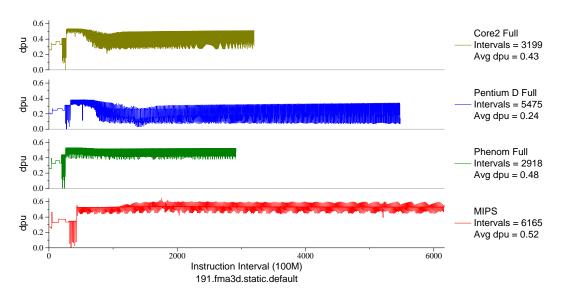

| E.27         | CPI phase plot for fma3d (FP, F90, Crash Simulation) 19                                                                         | 91               |

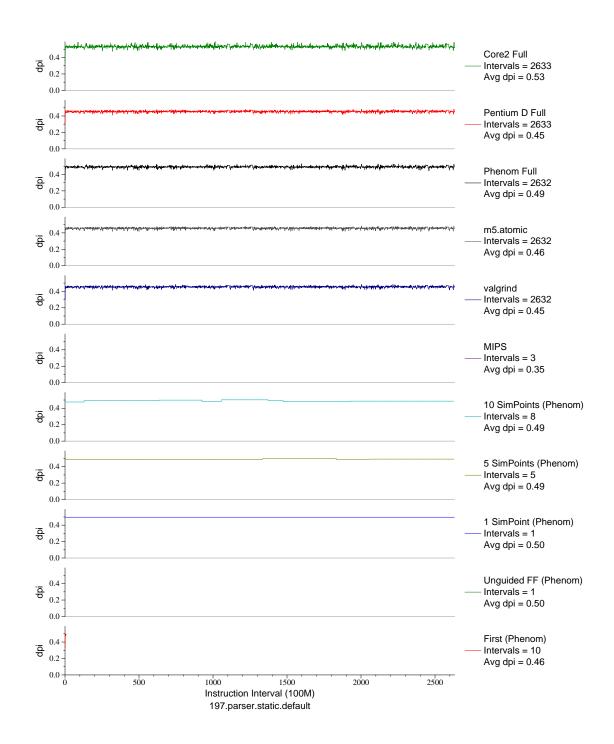

| E.28 | CPI phase plot for parser (INT, C, Word Processing)           | 192 |

|------|---------------------------------------------------------------|-----|

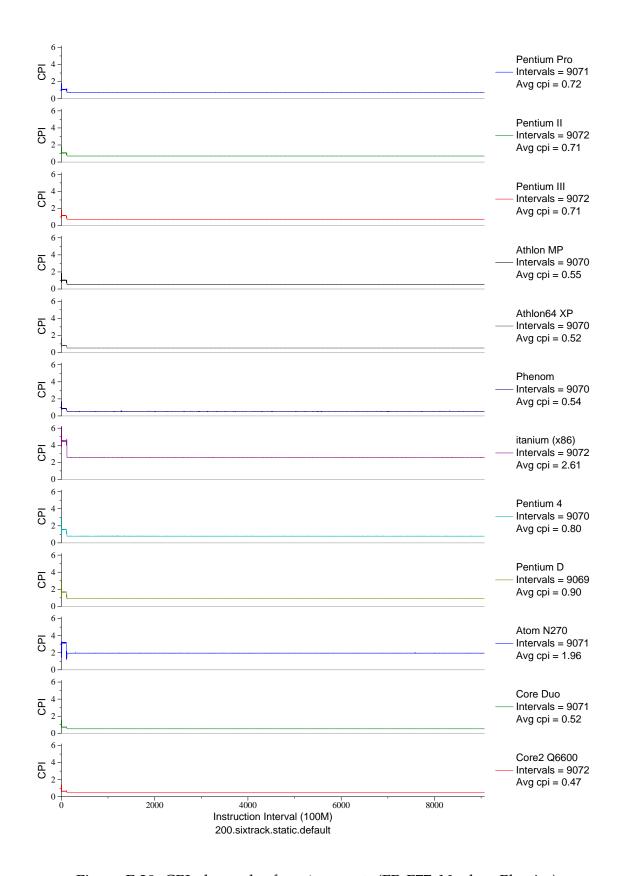

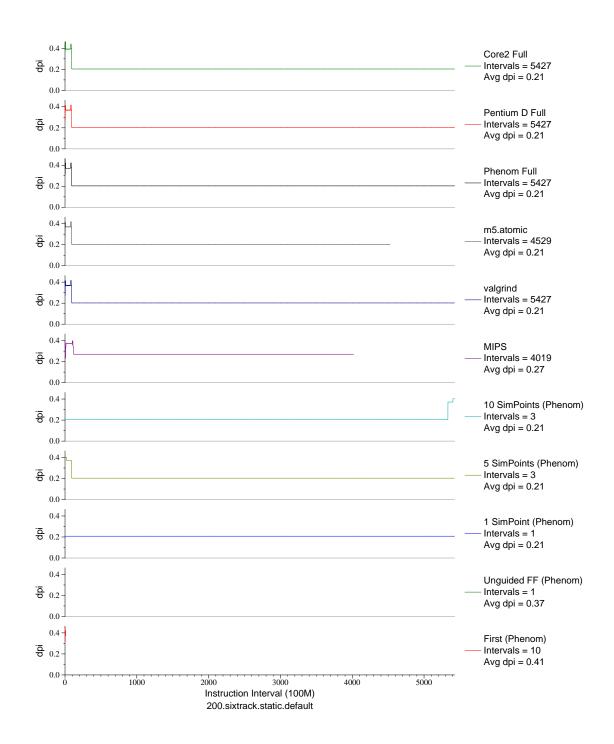

| E.29 | CPI phase plot for sixtrack (FP, F77, Nuclear Physics)        | 193 |

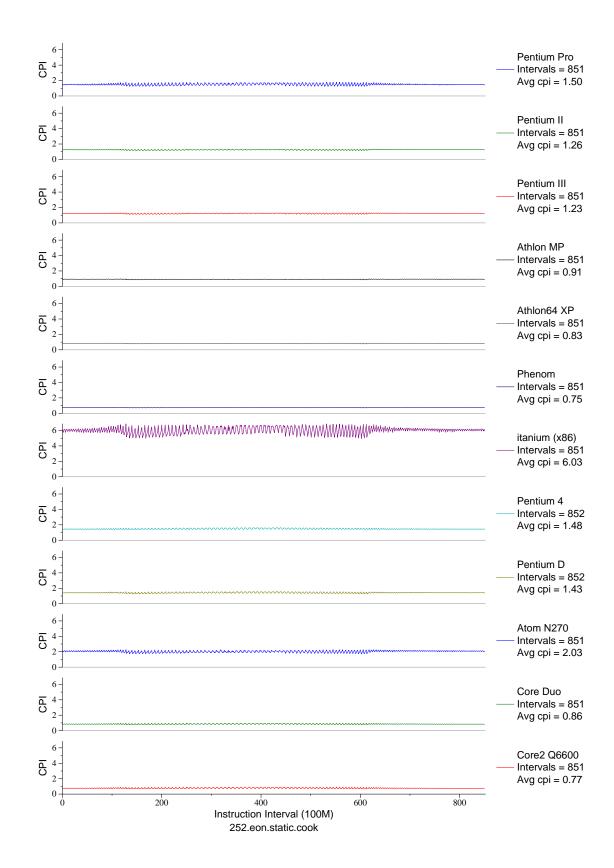

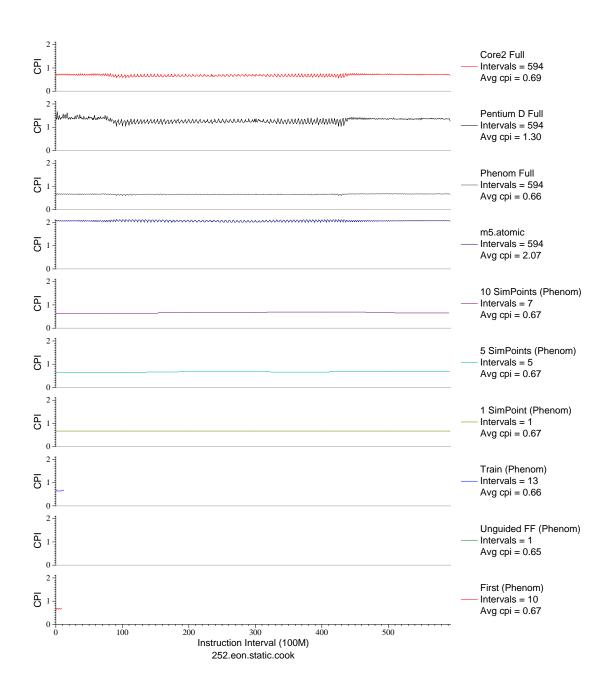

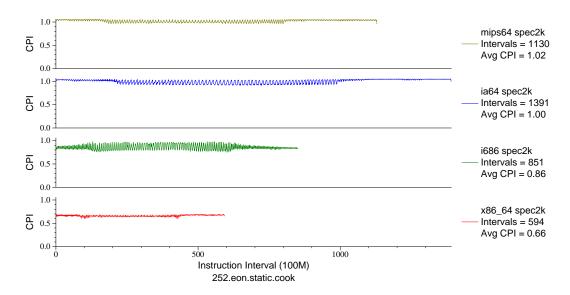

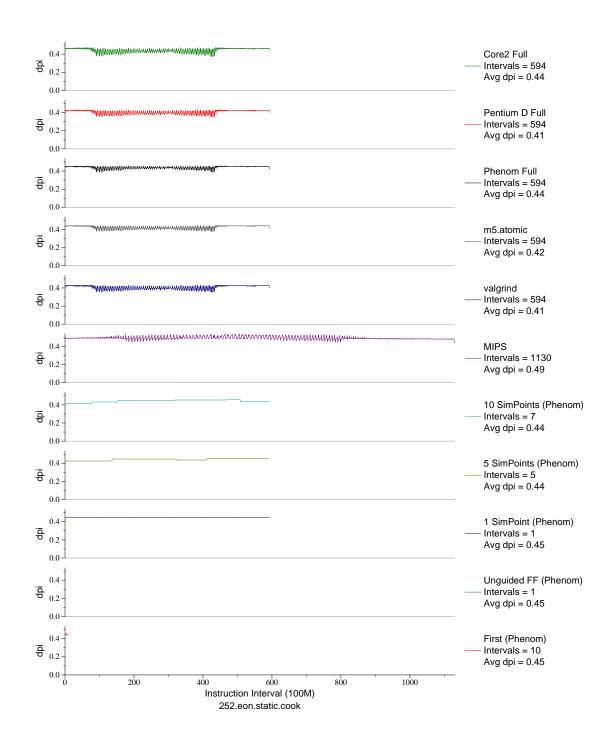

| E.30 | CPI phase plot for eon.cook (INT, C++, Computer Graphics)     | 194 |

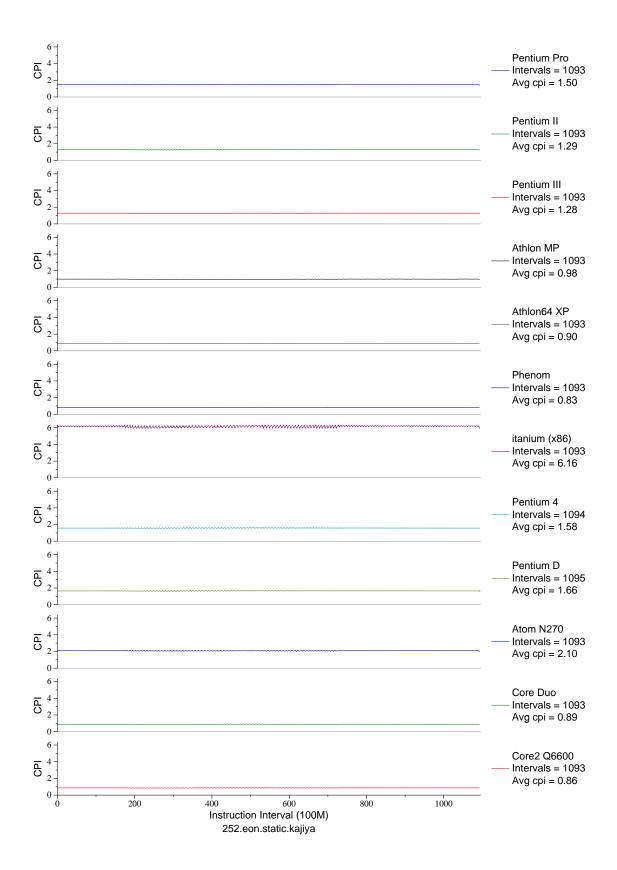

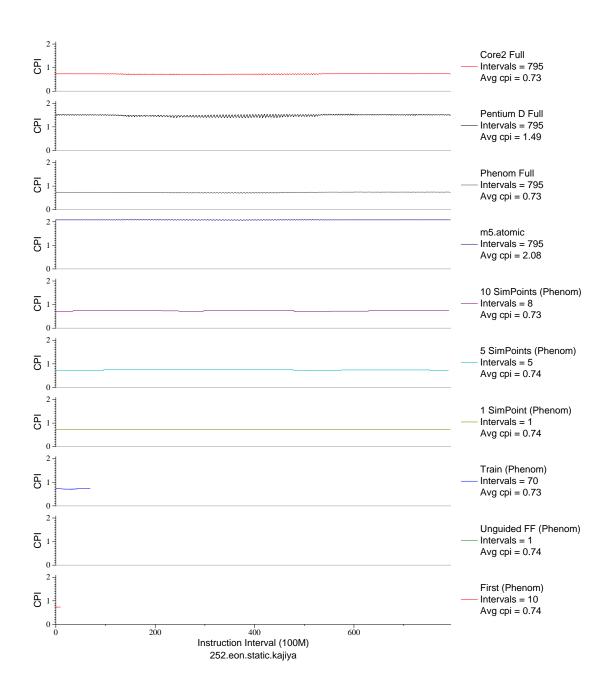

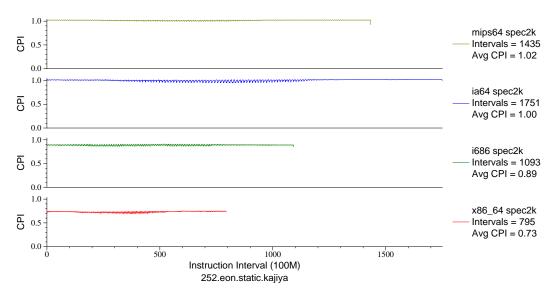

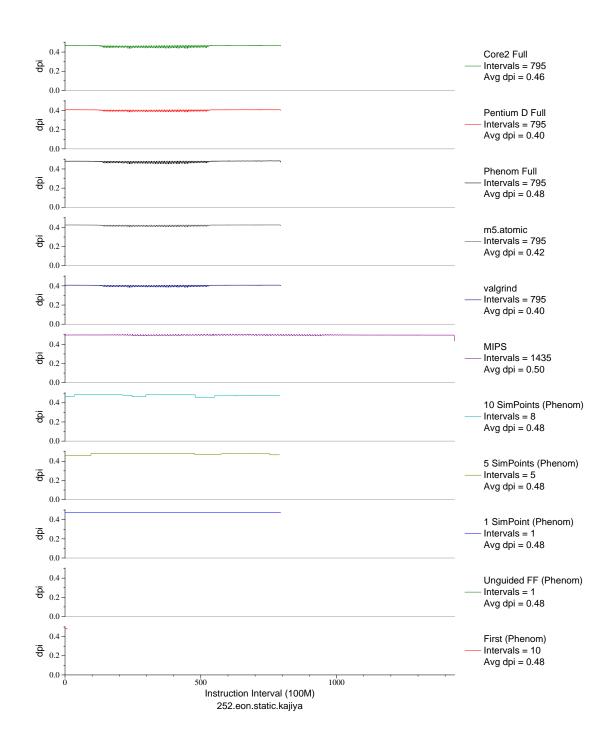

| E.31 | CPI phase plot for eon.kaj (INT, C++, Computer Graphics)      | 195 |

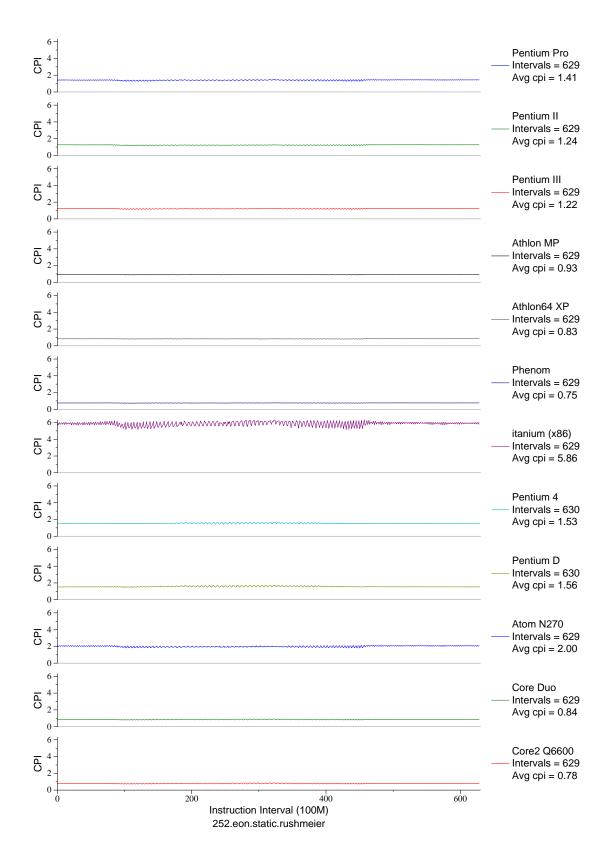

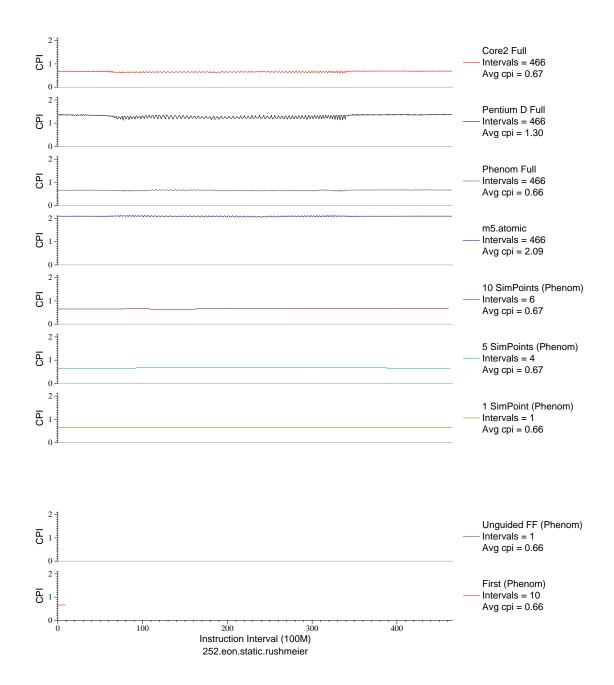

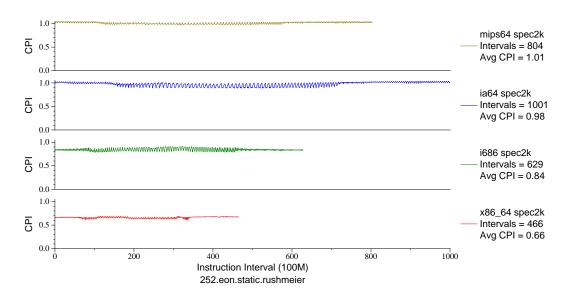

| E.32 | CPI phase plot for eon.rush (INT, C++, Computer Graphics)     | 196 |

| E.33 |                                                               | 197 |

| E.34 | 1 1                                                           | 198 |

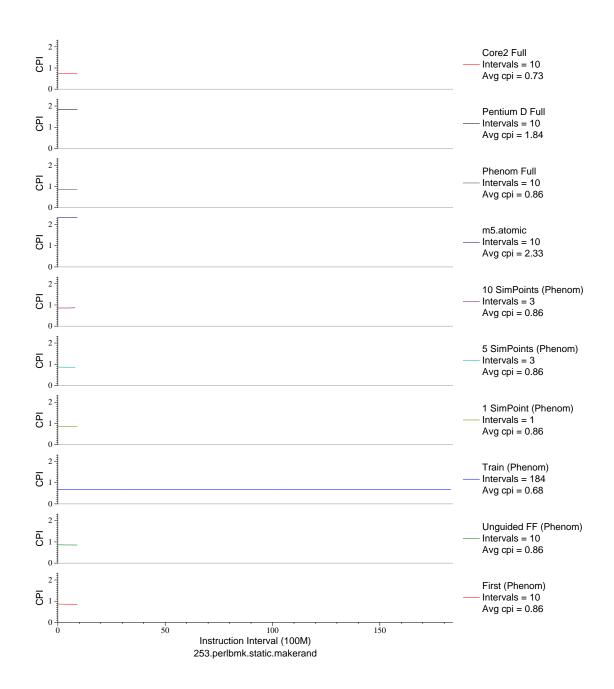

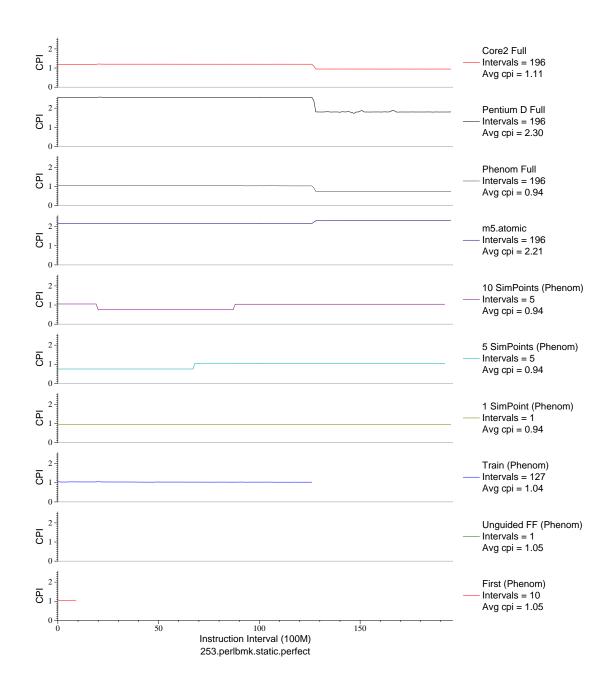

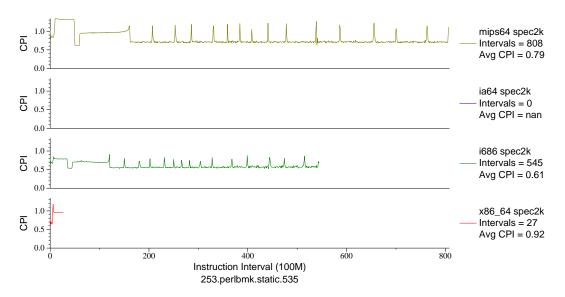

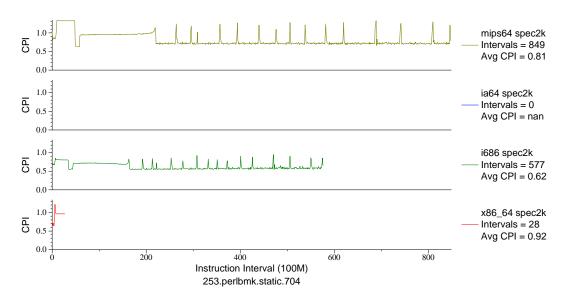

| E.35 | CPI phase plot for perlbmk. 850 (INT, C, Scripting Language). | 199 |

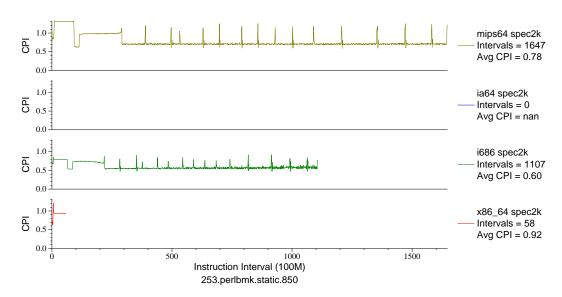

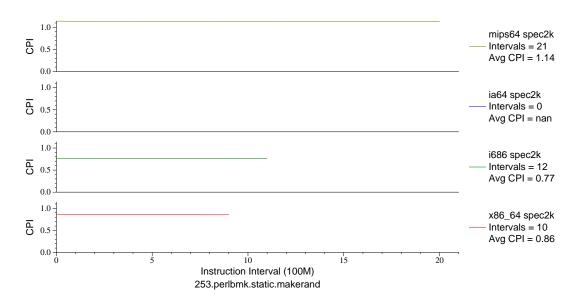

| E.36 | CPI phase plot for perlbmk . 957 (INT, C, Scripting Language) | 200 |

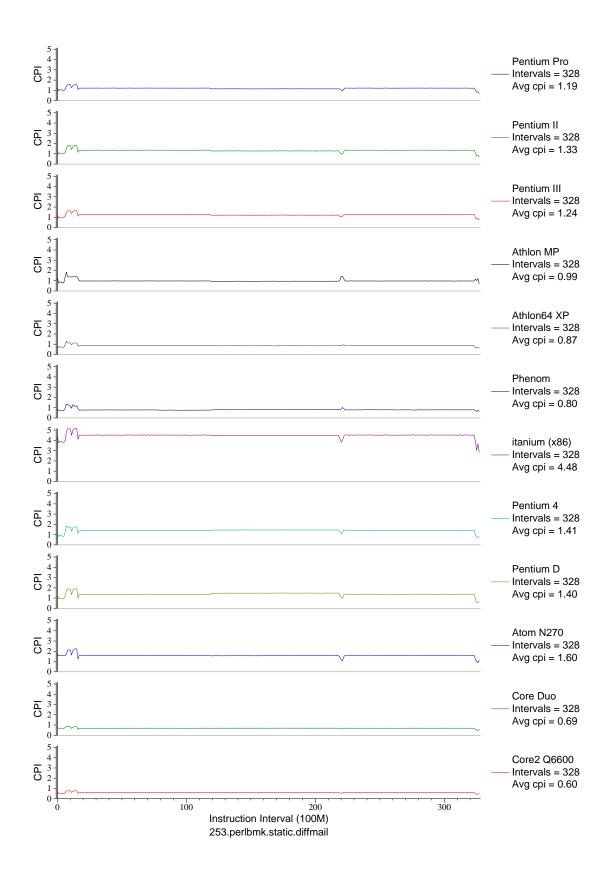

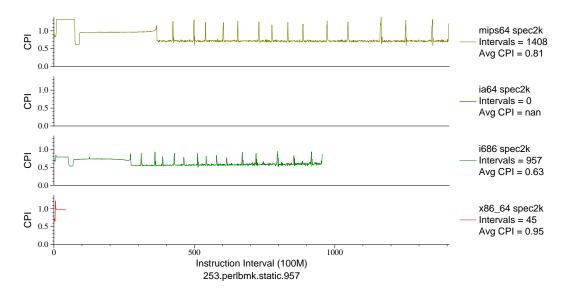

| E.37 | CPI phase plot for perlbmk.diff (INT, C, Scripting Language)  | 201 |

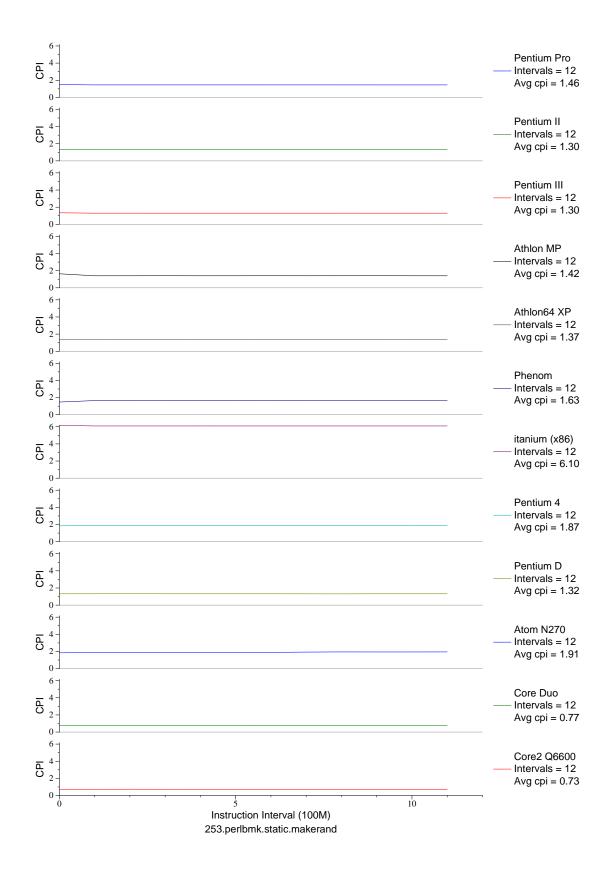

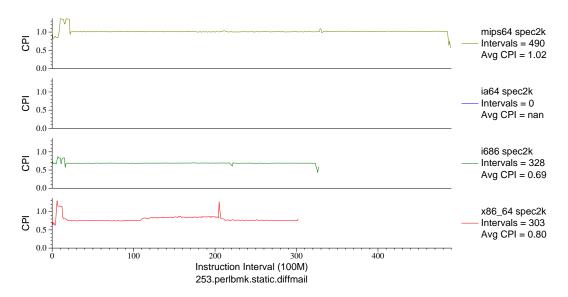

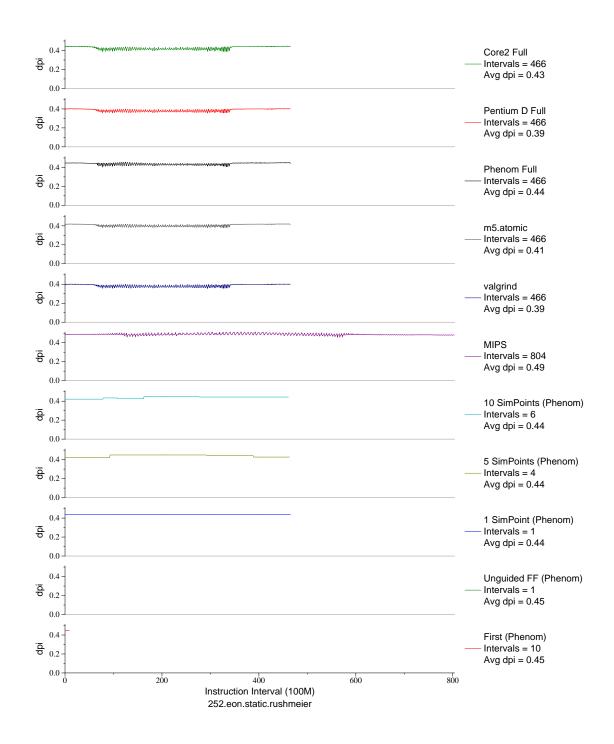

| E.38 | CPI phase plot for perlbmk.mkrnd (INT, C, Scripting Language) | 202 |

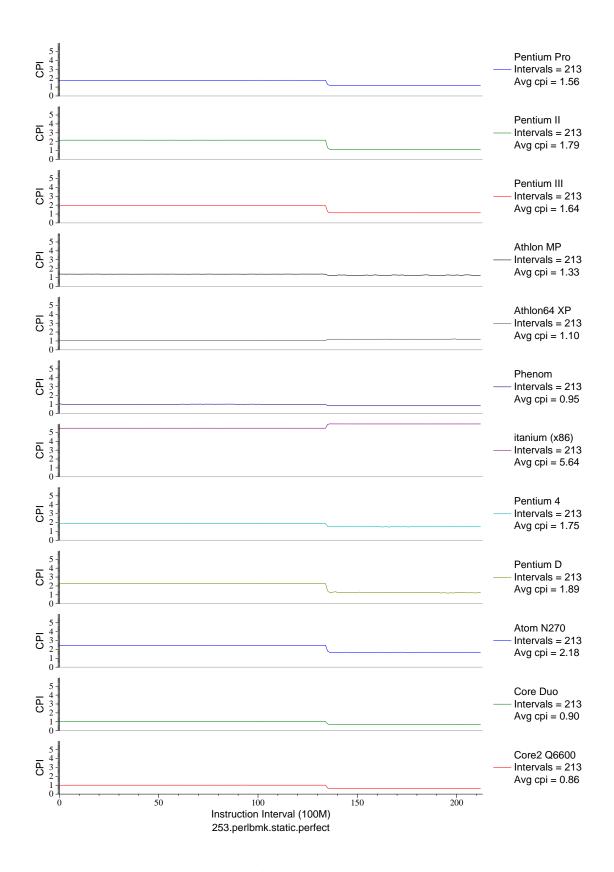

| E.39 | CPI phase plot for perlbmk.perf (INT, C, Scripting Language)  | 203 |

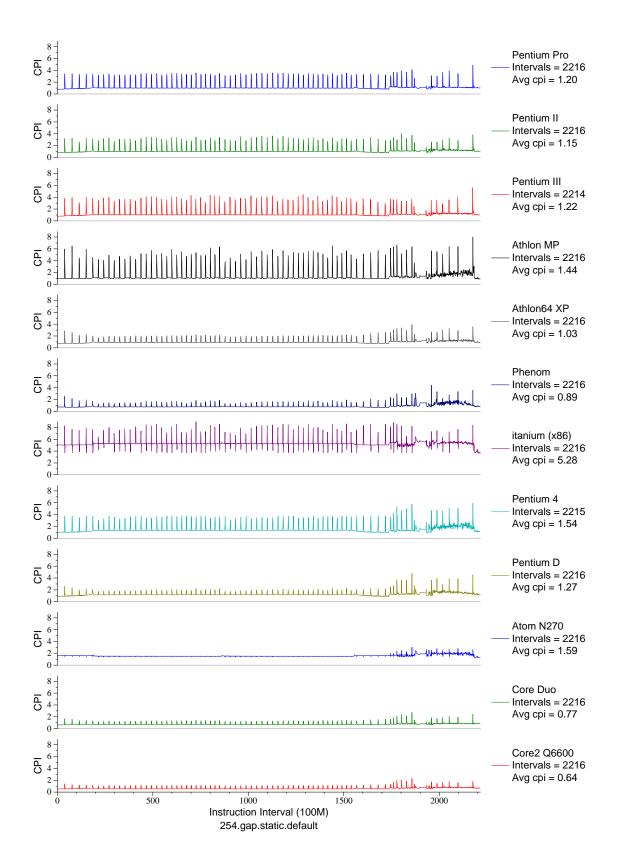

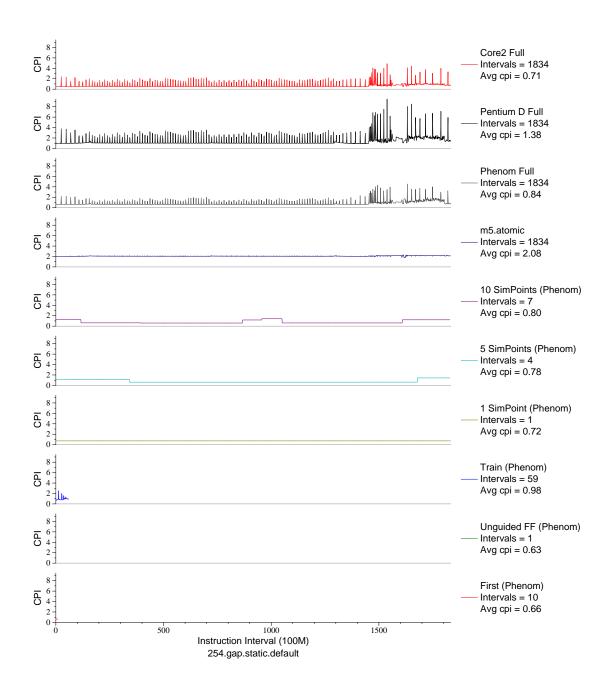

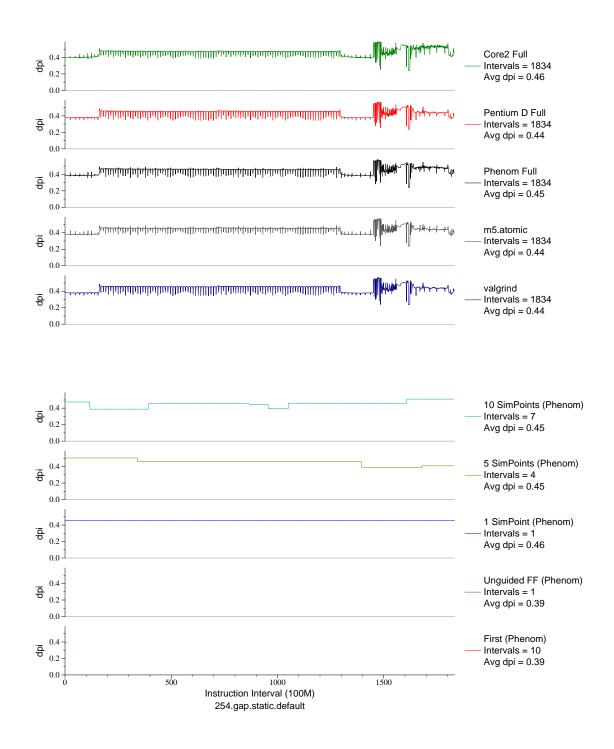

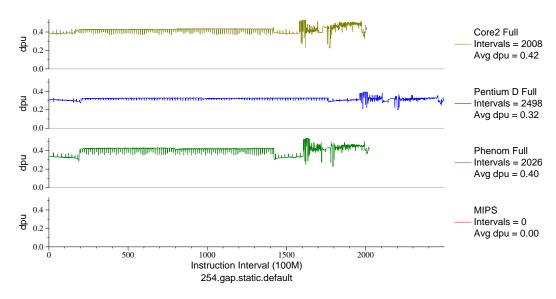

| E.40 | CPI phase plot for gap (INT, C, Group Theory)                 | 204 |

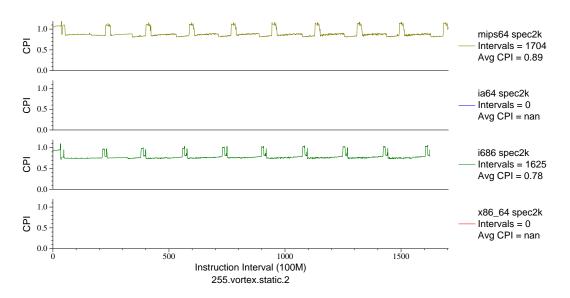

| E.41 | CPI phase plot for vortex.1 (INT, C, Database)                | 205 |

| E.42 | CPI phase plot for vortex. 2 (INT, C, Database)               | 206 |

| E.43 | CPI phase plot for vortex. 3 (INT, C, Database)               | 207 |

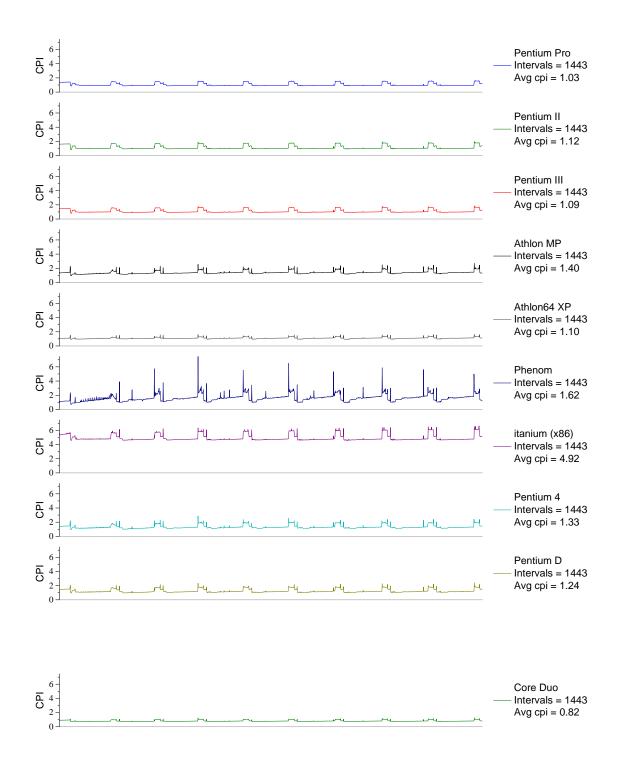

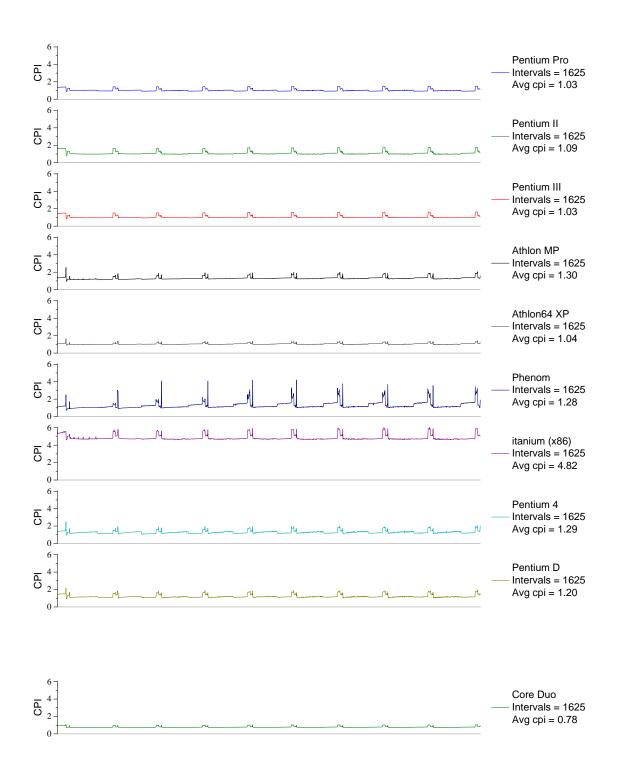

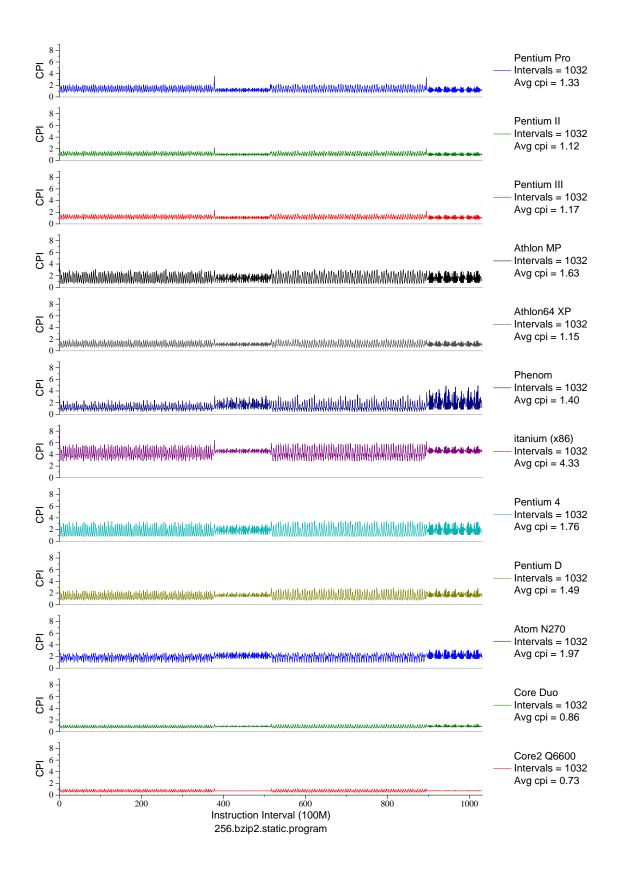

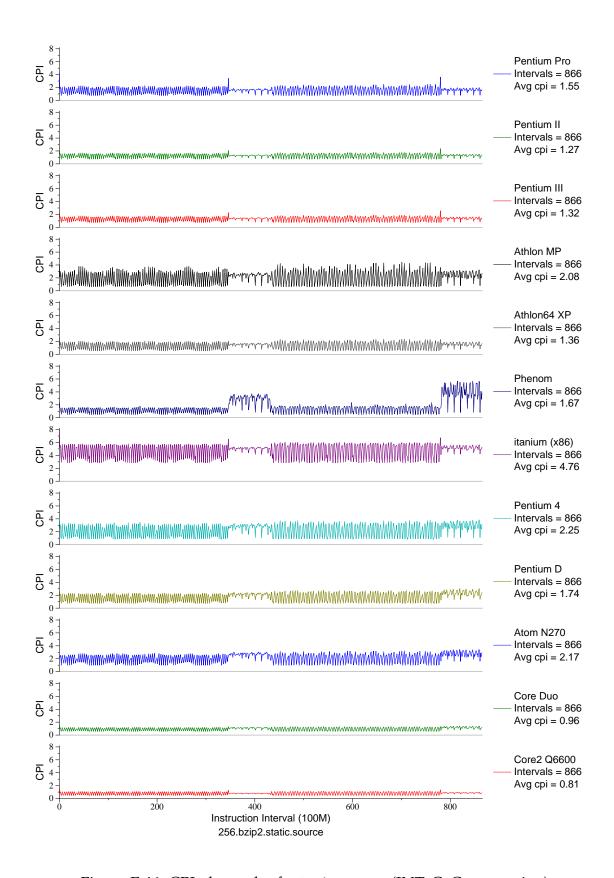

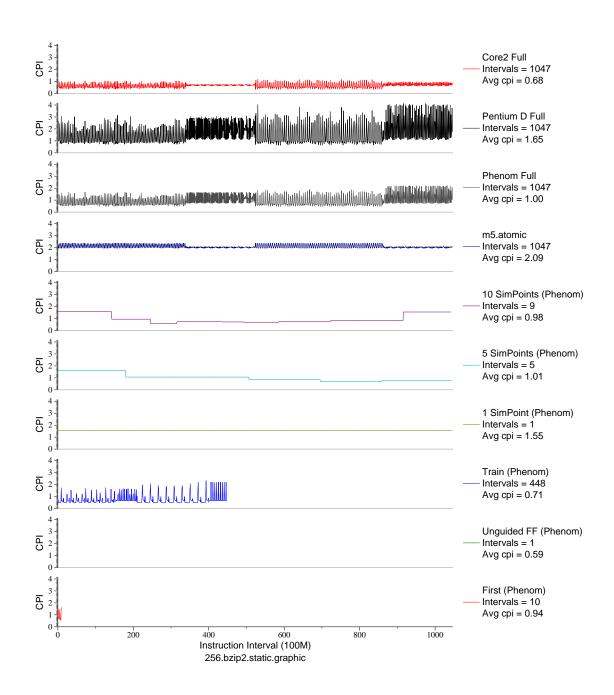

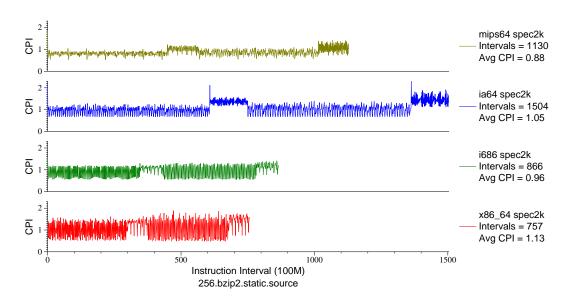

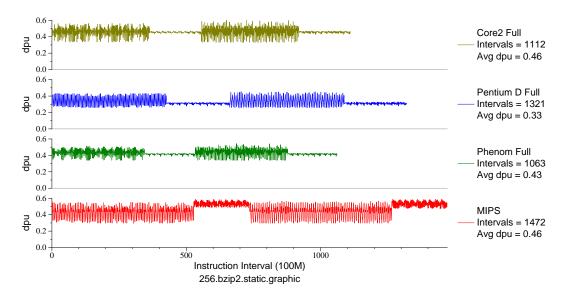

| E.44 | CPI phase plot for bzip2.graph (INT, C, Compression)          | 208 |

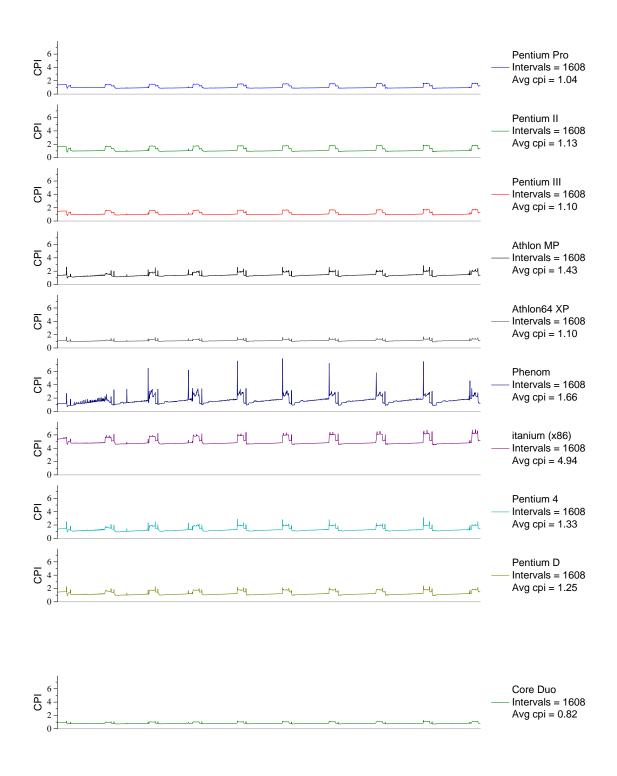

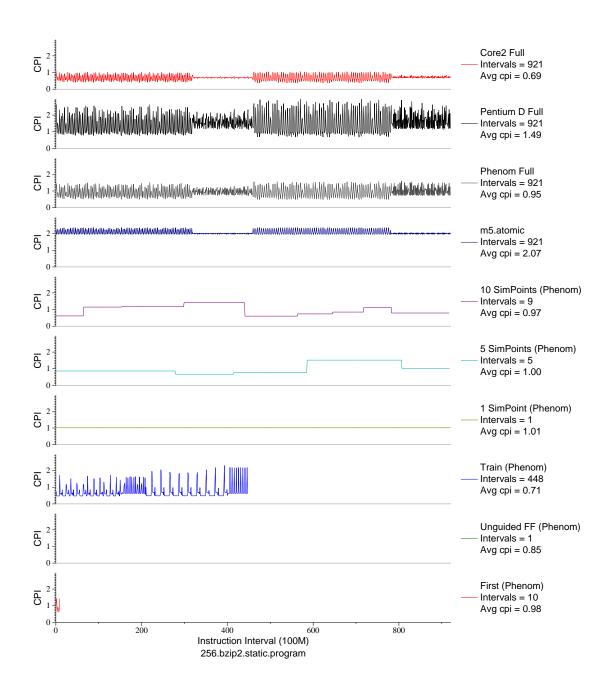

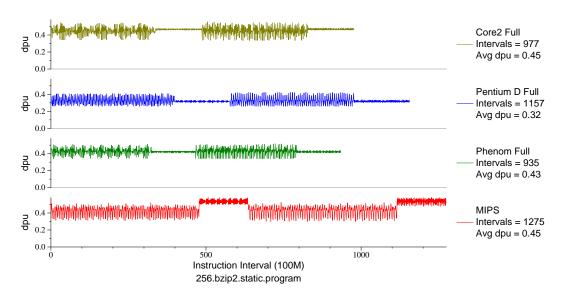

| E.45 | CPI phase plot for bzip2.prog (INT, C, Compression)           | 209 |

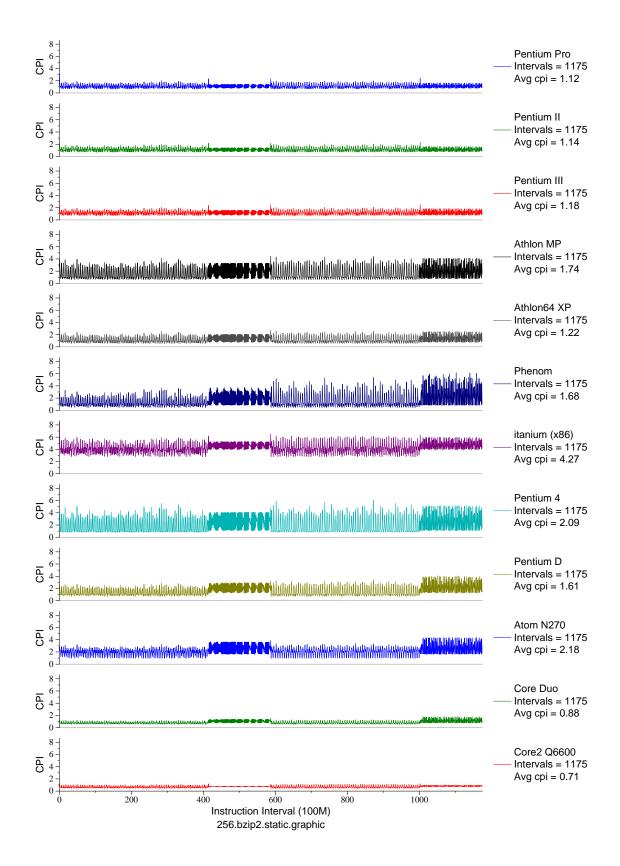

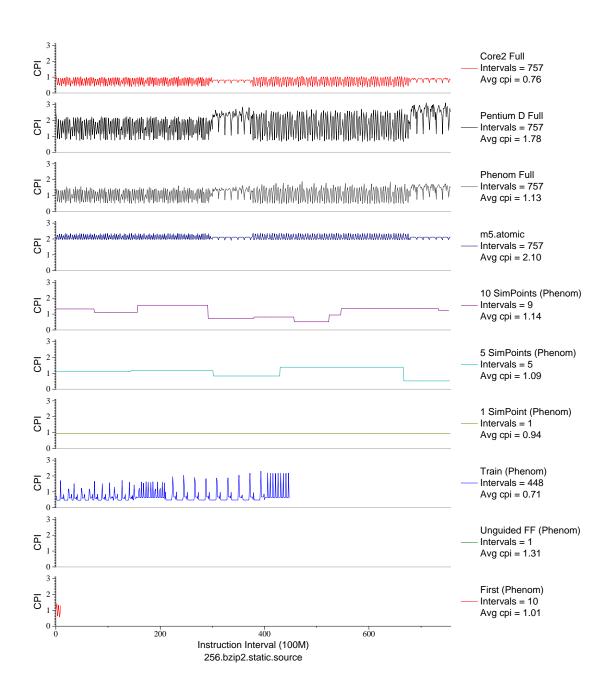

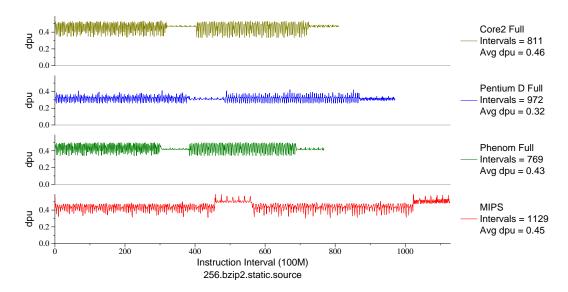

| E.46 | CPI phase plot for bzip2.src (INT, C, Compression)            | 210 |

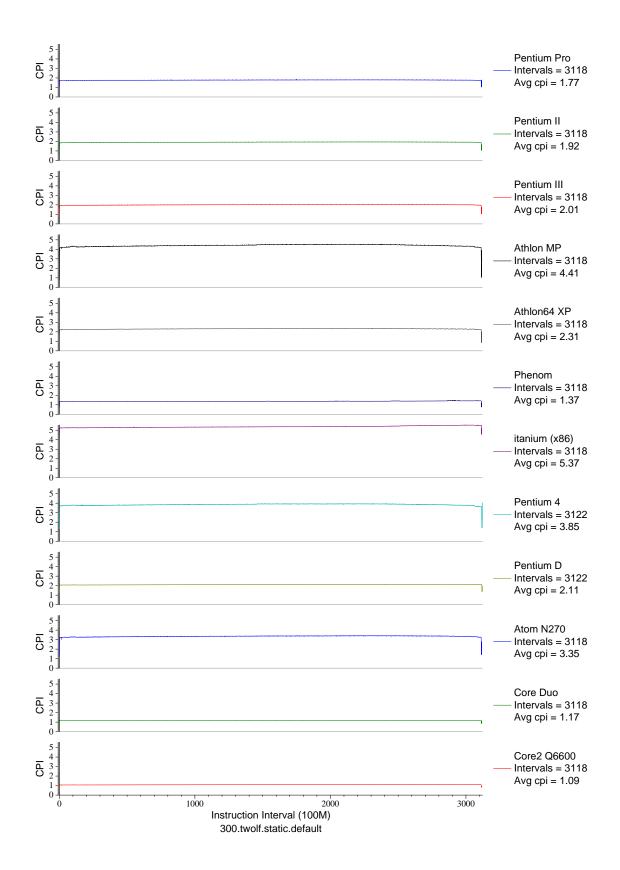

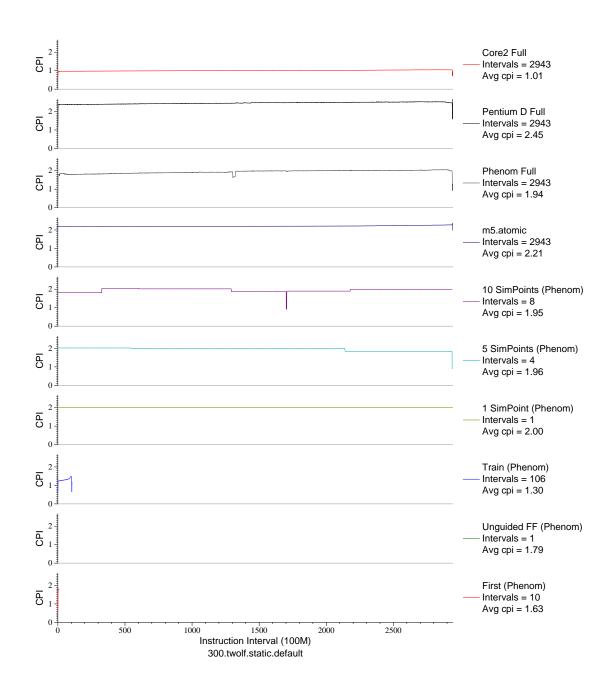

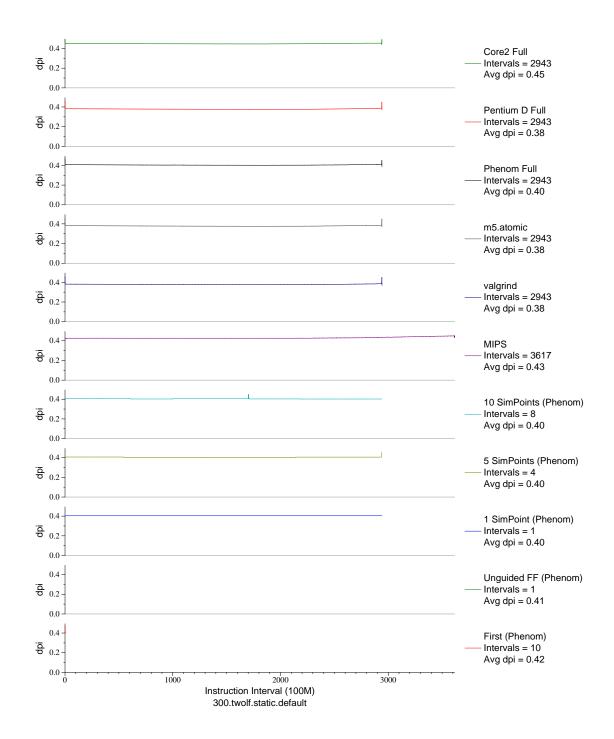

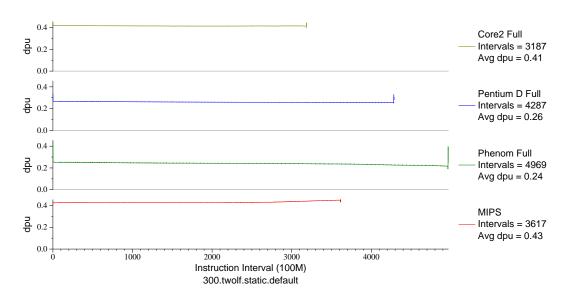

| E.47 | CPI phase plot for twolf (INT, C, Place/Route)                | 211 |

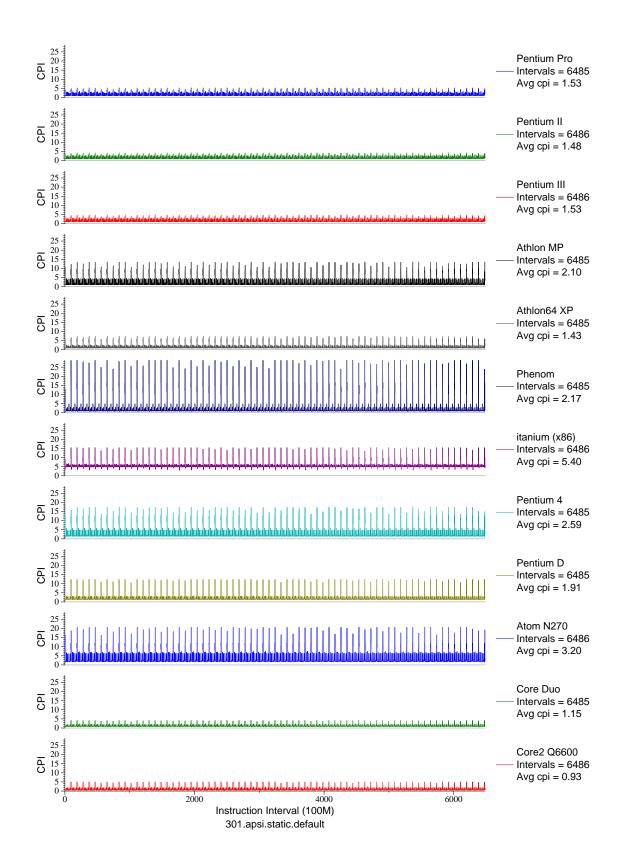

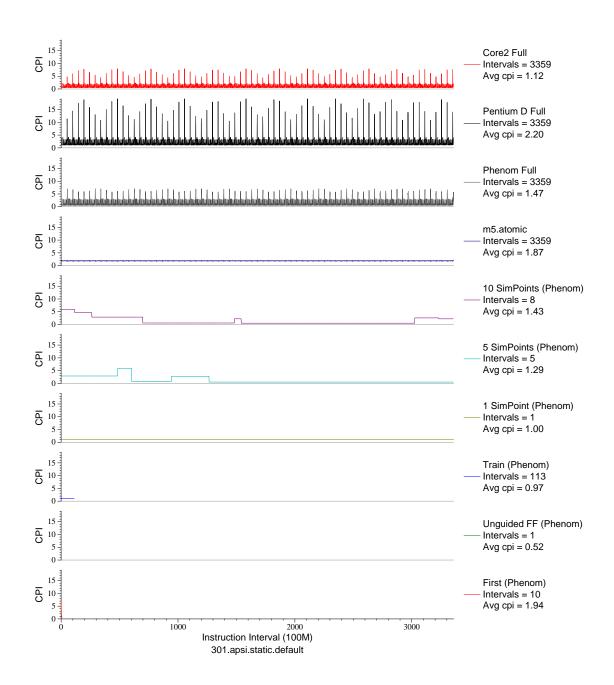

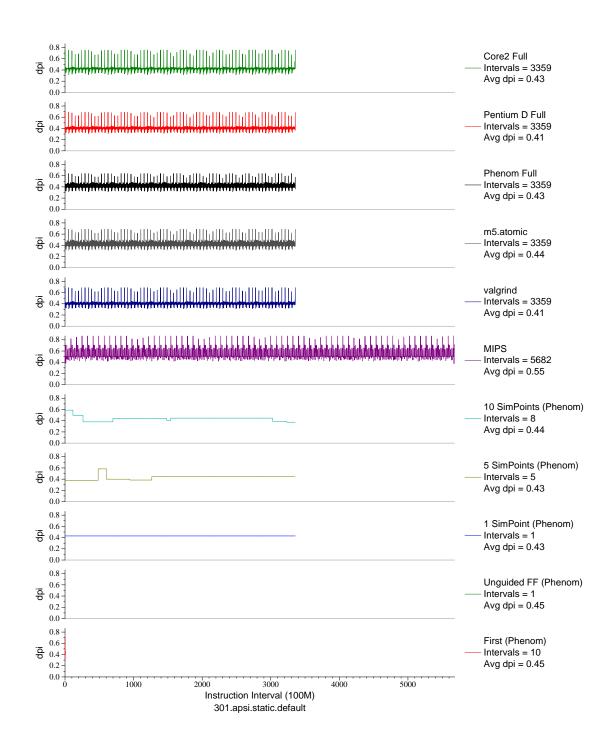

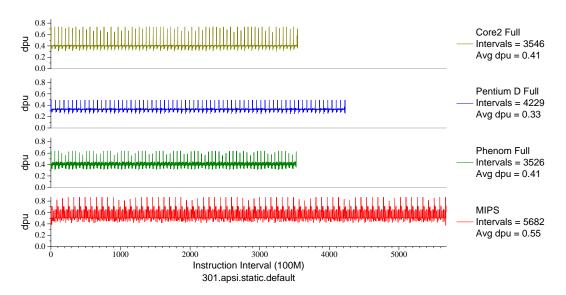

| E.48 | CPI phase plot for apsi (FP, F77, Meteorology/Pollution)      | 212 |

| E.49 | CPI phase plot for gzip.graph (INT, C, Compression)           | 214 |

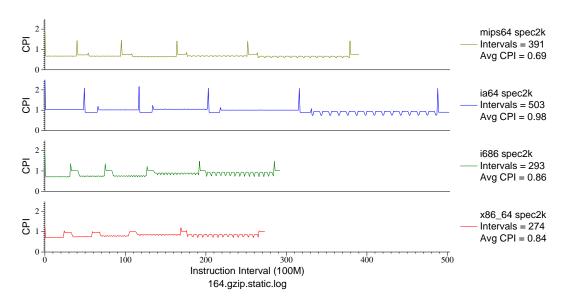

| E.50 | CPI phase plot for gzip.log (INT, C, Compression)             | 215 |

| E.51 | CPI phase plot for gzip.prog (INT, C, Compression)            | 216 |

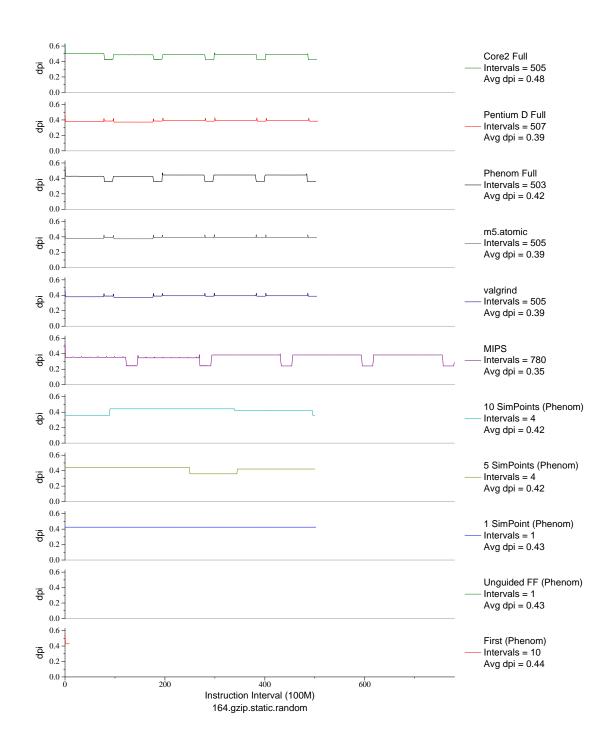

| E.52 | CPI phase plot for gzip.rnd (INT, C, Compression)             | 217 |

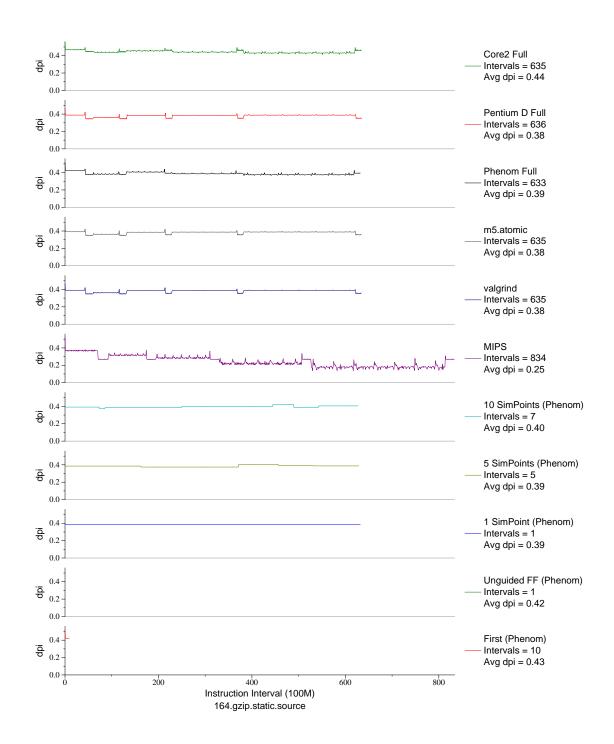

| E.53 | CPI phase plot for gzip.src (INT, C, Compression)             | 218 |

| E.54 | CPI phase plot for wupwise (FP, F77, Quantum Chromodynamics). | 219 |

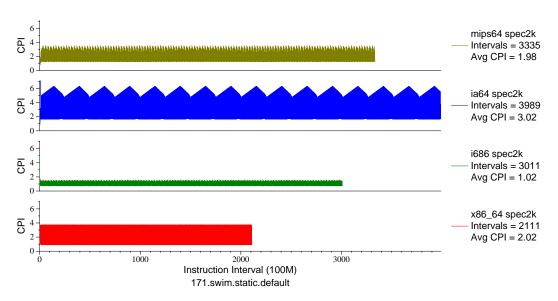

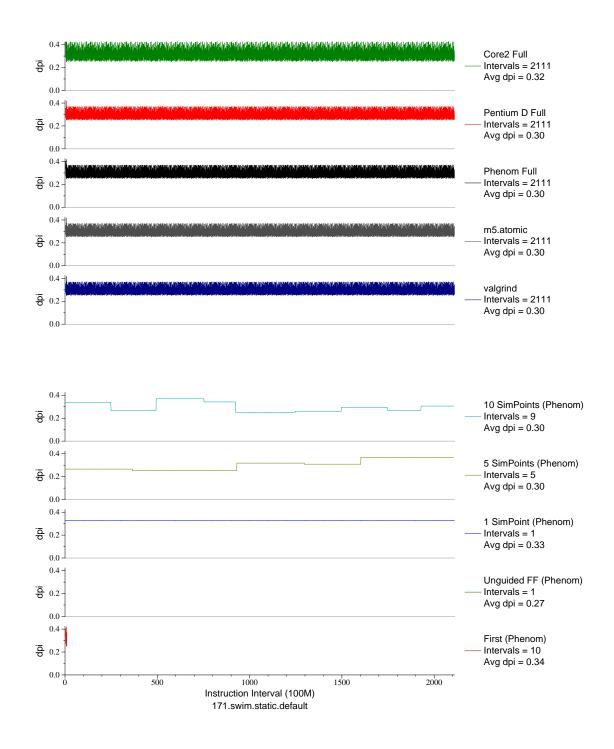

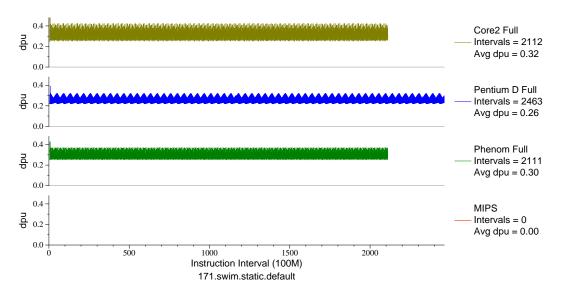

| E.55 | CPI phase plot for swim (FP, F77, Meteorology/Water)          | 220 |

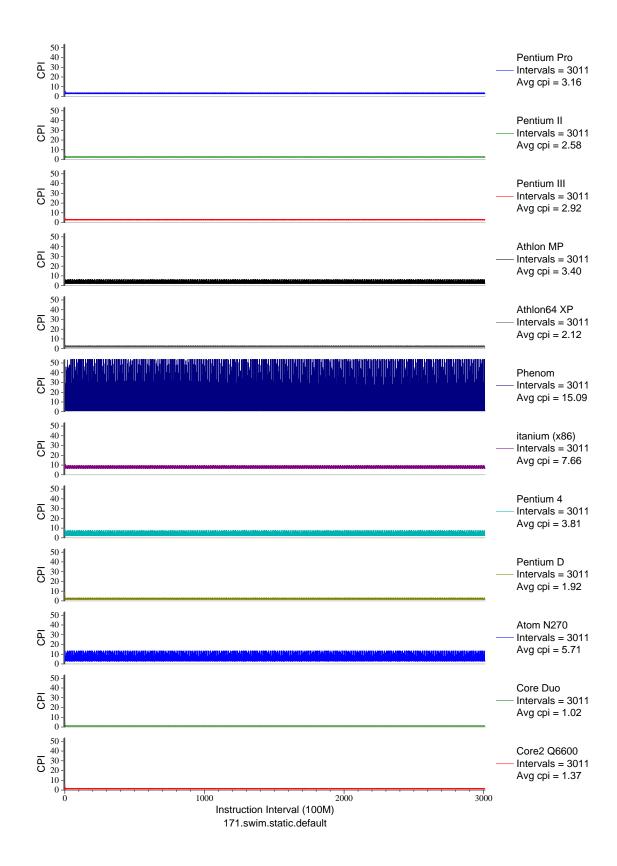

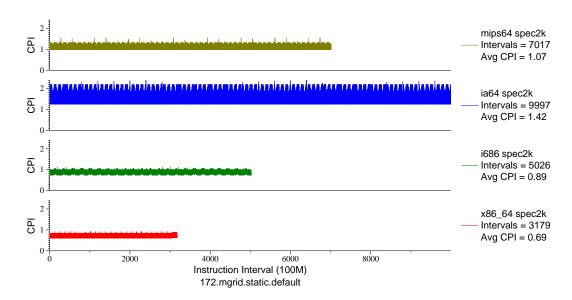

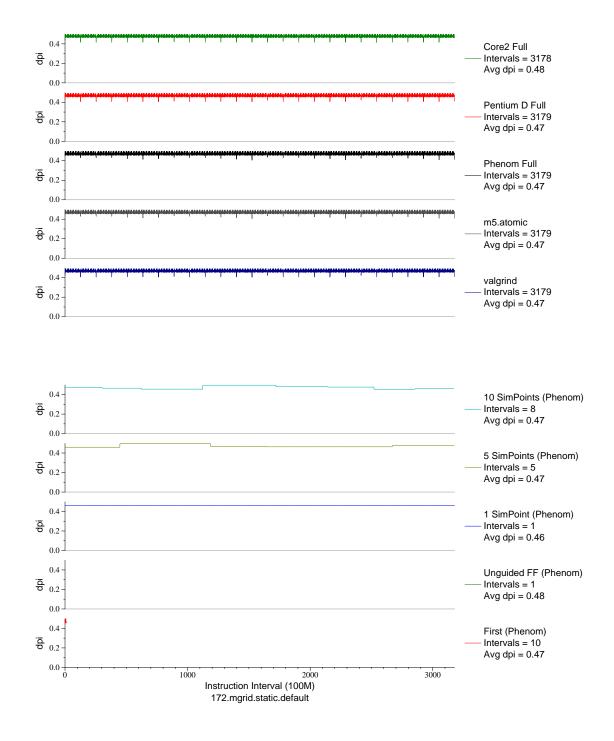

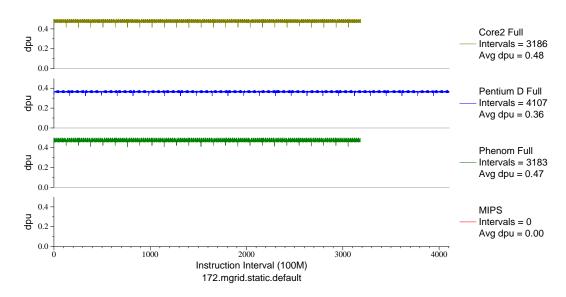

| E.56 | CPI phase plot for mgrid (FP, F77, Multi-Grid Solver)         | 221 |

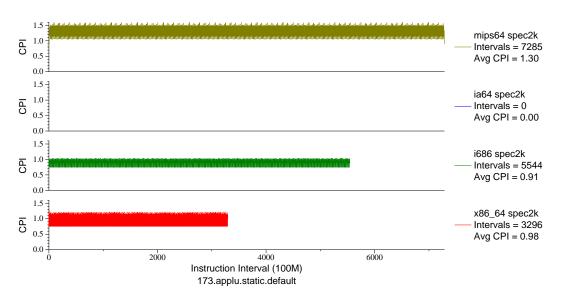

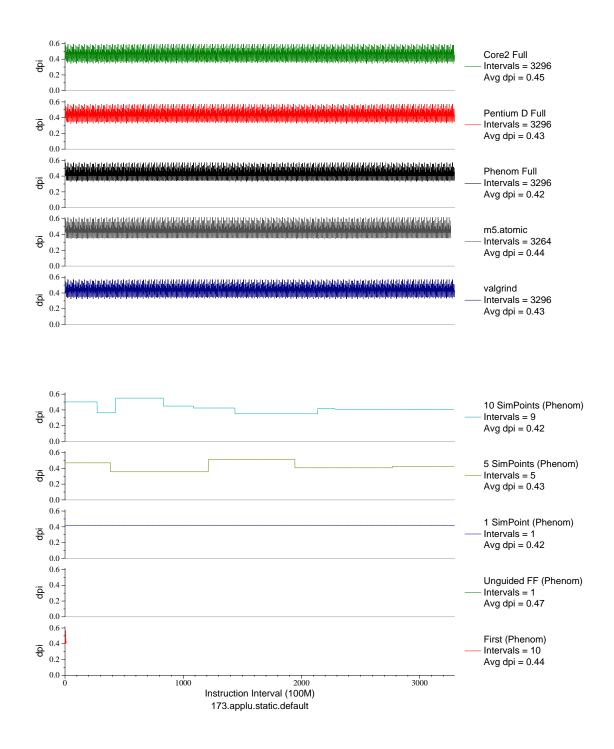

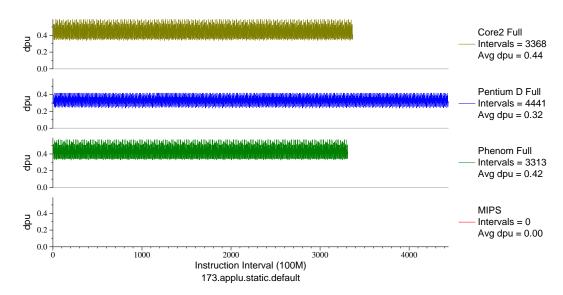

| E.57 |                                                               | 222 |

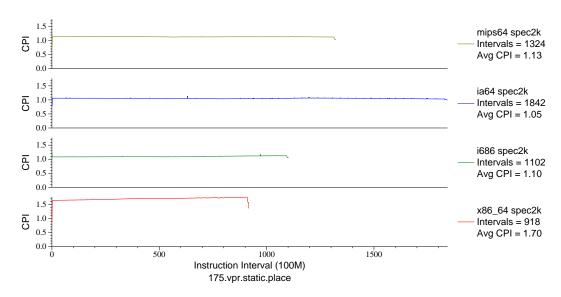

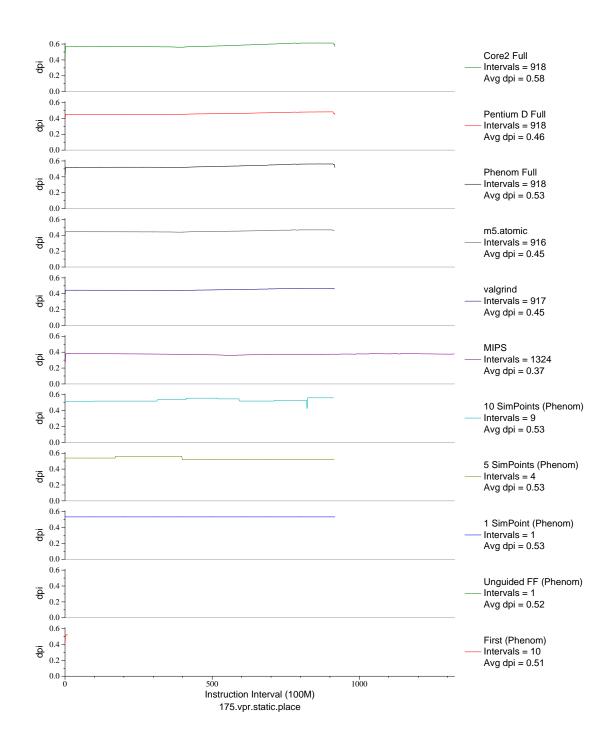

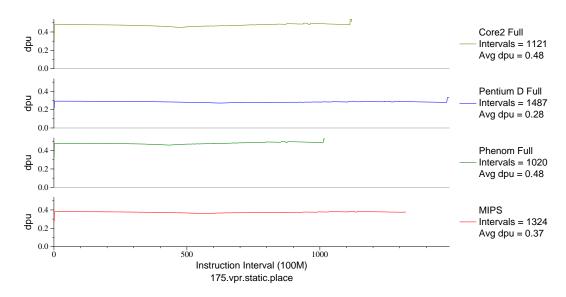

| E.58 | CPI phase plot for vpr.place (INT, C, FPGA Place/Route)       | 223 |

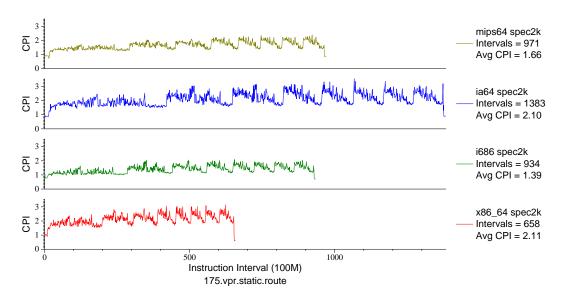

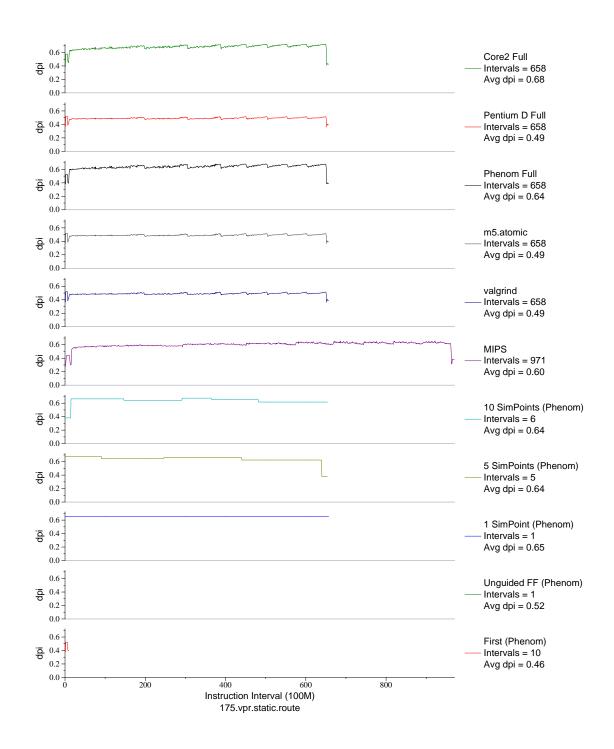

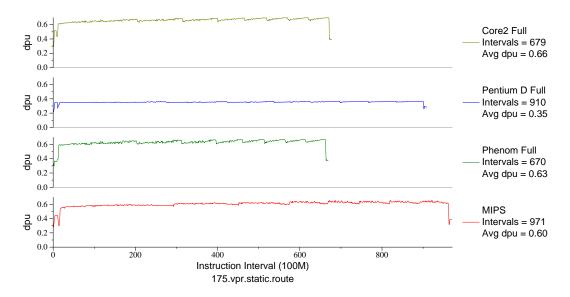

|      | CPI phase plot for vpr.route (INT, C, FPGA Place/Route)       |     |

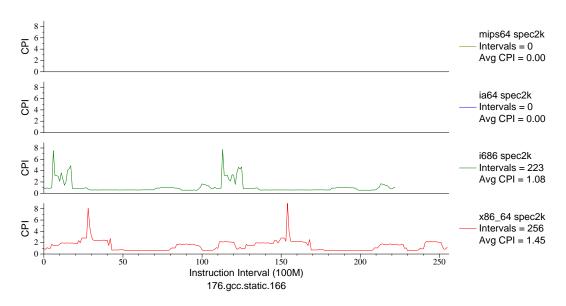

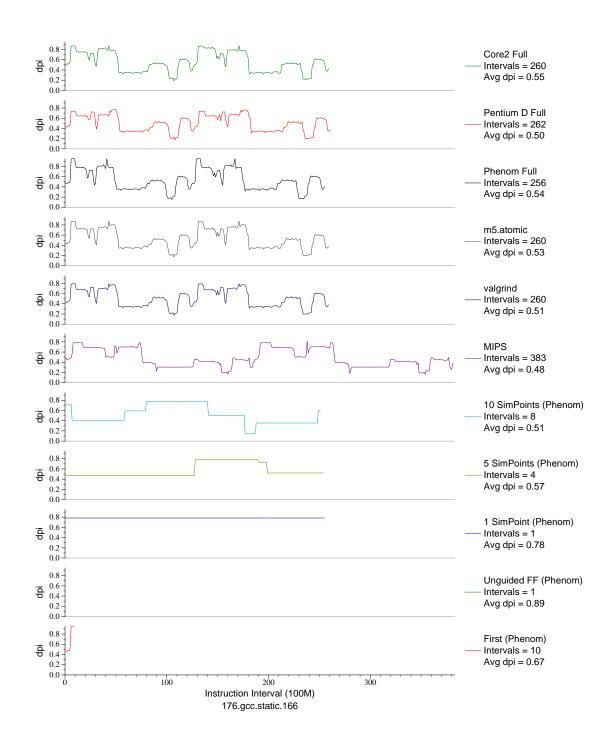

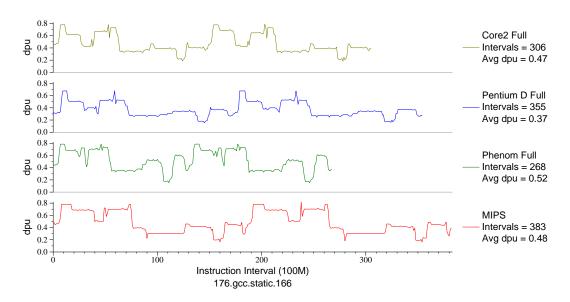

| E.60 | CPI phase plot for gcc.166 (INT, C, C Compiler)               | 225 |

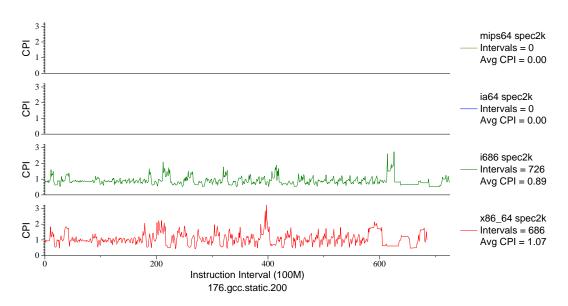

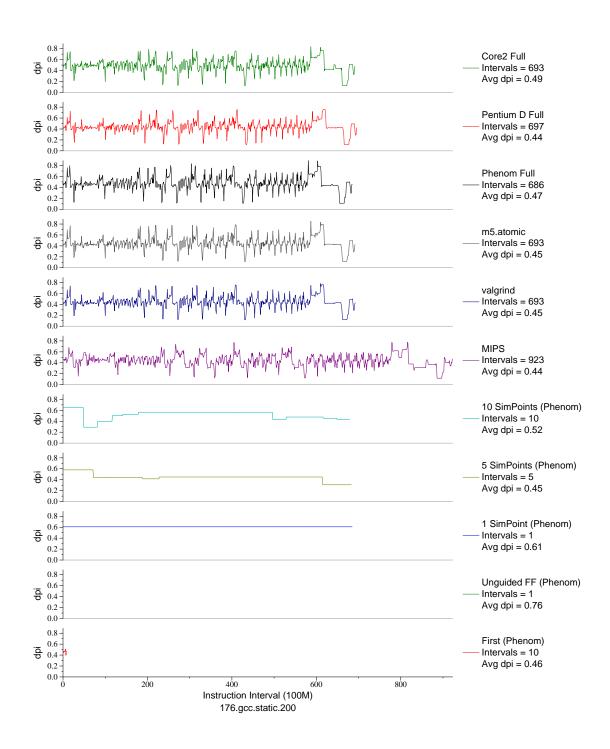

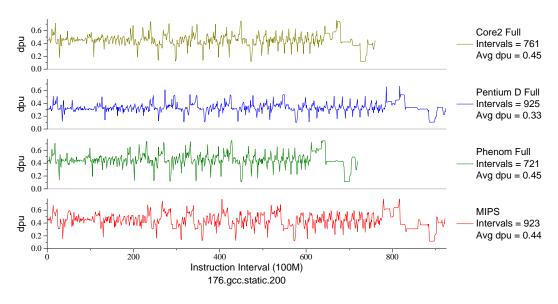

| E.61 | CPI phase plot for gcc. 200 (INT, C, C Compiler)              |     |

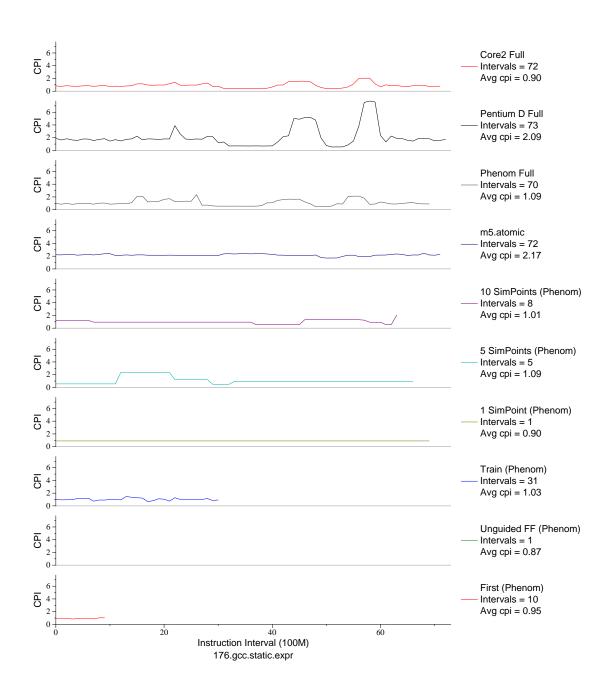

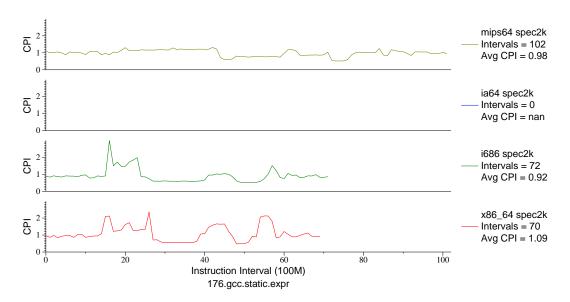

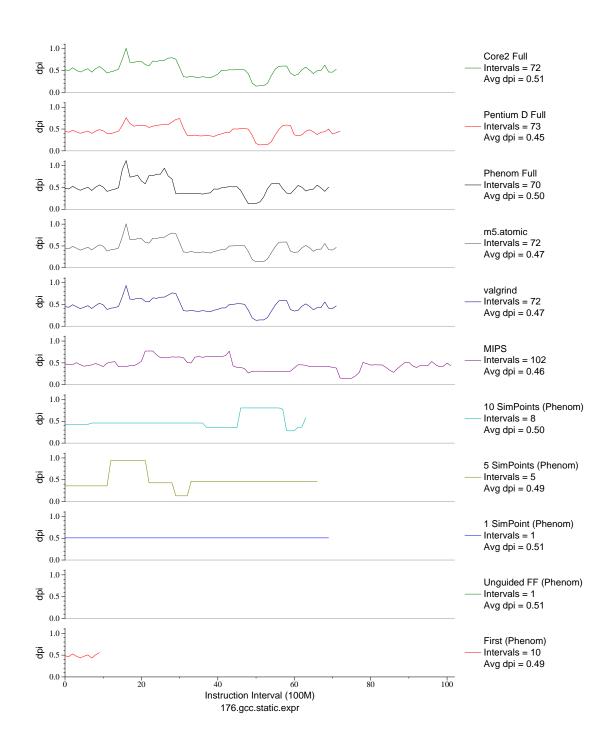

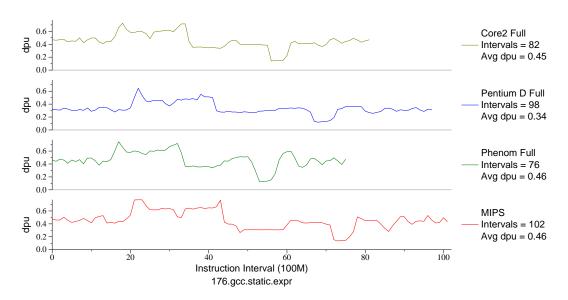

|      | CPI phase plot for gcc.expr (INT, C, C Compiler)              |     |

| E.63 | CPI phase plot for gcc.int (INT, C, C Compiler)               | 228 |

| E.64 | CPI phase plot for gcc.sci (INT, C, C Compiler)               | 229 |

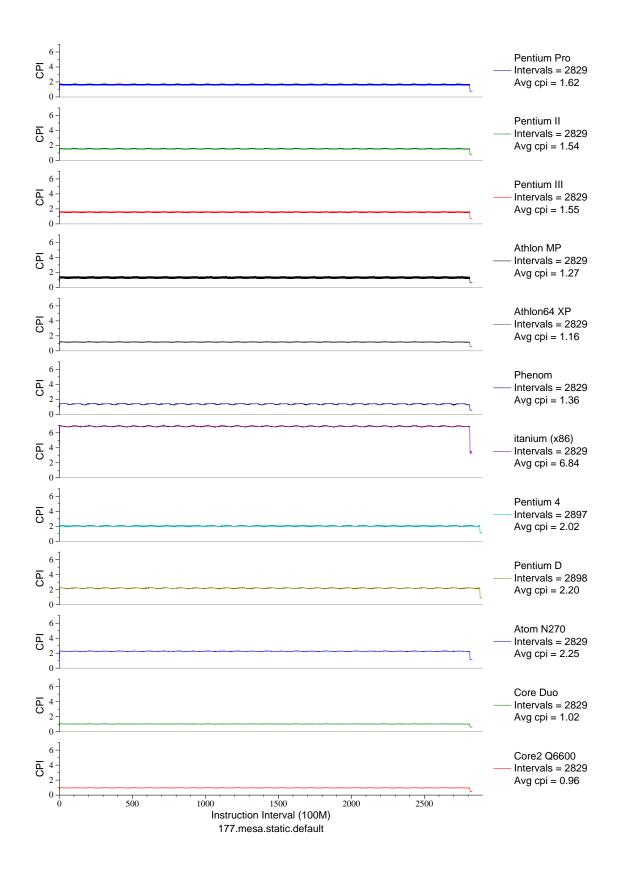

| E.65 | CPI phase plot for mesa (FP, C, 3D-graphics)                  | 230 |

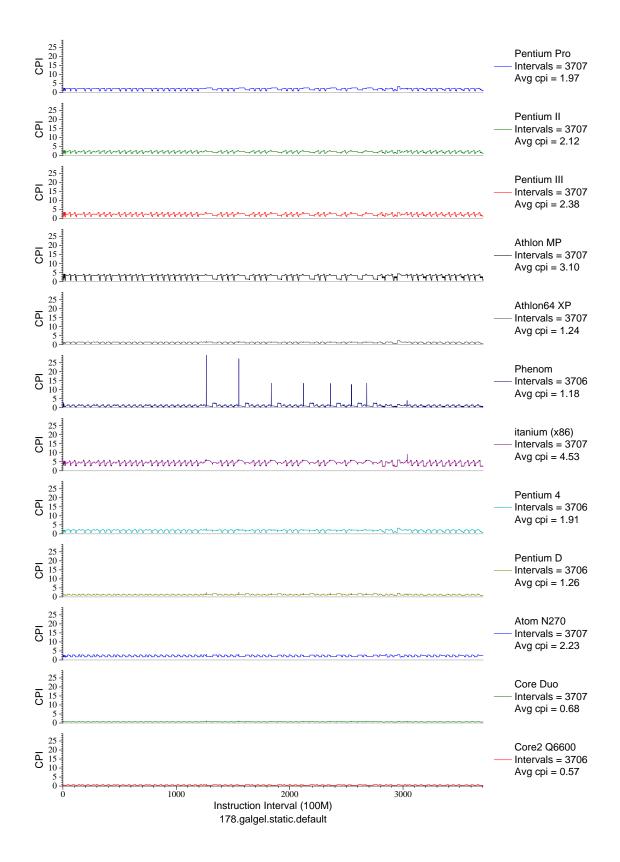

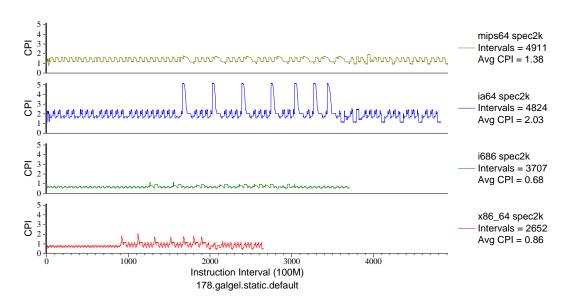

| E.66 | CPI phase plot for galgel (FP, F90, Fluid Dynamics)           | 231 |

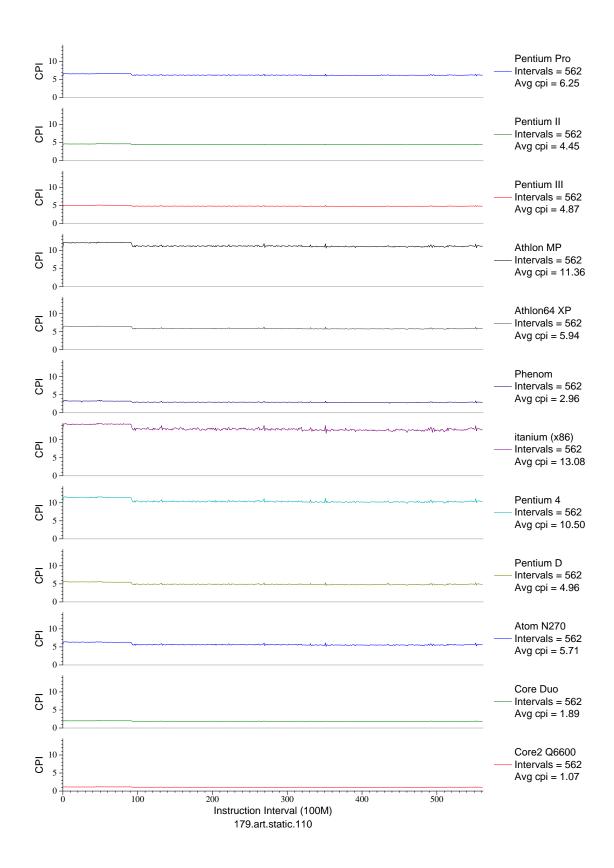

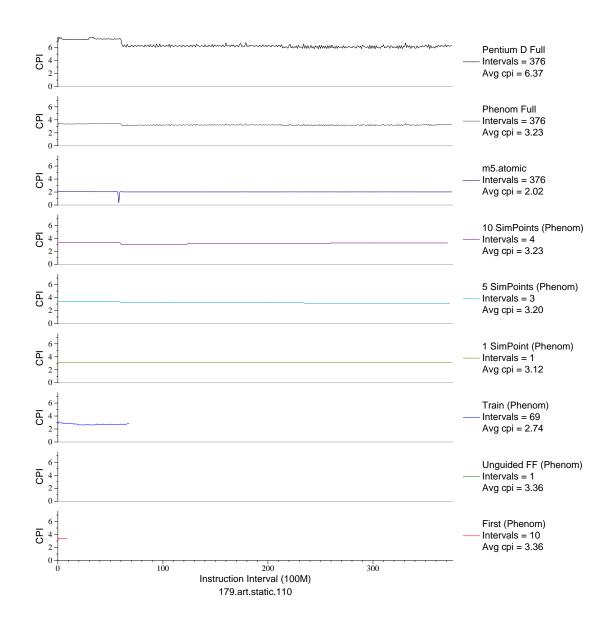

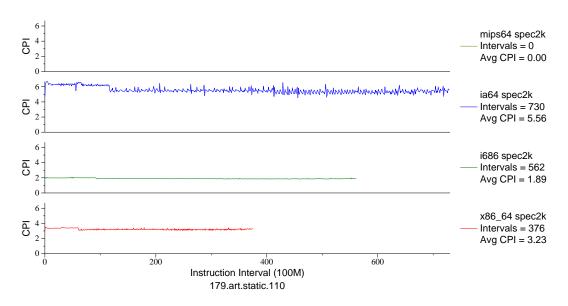

| E.67 | CPI phase plot for art.110 (FP, C, Neural Networks)           | 232 |

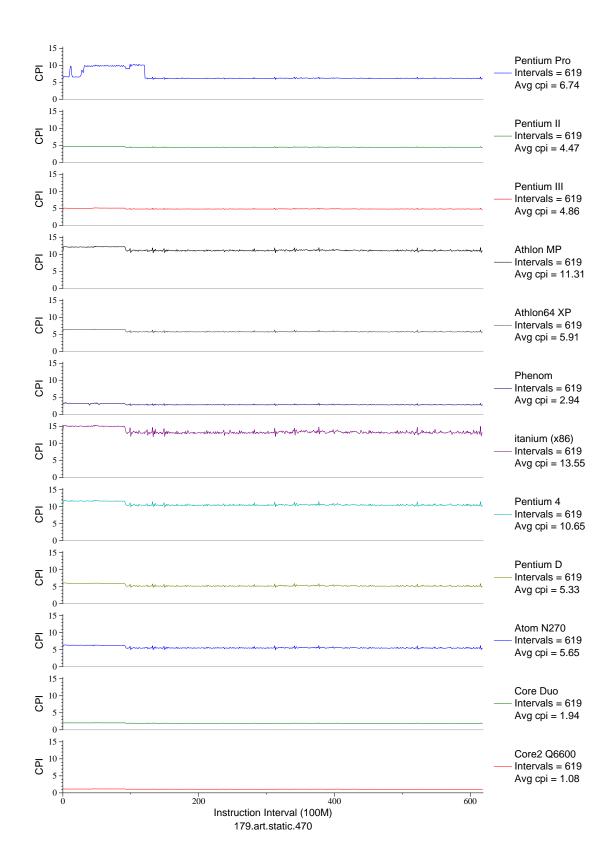

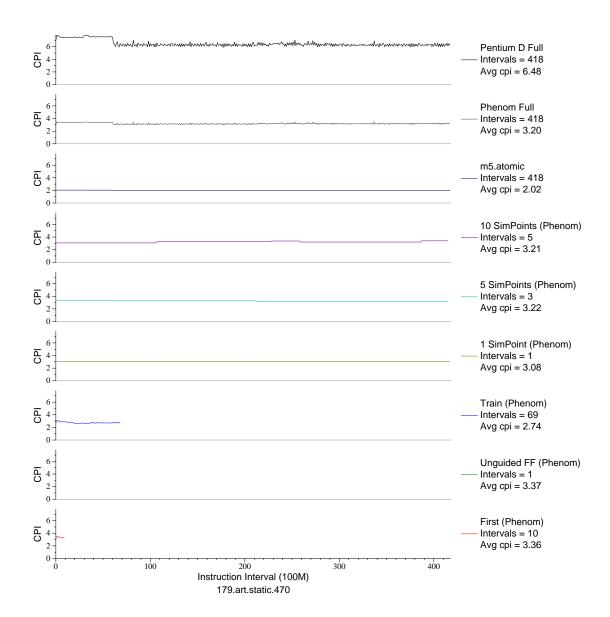

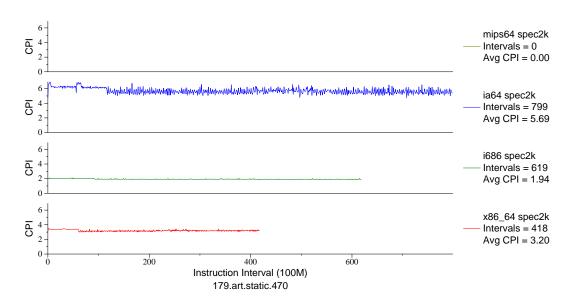

| E.68 | CPI phase plot for art. 470 (FP, C, Neural Networks)          | 233 |

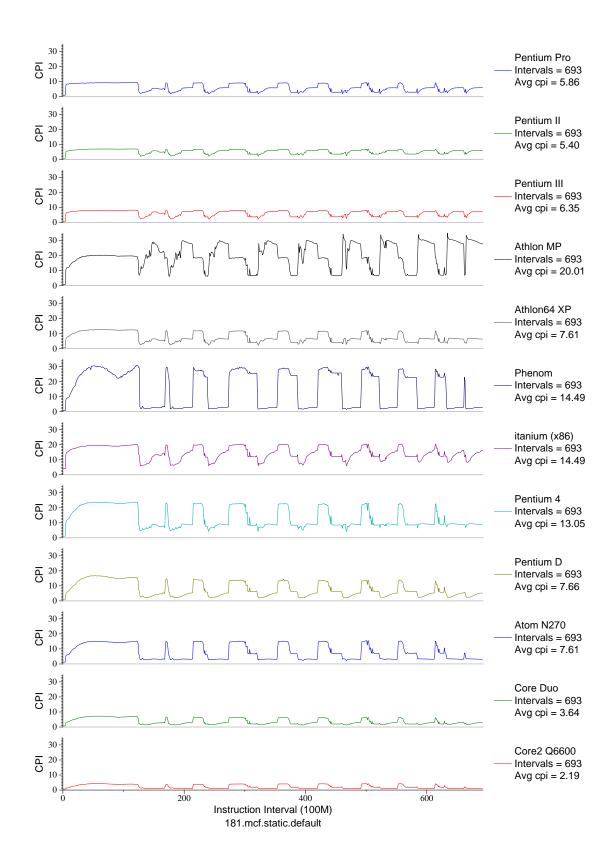

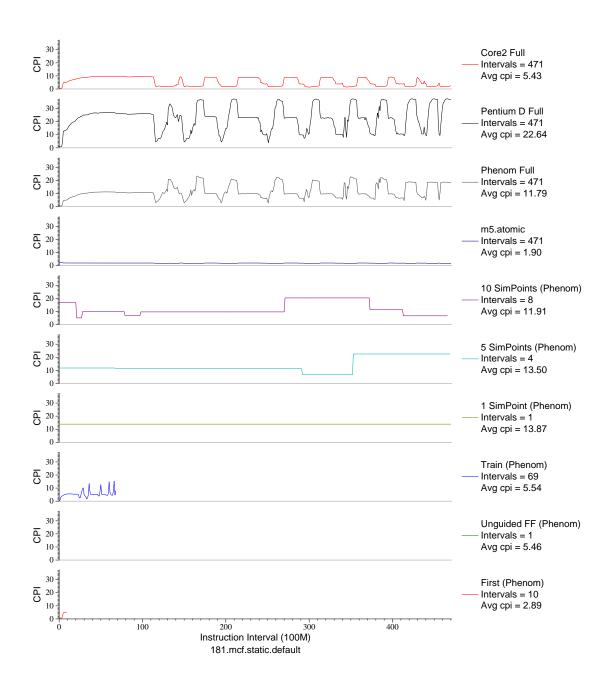

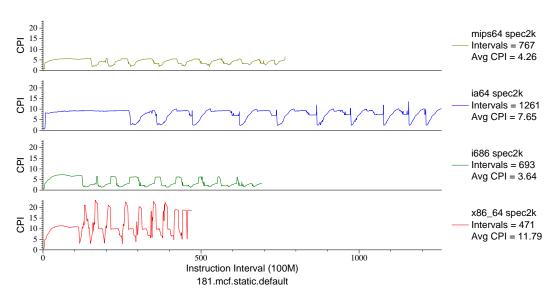

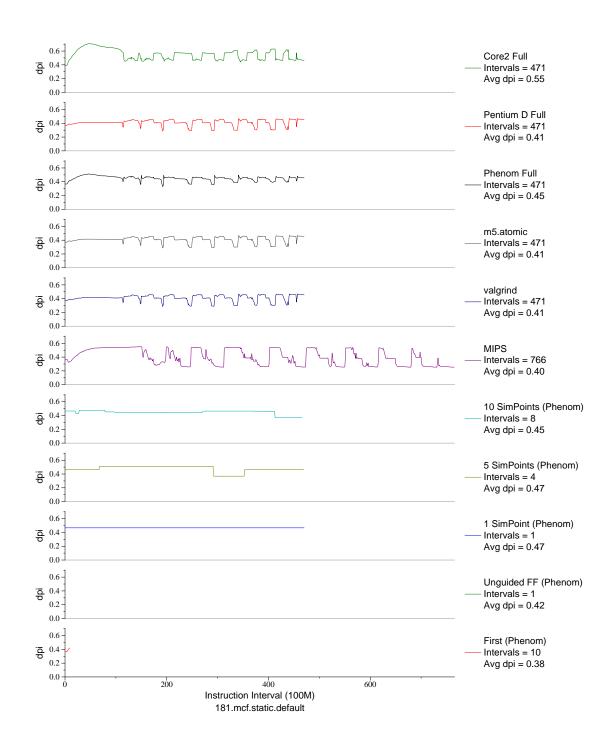

| E.69 | CPI phase plot for mcf (INT, C, Combinatorial Opt)            | 234 |

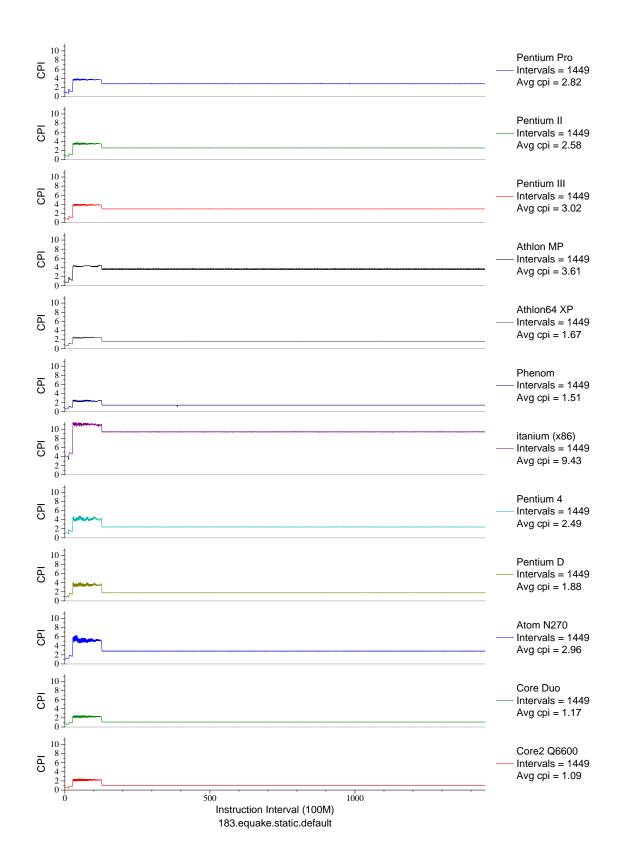

| E.70 | CPI phase plot for equake (FP, C, Seismic Propogation)        | 235 |

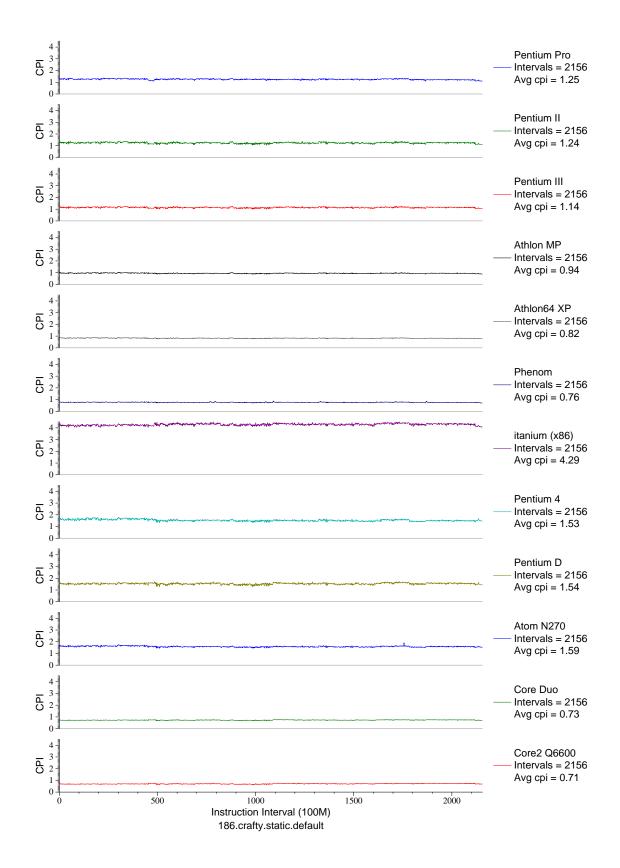

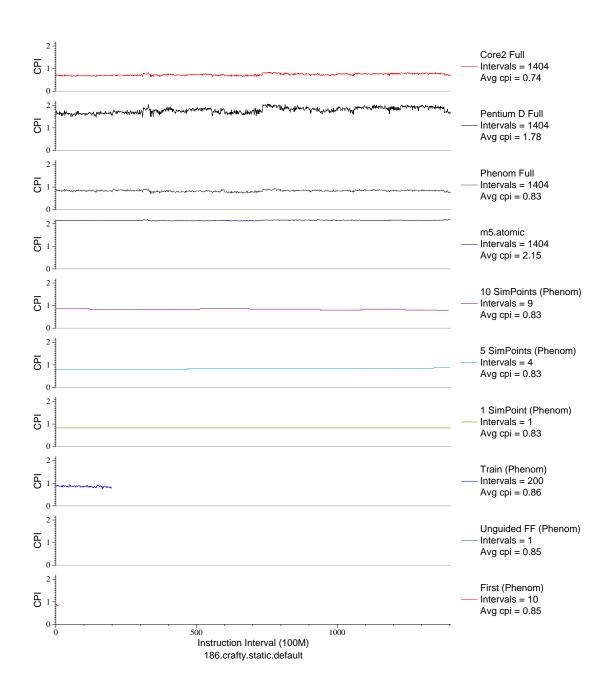

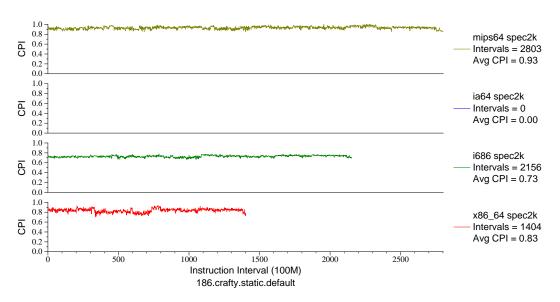

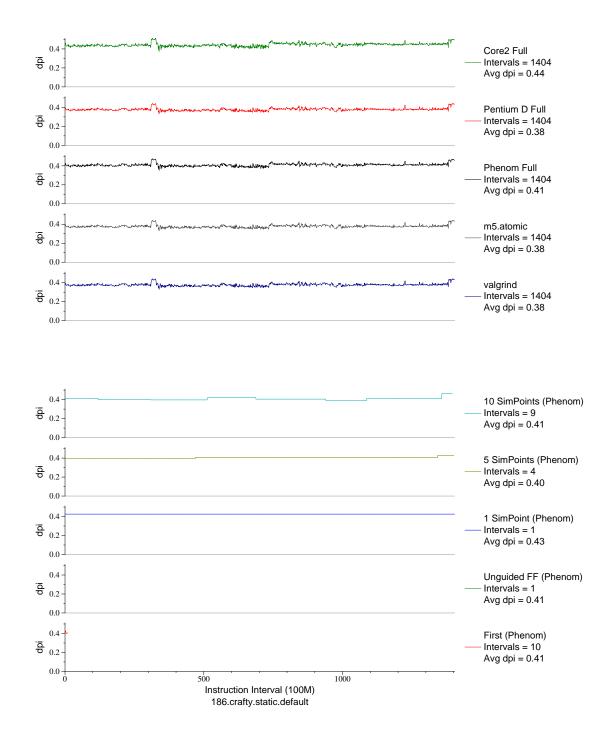

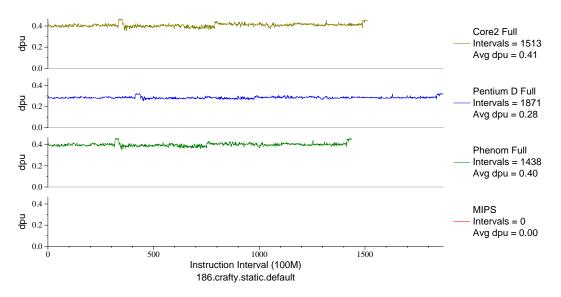

| E.71 | CPI phase plot for crafty (INT, C, Chess)                     | 236 |

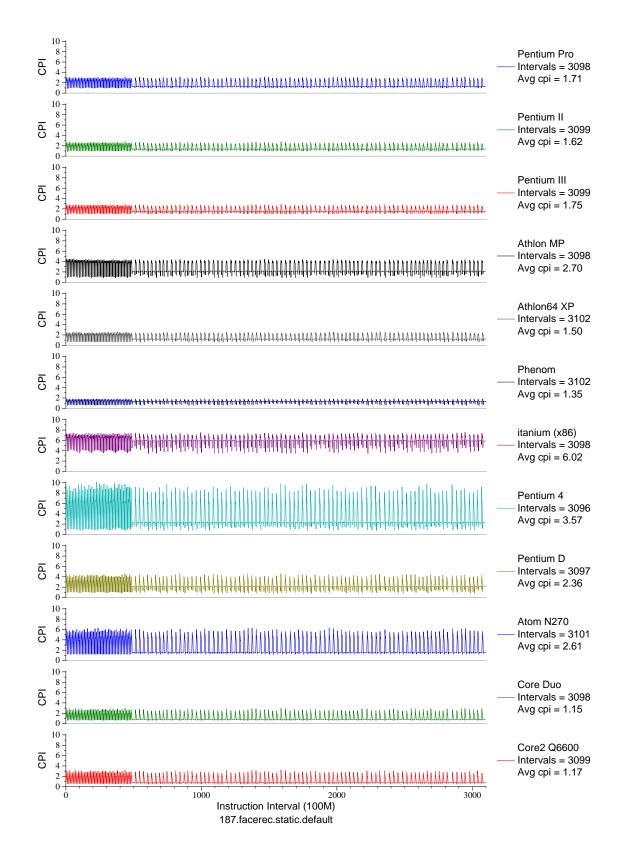

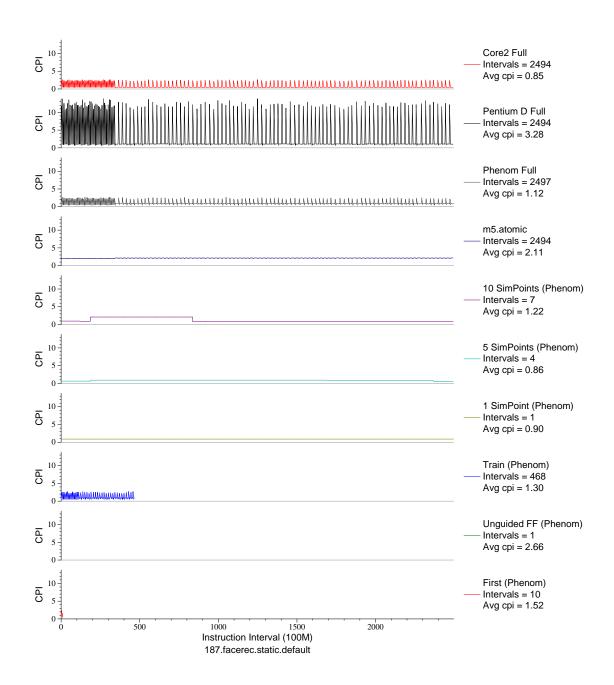

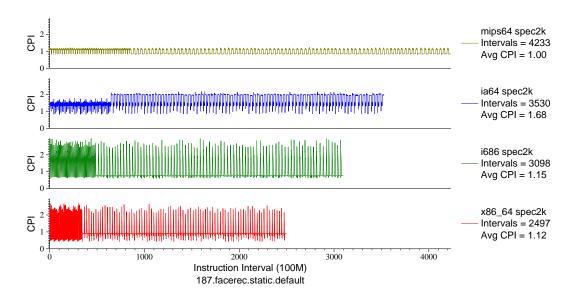

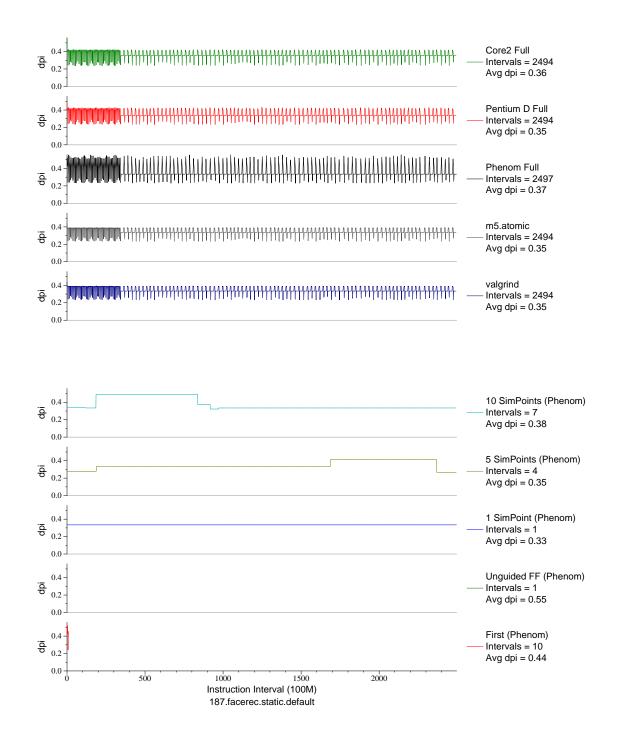

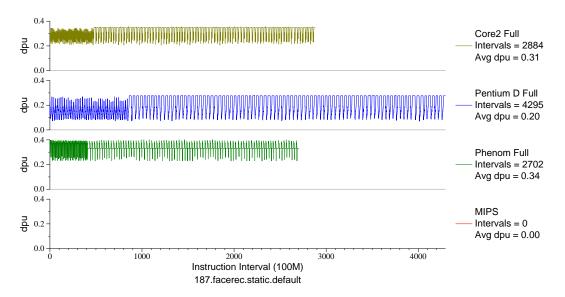

| E.72 | CPI phase plot for facerec (FP, F90, Facial Recognition)      | 237 |

|------|---------------------------------------------------------------|-----|

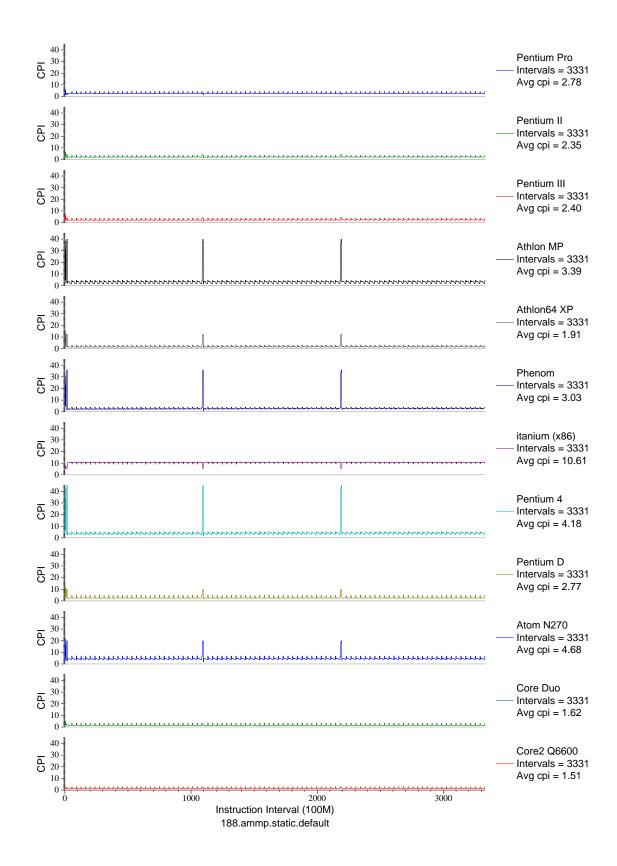

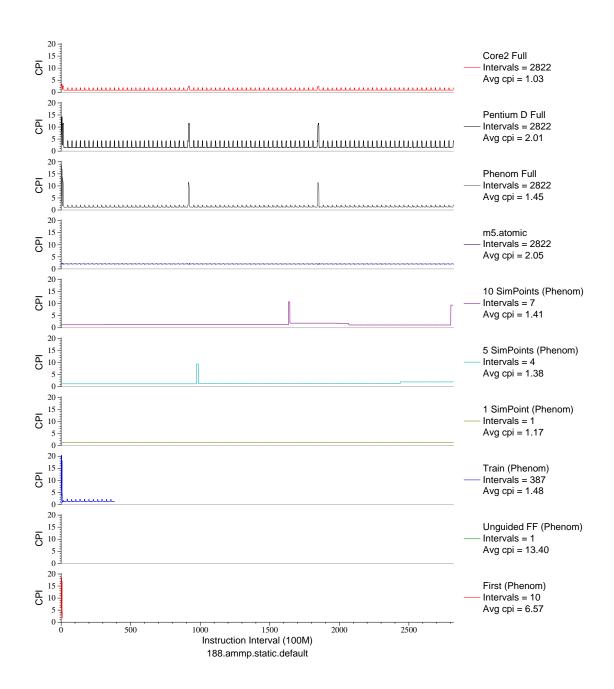

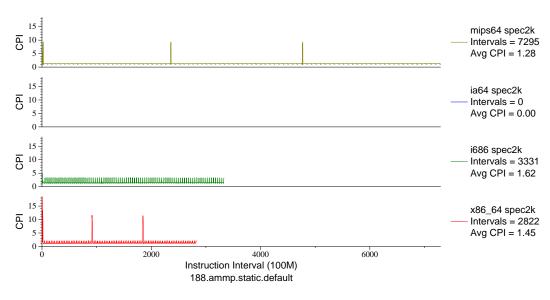

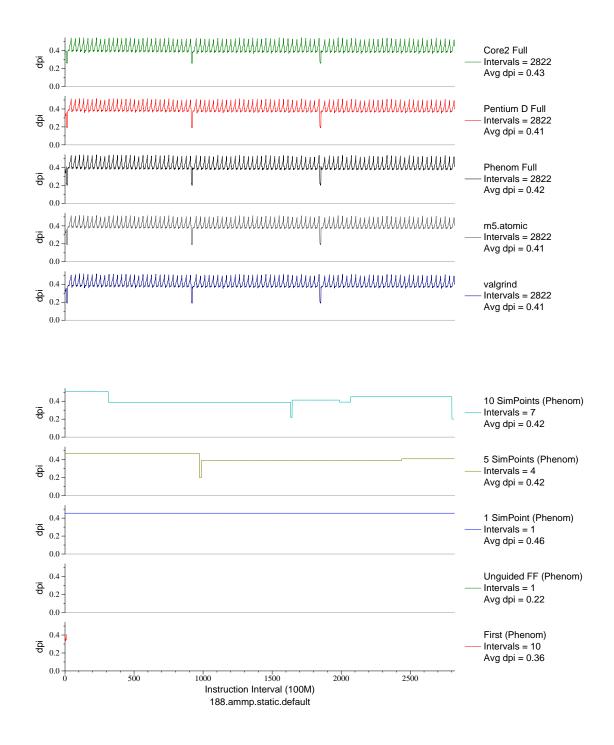

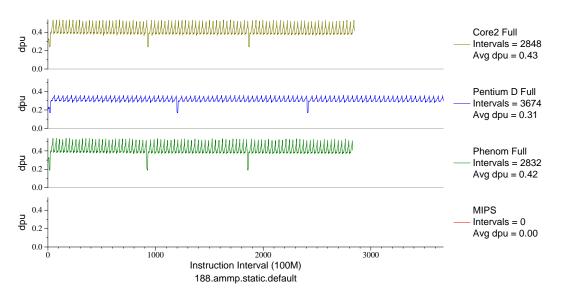

| E.73 | CPI phase plot for ammp (FP, C, Chemistry)                    | 238 |

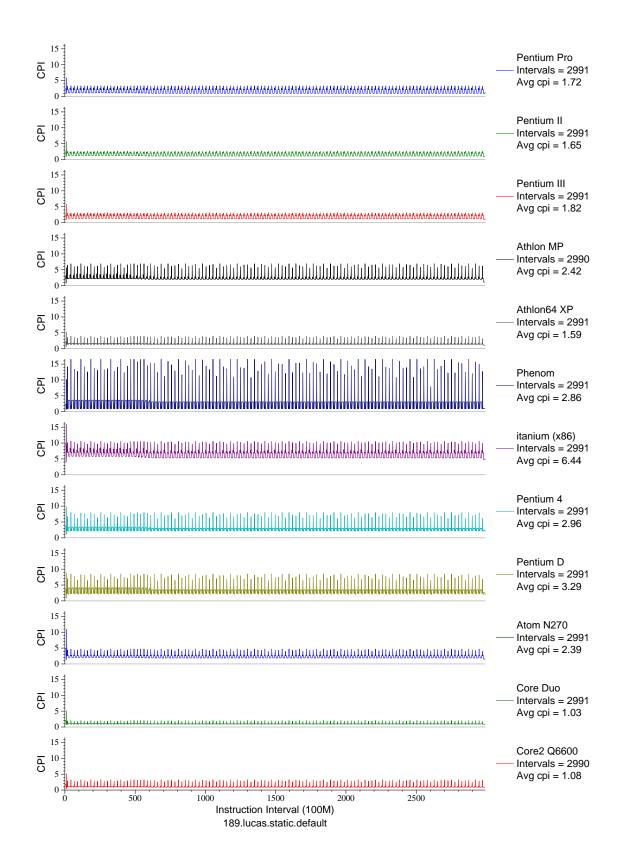

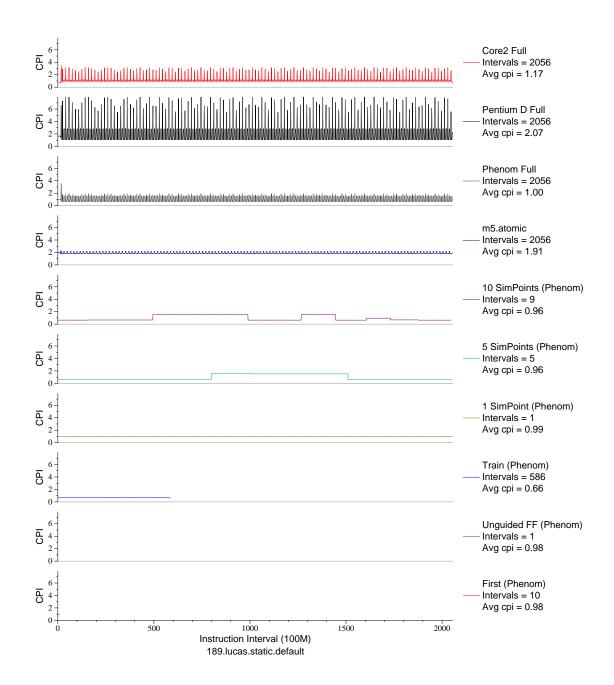

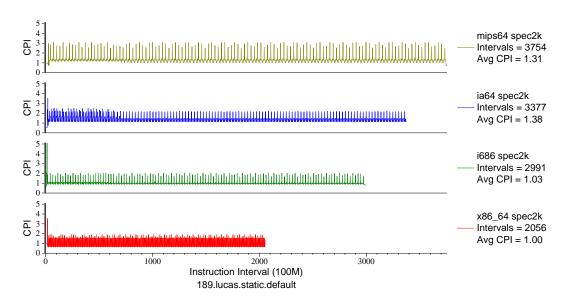

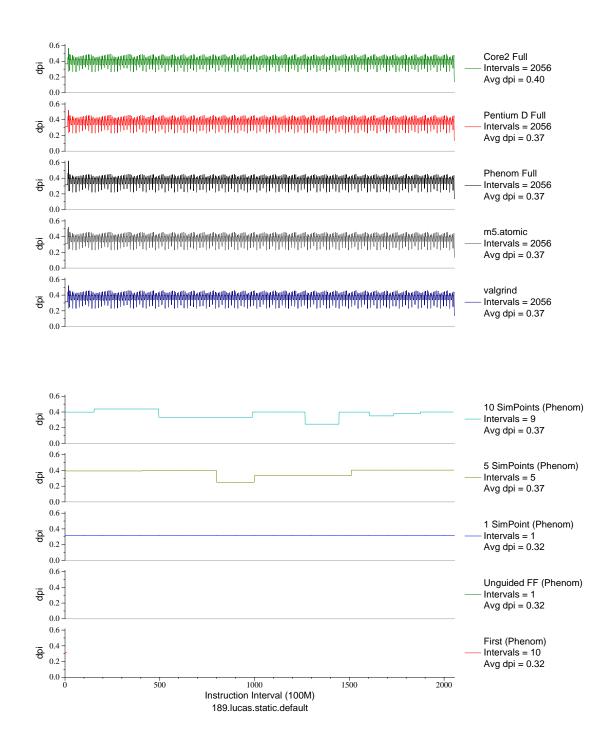

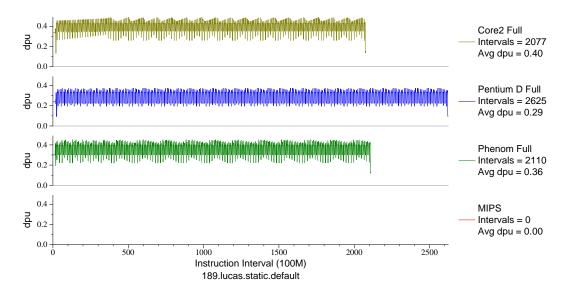

| E.74 | CPI phase plot for lucas (FP, F90, Number Theory)             | 239 |

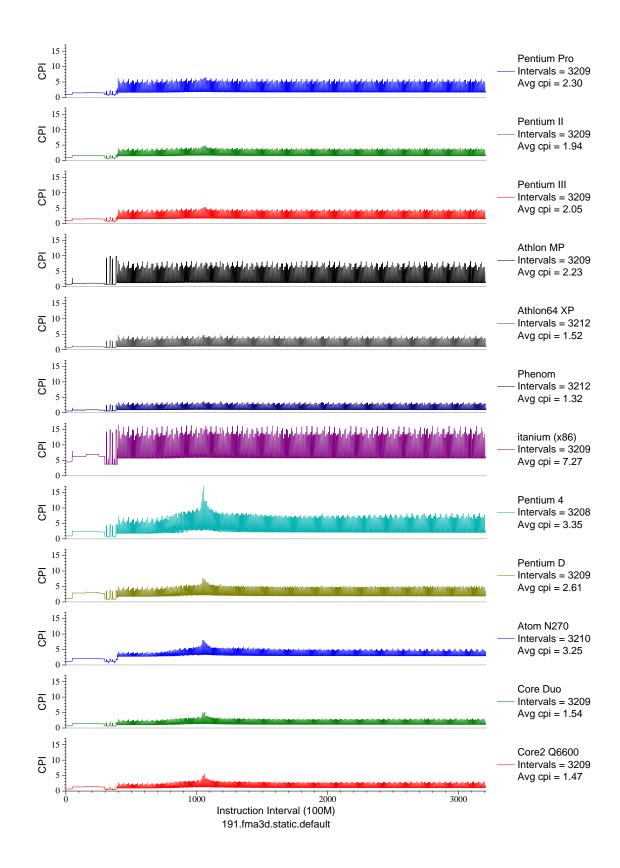

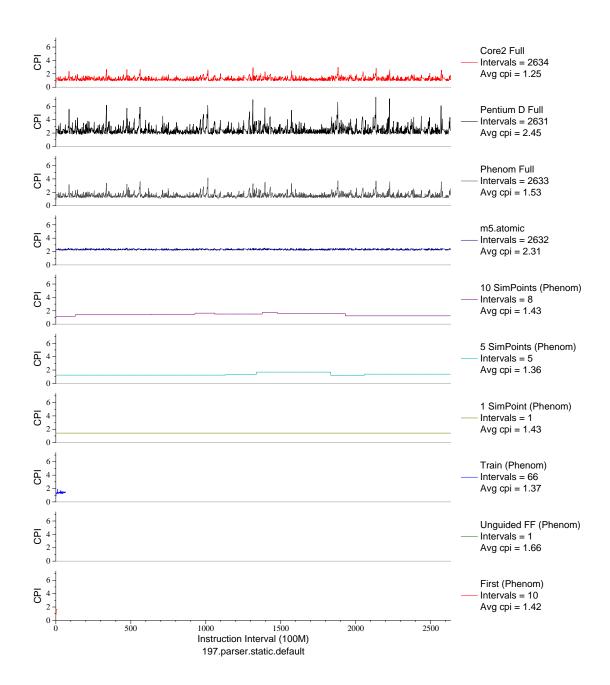

| E.75 | CPI phase plot for fma3d (FP, F90, Crash Simulation)          | 240 |

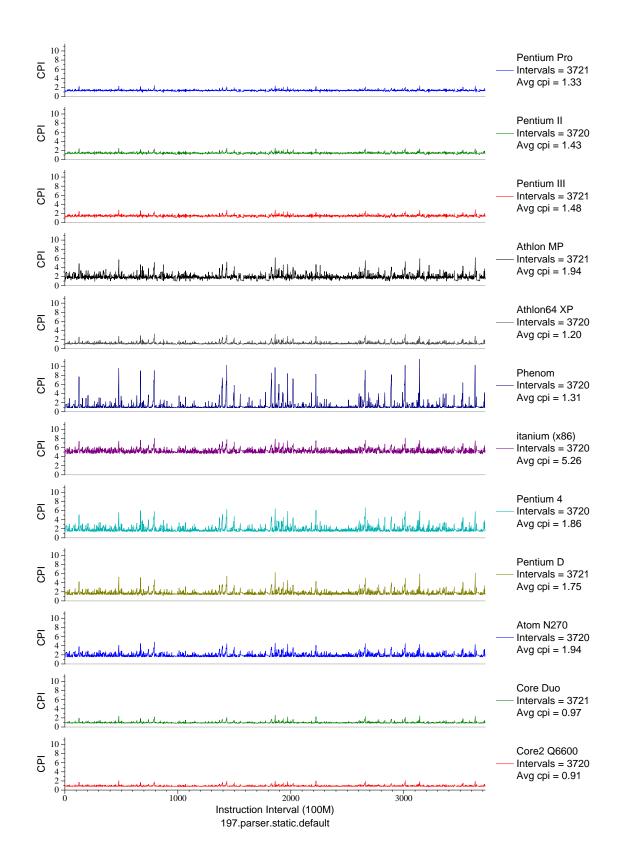

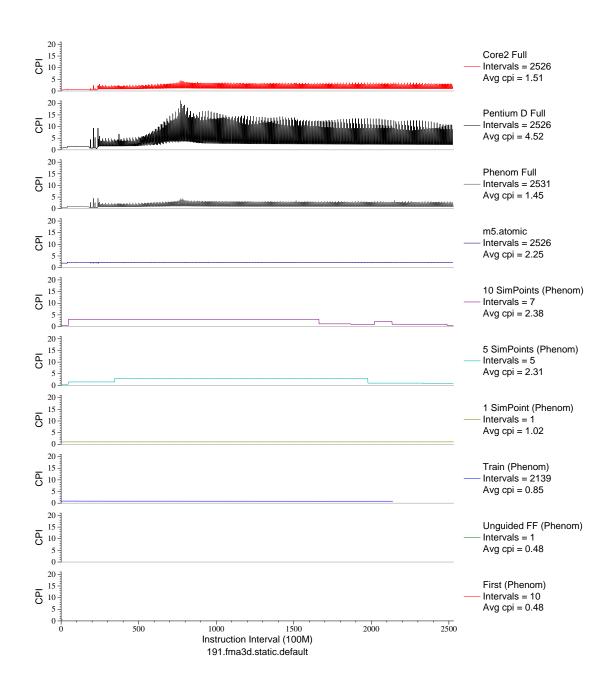

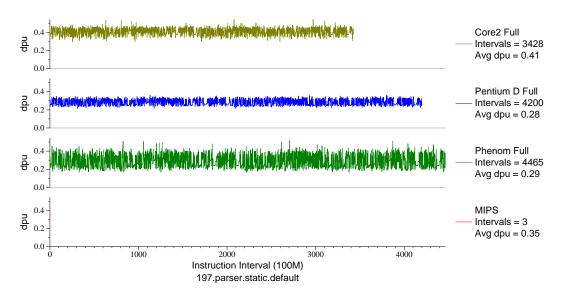

| E.76 | CPI phase plot for parser (INT, C, Word Processing)           | 241 |

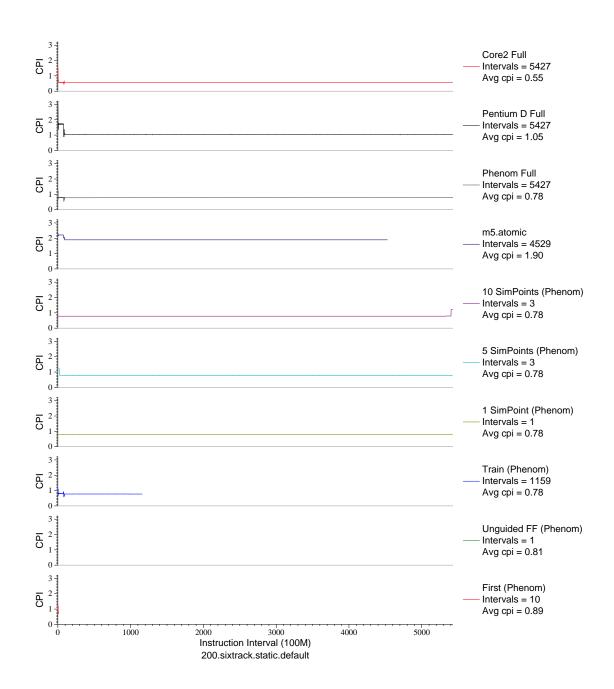

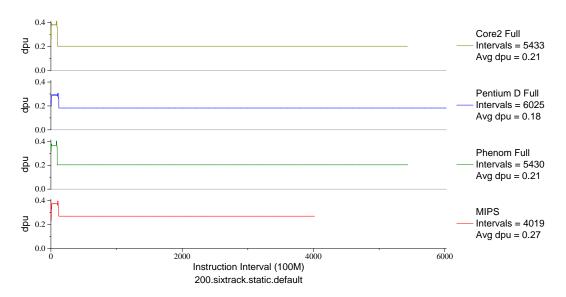

| E.77 | CPI phase plot for sixtrack (FP, F77, Nuclear Physics)        | 242 |

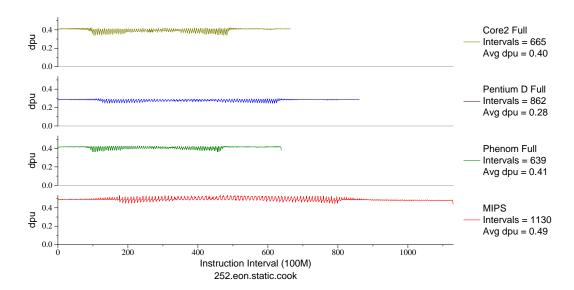

| E.78 | CPI phase plot for eon.cook (INT, C++, Computer Graphics) .   | 243 |

| E.79 | CPI phase plot for eon.kaj (INT, C++, Computer Graphics)      | 244 |

| E.80 | CPI phase plot for eon.rush (INT, C++, Computer Graphics) .   | 245 |

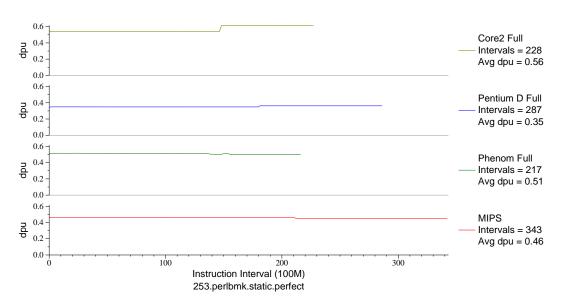

| E.81 | CPI phase plot for perlbmk.mkrnd (INT, C, Scripting Language) | 246 |

| E.82 | CPI phase plot for perlbmk.perf (INT, C, Scripting Language)  | 247 |

| E.83 | CPI phase plot for gap (INT, C, Group Theory)                 | 248 |

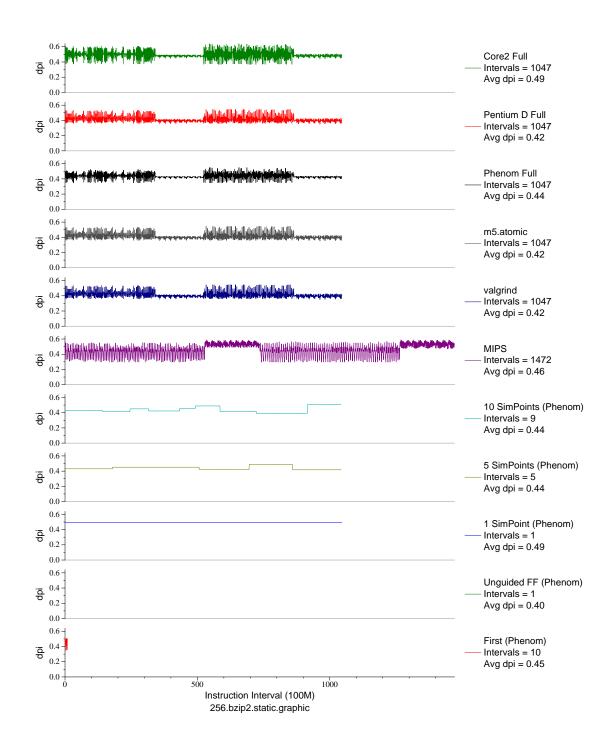

| E.84 | CPI phase plot for bzip2.graph (INT, C, Compression)          | 249 |

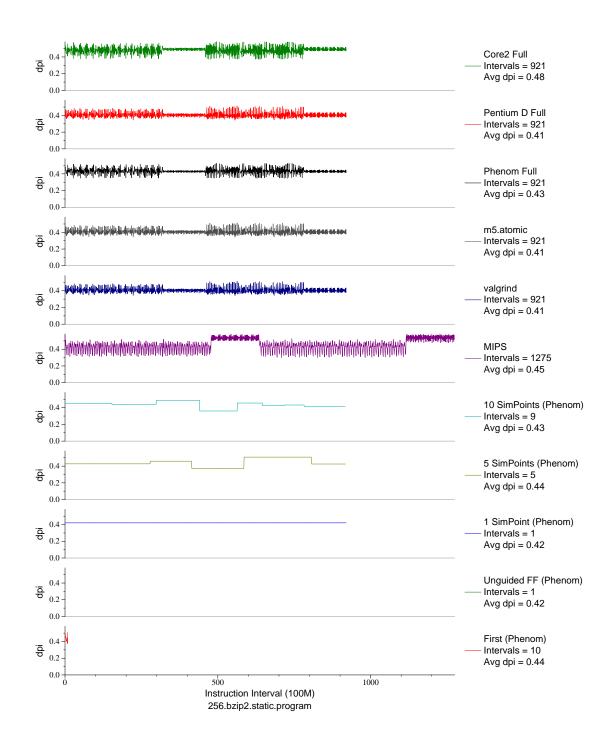

| E.85 | CPI phase plot for bzip2.prog (INT, C, Compression)           | 250 |

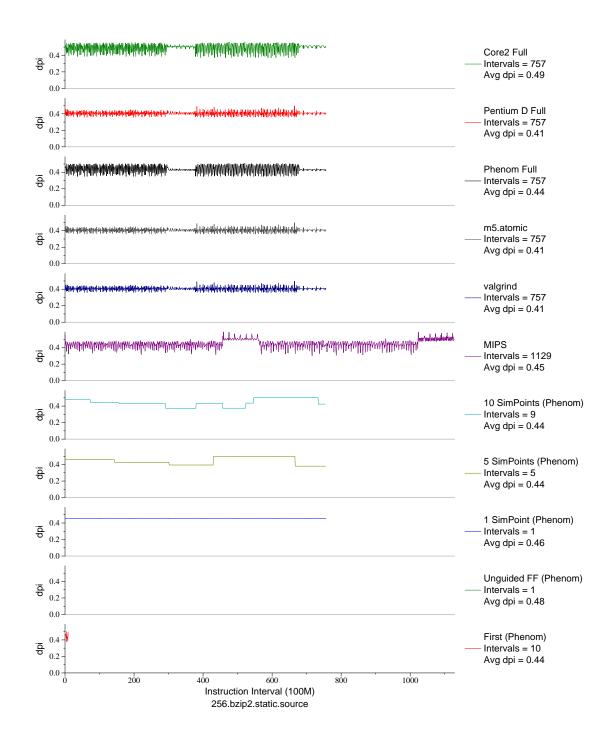

| E.86 | CPI phase plot for bzip2.src (INT, C, Compression)            | 251 |

| E.87 | CPI phase plot for twolf (INT, C, Place/Route)                | 252 |

| E.88 | CPI phase plot for apsi (FP, F77, Meteorology/Pollution)      | 253 |

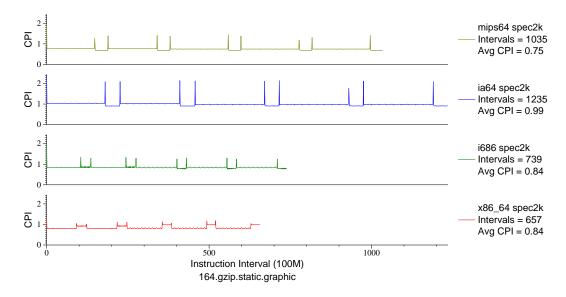

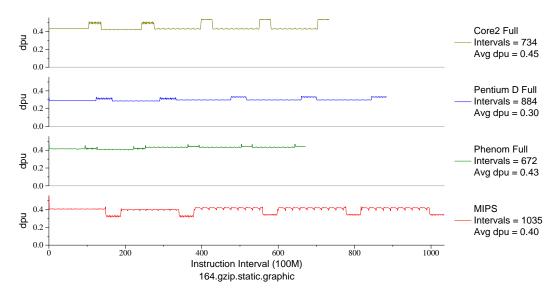

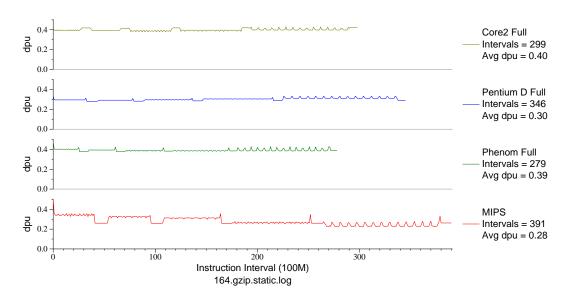

| F.1  | Multi-arch CPI plot for gzip.graph (INT, C, Compression)      | 254 |

| F.2  | Multi-arch CPI plot for gzip.log (INT, C, Compression)        | 255 |

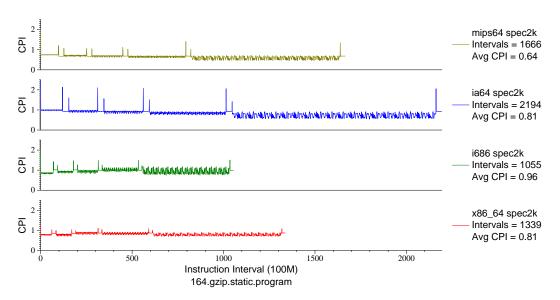

| F.3  | Multi-arch CPI plot for gzip.prog (INT, C, Compression)       | 255 |

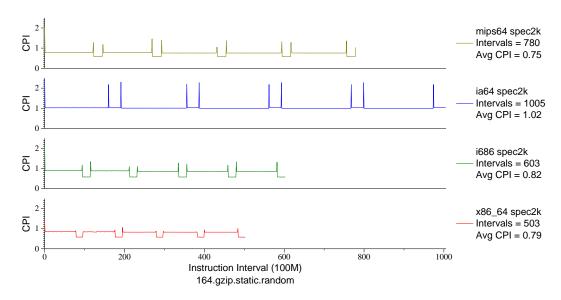

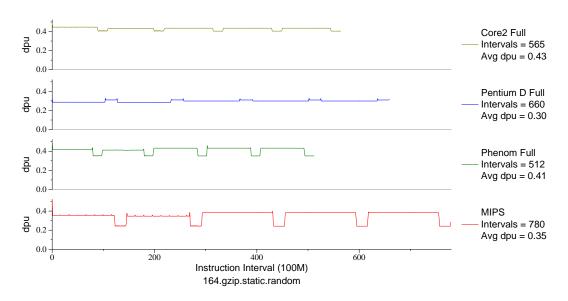

| F.4  | Multi-arch CPI plot for gzip.rand (INT, C, Compression)       | 256 |

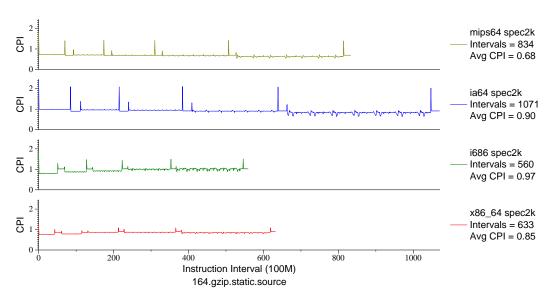

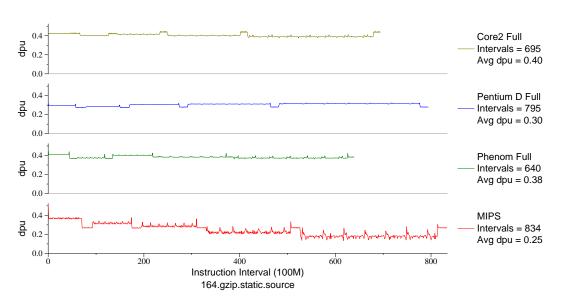

| F.5  | Multi-arch CPI plot for gzip.src (INT, C, Compression)        | 256 |

| F.6  | Multi-arch CPI plot for wupwise (FP, F77, Quantum Chromody-   |     |

|      | namics)                                                       | 257 |

| F.7  | Multi-arch CPI plot for swim (FP, F77, Meteorology/Water)     | 257 |

| F.8  | Multi-arch CPI plot for mgrid (FP, F77, Multi-Grid Solver)    | 258 |

| F.9  | Multi-arch CPI plot for applu (FP, F77, Fluid Dynamics)       | 258 |

| F.10 | Multi-arch CPI plot for vpr.place (INT, C, FPGA Place/Route)  | 259 |

| F.11 | Multi-arch CPI plot for vpr.route (INT, C, FPGA Place/Route)  | 259 |

| F.12 | Multi-arch CPI plot for gcc.166 (INT, C, C Compiler)          | 260 |

| F.13 | Multi-arch CPI plot for gcc. 200 (INT, C, C Compiler)         | 260 |

| F.14 | Multi-arch CPI plot for gcc.expr (INT, C, C Compiler)         | 261 |

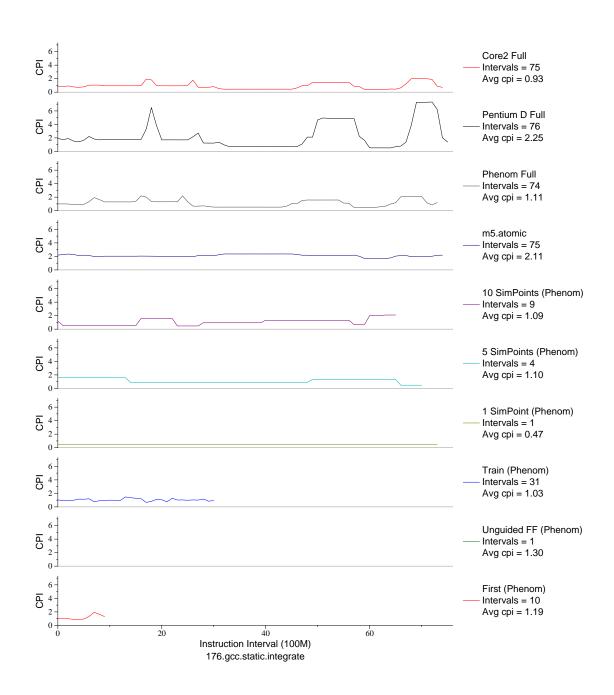

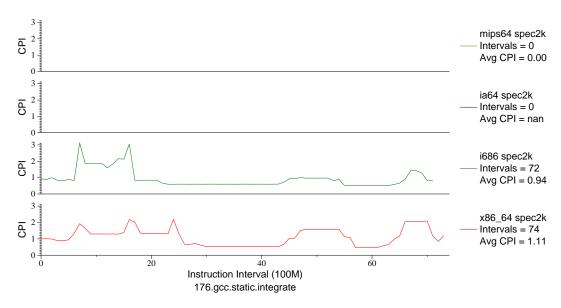

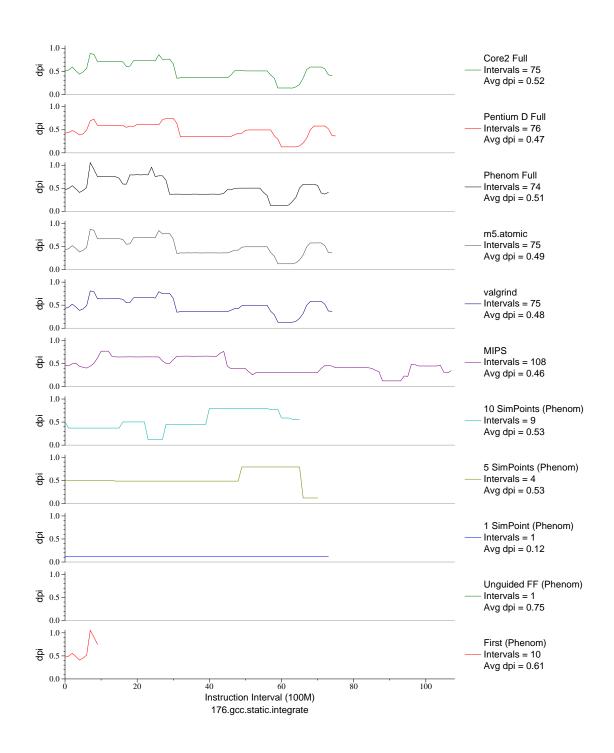

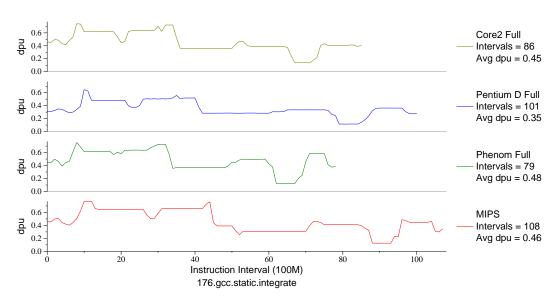

| F.15 | Multi-arch CPI plot for gcc.integrate (INT, C, C Compiler) .  | 261 |

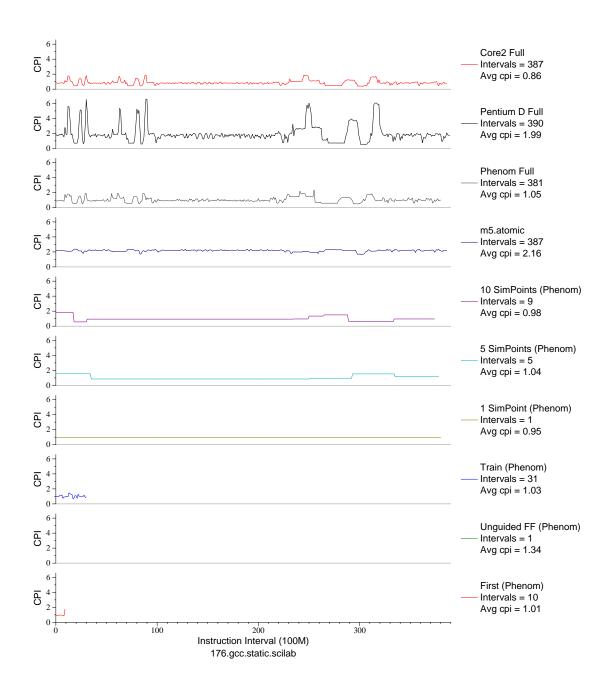

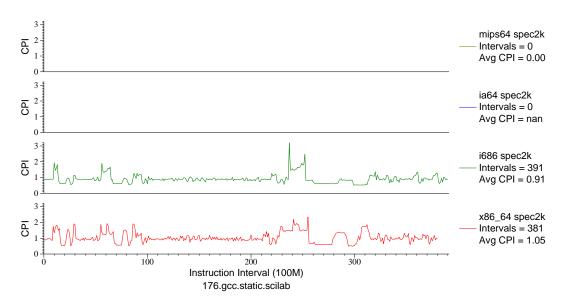

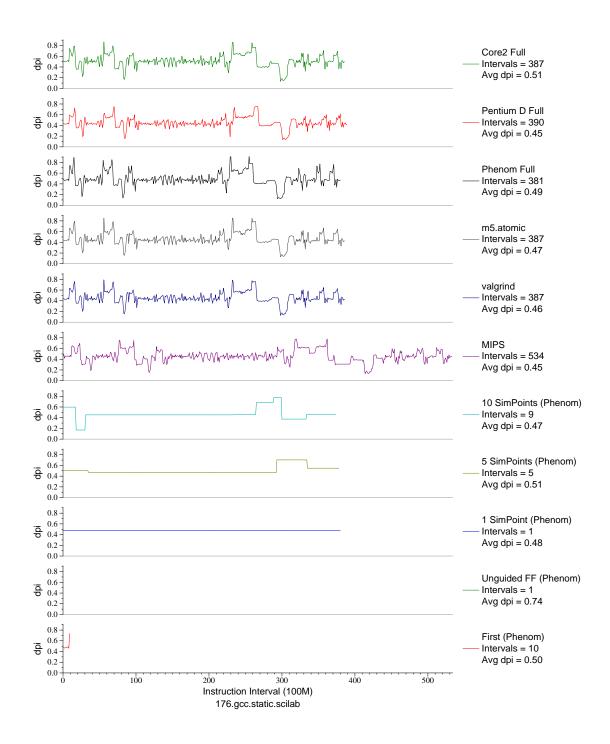

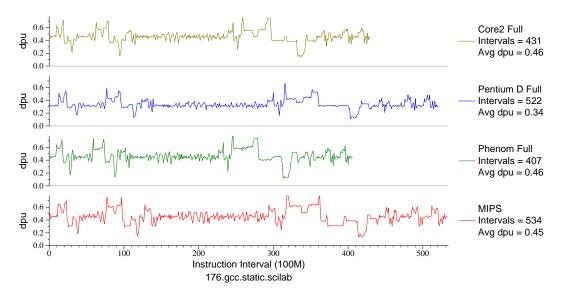

| F.16 | Multi-arch CPI plot for gcc.scilab (INT, C, C Compiler)       | 262 |

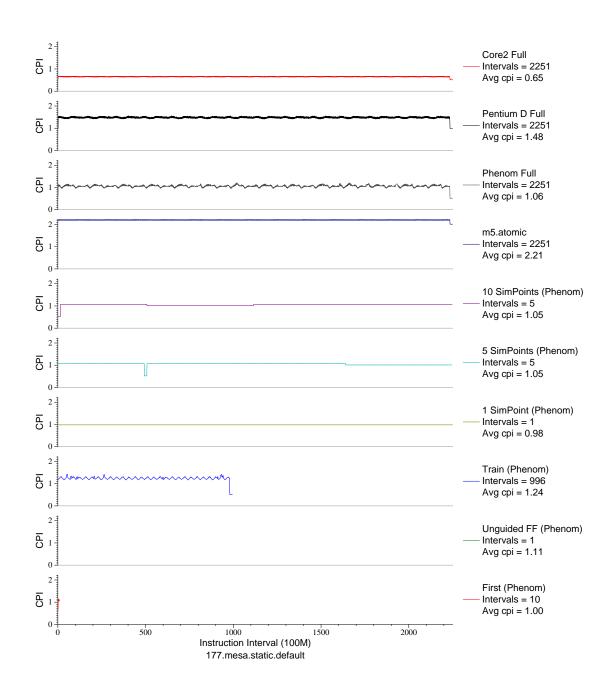

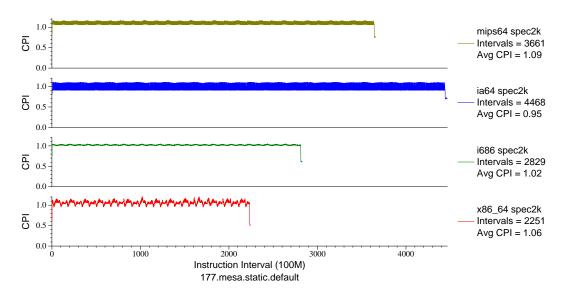

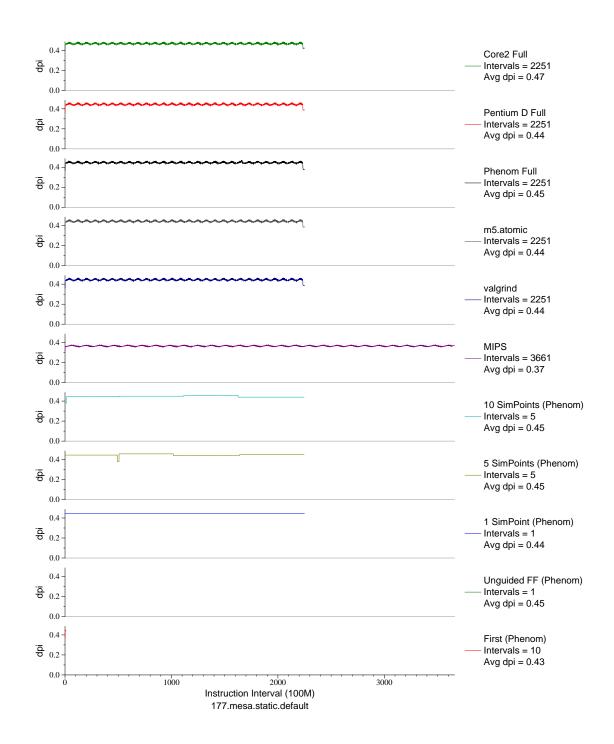

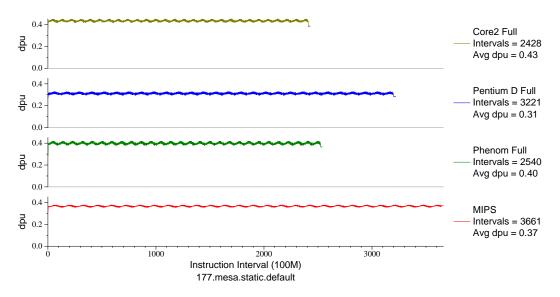

| F.17 | Multi-arch CPI plot for mesa (FP, C, 3D-graphics)             | 262 |

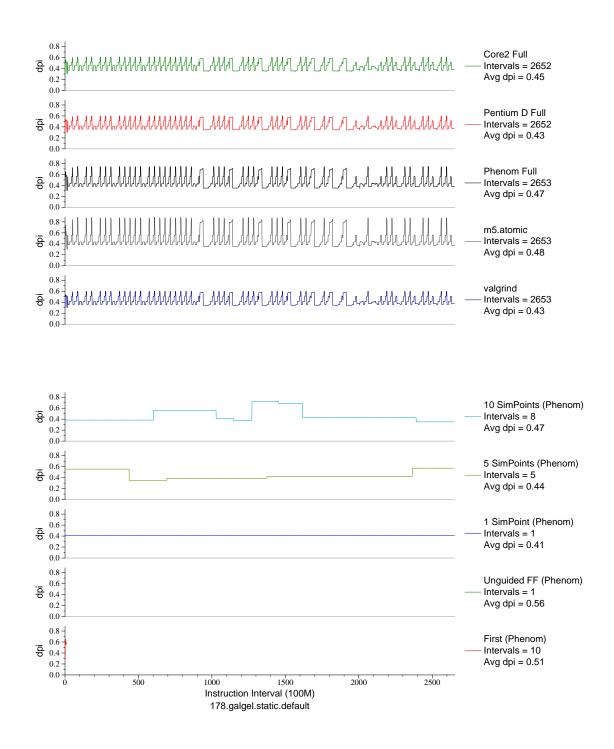

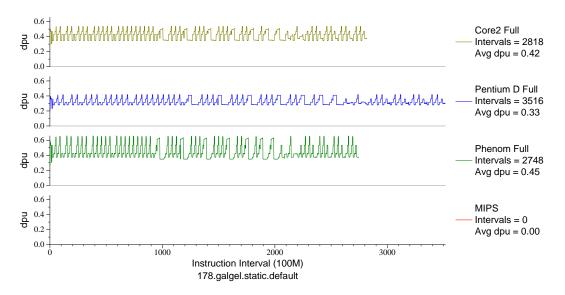

| F.18 | Multi-arch CPI plot for galgel (FP, F90, Fluid Dynamics)      | 263 |

| F.19 | Multi-arch CPI plot for art.110 (FP, C, Neural Networks)      | 263 |

| F.20 | Multi-arch CPI plot for art. 470 (FP, C, Neural Networks)     | 264 |

| F.21 | Multi-arch CPI plot for mcf (INT, C, Combinatorial Opt)       |     |

| F.22 | Multi-arch CPI plot for equake (FP, C, Seismic Propogation)   |     |

| F.23 | Multi-arch CPI plot for crafty (INT, C, Chess)                |     |

| F.24 | Multi-arch CPI plot for facerec (FP, F90, Facial Recognition) |     |

| F.25 | Multi-arch CPI plot for ammp (FP, C, Chemistry)               |     |

| F.26 | Multi-arch CPI plot for lucas (FP, F90, Number Theory)          | 267         |

|------|-----------------------------------------------------------------|-------------|

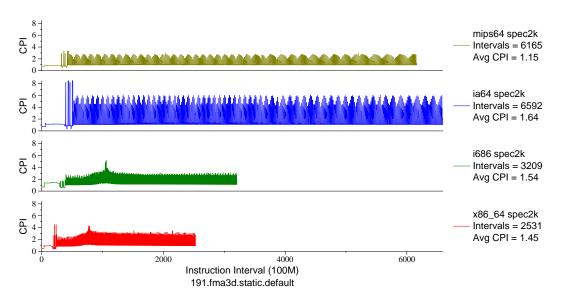

| F.27 | Multi-arch CPI plot for fma3d (FP, F90, Crash Simulation)       | 267         |

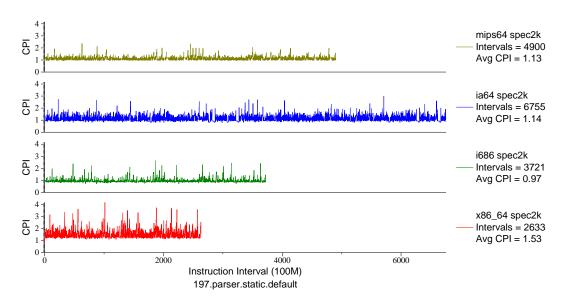

| F.28 | Multi-arch CPI plot for parser (INT, C, Word Processing)        | 268         |

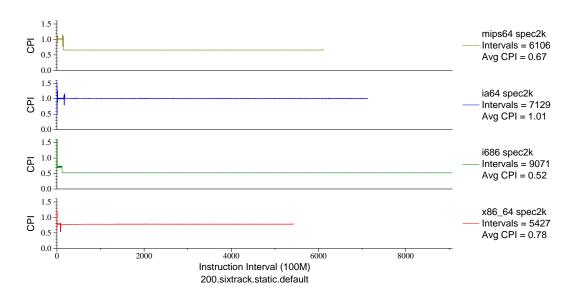

| F.29 | Multi-arch CPI plot for sixtrack (FP, F77, Nuclear Physics)     | 268         |

| F.30 | Multi-arch CPI plot for eon.cook (INT, C++, Computer Graphics   | )269        |

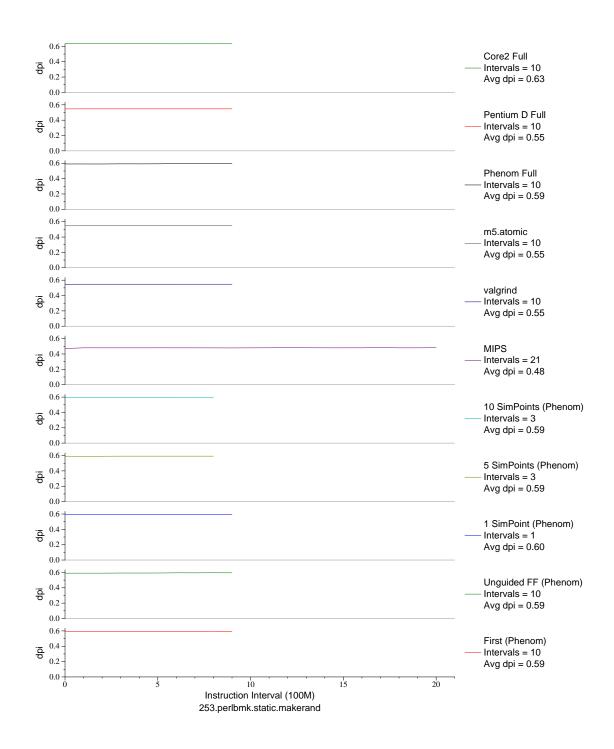

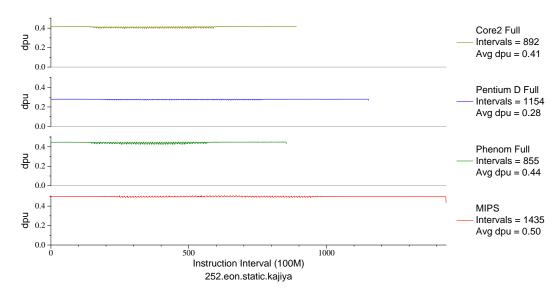

| F.31 | Multi-arch CPI plot for eon.kajiya (INT, C++, Computer          |             |

|      | Graphics)                                                       | 269         |

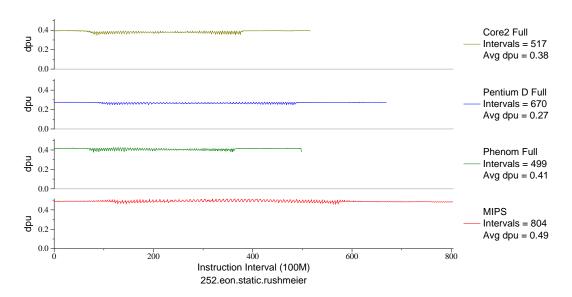

| F.32 | Multi-arch CPI plot for eon.rushmeier (INT, C++, Computer       |             |

|      | Graphics)                                                       | 270         |

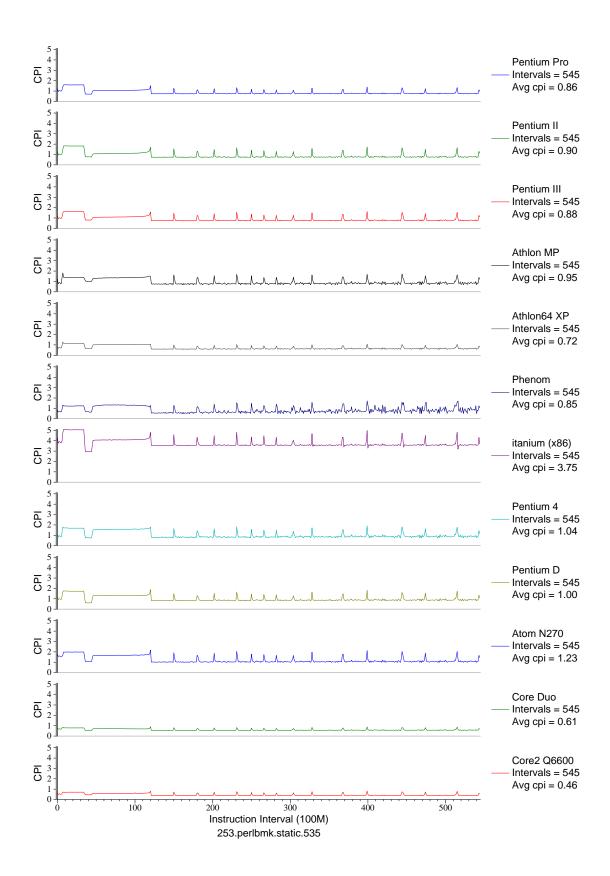

| F.33 | Multi-arch CPI plot for perlbmk.535 (INT, C, Scripting Lan-     |             |

|      | guage)                                                          | 270         |

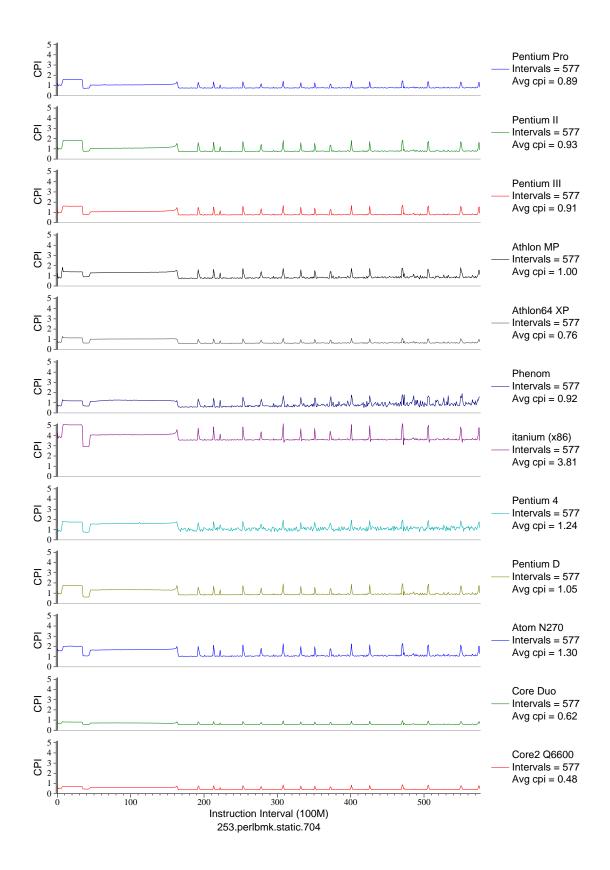

| F.34 | Multi-arch CPI plot for perlbmk.704 (INT, C, Scripting Lan-     |             |

|      | guage)                                                          | 271         |

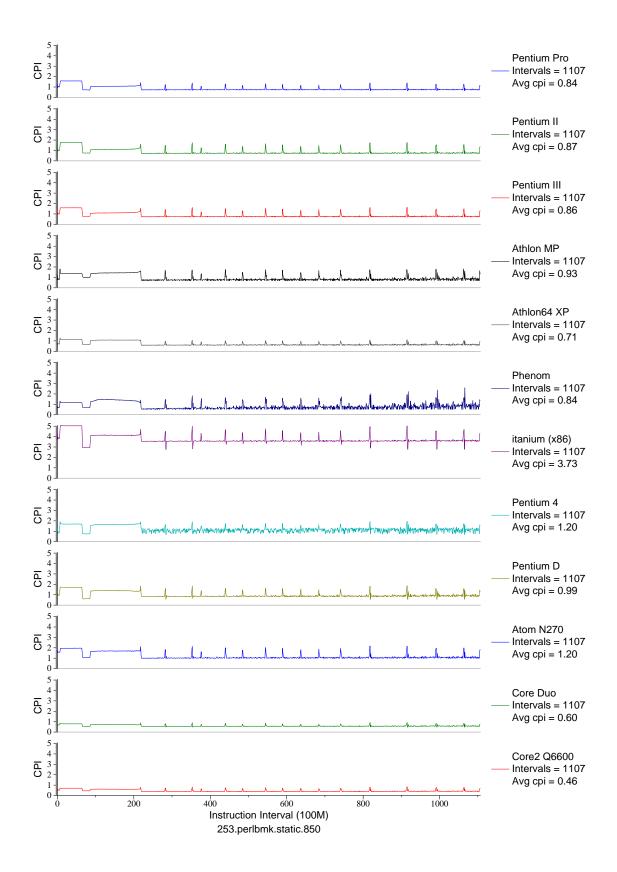

| F.35 | Multi-arch CPI plot for perlbmk.850 (INT, C, Scripting Lan-     |             |

|      | guage)                                                          | 271         |

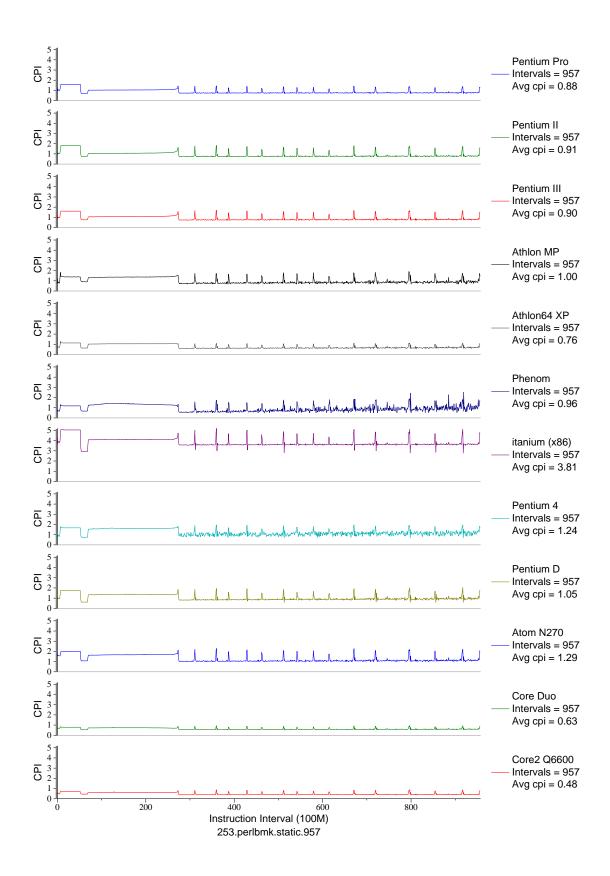

| F.36 | Multi-arch CPI plot for perlbmk.957 (INT, C, Scripting Lan-     |             |

|      | guage)                                                          | 272         |

| F.37 | Multi-arch CPI plot for perlbmk.diff (INT, C, Scripting Lan-    |             |

|      | guage)                                                          | 272         |

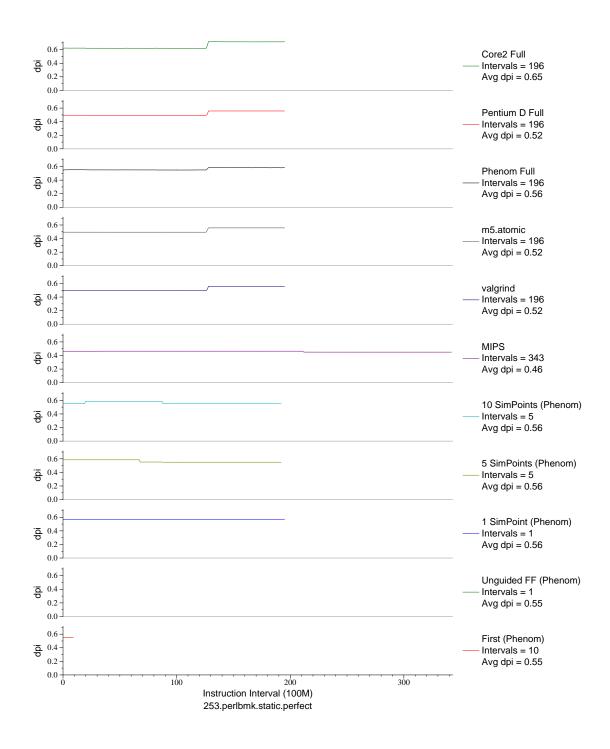

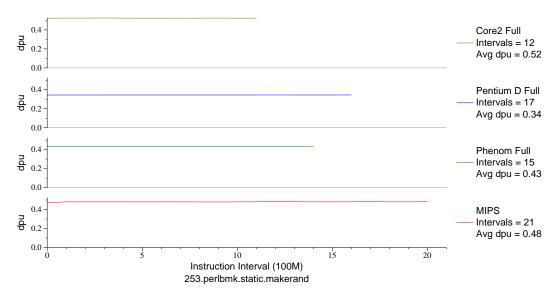

| F.38 | Multi-arch CPI plot for perlbmk.mkrnd(INT, C, Scripting)        |             |

| F.39 | Multi-arch CPI plot for perlbmk.perf (INT, C, Scripting)        | <b>27</b> 3 |

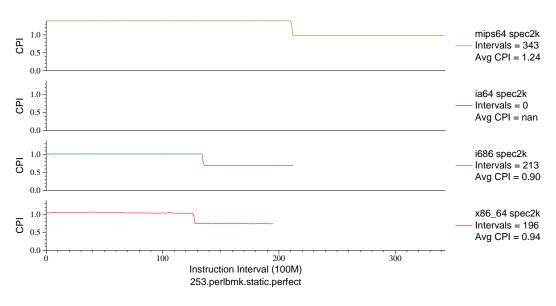

| F.40 | Multi-arch CPI plot for gap (INT, C, Group Theory)              | 274         |

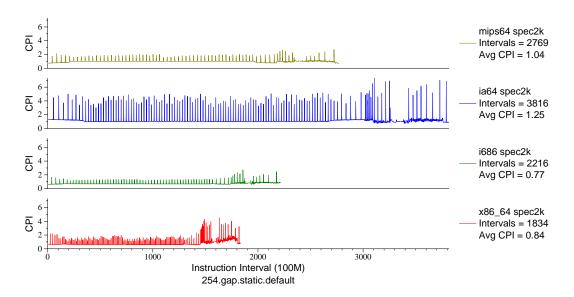

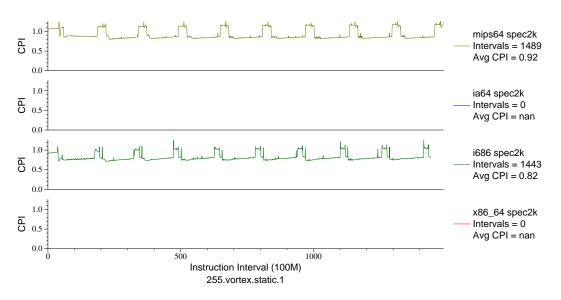

| F.41 | Multi-arch CPI plot for vortex.1 (INT, C, Database)             |             |

| F.42 | Multi-arch CPI plot for vortex. 2 (INT, C, Database)            |             |

| F.43 | Multi-arch CPI plot for vortex. 3 (INT, C, Database)            |             |

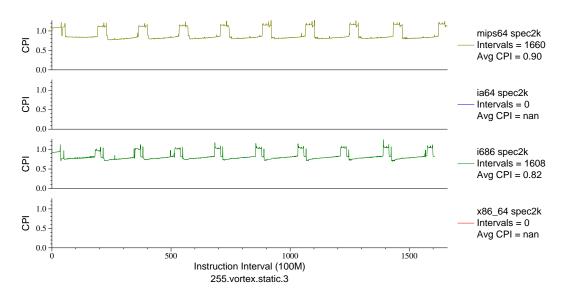

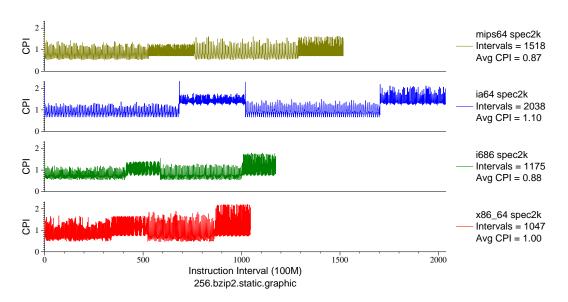

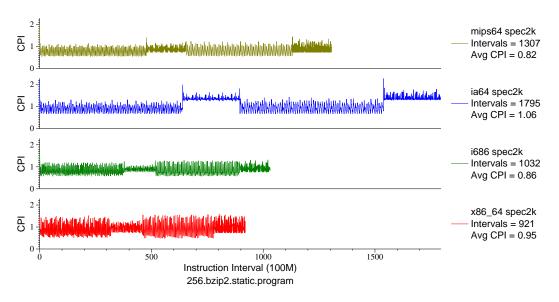

| F.44 | Multi-arch CPI plot for bzip2.graph (INT, C, Compression)       |             |

| F.45 | Multi-arch CPI plot for bzip2.prog(INT, C, Compression)         |             |

| F.46 | Multi-arch CPI plot for bzip2.src (INT, C, Compression)         |             |

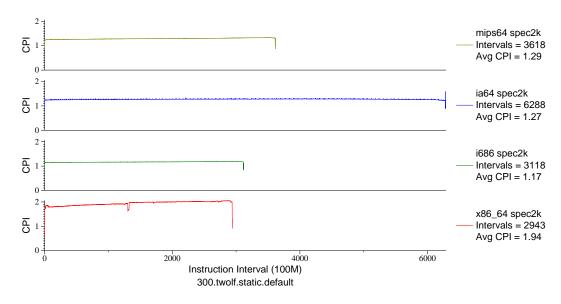

| F.47 | Multi-arch CPI plot for twolf (INT, C, Place/Route)             |             |

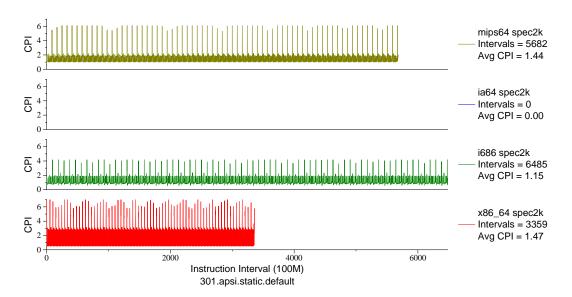

| F.48 | Multi-arch CPI plot for apsi (FP, F77, Meteorology/Pollution) . | 278         |

| G.1  | L1 dcache accesses per instruction plot for gzip.graph (INT, C, |             |

|      | Compression)                                                    | 280         |

| G.2  | L1 dcache accesses per instruction plot for gzip.log (INT, C,   |             |

|      | Compression)                                                    | 281         |

| G.3  | L1 dcache accesses per instruction plot for gzip.prog (INT, C,  |             |

|      | Compression)                                                    | 282         |

| G.4  | L1 dcache accesses per instruction plot for gzip.rand (INT, C,  |             |

|      | Compression)                                                    | 283         |

| G.5  | L1 dcache accesses per instruction plot for gzip.src (INT, C,   |             |

|      | Compression)                                                    | 284         |

| G.6  | L1 dcache accesses per instruction plot for wupwise (FP, F77,   |             |

|      | Quantum Chromodynamics)                                         | 285         |

| G.7         | L1 dcache accesses per instruction plot for swim (FP, F77, Mete-   | 206     |

|-------------|--------------------------------------------------------------------|---------|

| G.8         | orology/Water)                                                     | 286     |

| <b>G</b> .0 | Grid Solver)                                                       | 287     |

| G.9         | L1 dcache accesses per instruction plot for applu (FP, F77, Fluid  | 207     |

| 0.,         | Dynamics)                                                          | 288     |

| G.10        | L1 dcache accesses per instruction plot for vpr.place (INT, C,     |         |

|             | FPGA Place/Route)                                                  | 289     |

| G.11        | L1 dcache accesses per instruction plot for vpr.route (INT, C,     |         |

|             | FPGA Place/Route)                                                  | 290     |

| G.12        | L1 dcache accesses per instruction plot for gcc.166 (INT, C, C     |         |

|             | Compiler)                                                          | 291     |

| G.13        | L1 dcache accesses per instruction plot for gcc. 200 (INT, C, C    |         |

| _           | Compiler)                                                          | 292     |

| G.14        | L1 dcache accesses per instruction plot for gcc.expr (INT, C, C    |         |

| ~           | Compiler)                                                          | 293     |

| G.15        | L1 dcache accesses per instruction plot for gcc.int (INT, C, C     | 20.4    |

| C 1 (       | Compiler)                                                          | 294     |

| G.16        | L1 dcache accesses per instruction plot for gcc.sci (INT, C, C     | 205     |

| C 17        | Compiler)                                                          | 295     |

| G.1/        | L1 dcache accesses per instruction plot for mesa (FP, C, 3D-       | 296     |

| C 10        | graphics)                                                          | 290     |

| G.10        | Fluid Dynamics)                                                    | 297     |

| G 19        | L1 dcache accesses per instruction plot for art . 110 (FP, C, Neu- | <i></i> |

| G.17        | ral Networks)                                                      | 298     |

| G.20        | L1 dcache accesses per instruction plot for art . 470 (FP, C, Neu- |         |

| 0.20        | ral Networks)                                                      | 299     |

| G.21        | L1 dcache accesses per instruction plot for mcf (INT, C, Combi-    |         |

|             | natorial Opt)                                                      | 300     |

| G.22        | L1 dcache accesses per instruction plot for equake (FP, C, Seis-   |         |

|             | mic Propogation)                                                   | 301     |

| G.23        | L1 dcache accesses per instruction plot for crafty (INT, C, Chess  | )302    |

| G.24        | L1 dcache accesses per instruction plot for facerec (FP, F90,      |         |

|             | Facial Recognition)                                                | 303     |

|             | L1 dcache accesses per instruction plot for ammp (FP, C, Chemistry | )304    |

| G.26        | L1 dcache accesses per instruction plot for lucas (FP, F90, Num-   |         |

| ~           | ber Theory)                                                        | 305     |

| G.27        | L1 dcache accesses per instruction plot for fma3d (FP, F90, Crash  | •       |

| C 20        | Simulation)                                                        | 306     |

| G.28        | L1 dcache accesses per instruction plot for parser (INT, C,        | 205     |

| C 20        | Word Processing)                                                   | 307     |

| G.29        | L1 dcache accesses per instruction plot for sixtrack (FP, F77,     | 200     |

|             | Nuclear Physics)                                                   | 200     |

| (C 31 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | L1 dcache accesses per instruction plot for eon.cook (INT, C++,                                                                                                                                                 |                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|