# CANONICAL NEURAL COMPUTATIONS IN ASYNCHRONOUS NEUROMORPHIC CIRCUITS

# A Dissertation

Presented to the Faculty of the Graduate School of Cornell University

in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

by

Nabil Imam

May 2014

© 2014 Nabil Imam

ALL RIGHTS RESERVED

# CANONICAL NEURAL COMPUTATIONS IN ASYNCHRONOUS NEUROMORPHIC CIRCUITS

Nabil Imam, Ph.D.

#### Cornell University 2014

This thesis describes the architecture, implementation and application of a parallel computing system modeled after the structure and function of neural circuits in animal brains. The system is constructed with custom digital CMOS circuits and consists of distributed cores of model neurons and synapses that are embedded in a spike-based communication network. Energy consumption associated with high neural fanout is kept at a minimum in the system with the use of distributed on-chip memory arrays that tightly couple synaptic information with the neural datapaths, and with the use of event-driven asynchronous communication circuits that efficiently transfer spikes within and between cores. A compact crossbar memory arrangement along with compact and low-power neuron datapaths add to the energy efficiency of the system and keep the silicon footprint of each core small. Synchronization circuitry between the computing and communication elements ensure that all cores run in lockstep with a software simulator enabling rapid development of algorithms. In a 28nm CMOS process 4096 of these cores are packed in a single chip measuring  $4.3cm^2$ . The chip supports 1 million neurons and 256 million synapses, operates in real time and consumes only 70mW during typical network operation. Because of its compact size, high energy efficiency and real-time operating speed, the chip can be used to implement brain-inspired algorithms in a wide range of mobile and embedded systems. For demonstration, the implementation of four canonical neural computations – intensity invariance, pattern decorrelation, associative recall and attentional modulation - is developed in this thesis.

#### ACKNOWLEDGEMENTS

A wonderful and talented group of individuals have made the past few years very enjoyable for me. I have the following people to thank for their advice in some of the most exciting areas of research and for their company in some of the most memorable times.

Thank you Professor Rajit Manohar for helping me develop an exciting research agenda through your insightful guidance. Thank you for the freedom you have given me and for the opportunities that have come my way because of our work. It was great to have an advisor with so many interesting ideas about so many different fields.

Several other professors at Cornell have influenced my work in very productive ways. Thank you Professor Thom Cleland for helping me develop intuitions about the workings of sensory systems and for your exciting ideas about the applications of our work. Thank you Professor Al Molnar for initially helping me come to grips with neuroscience and for your continued advice. Thank you Professor Kevin Tang for insightful discussions about brain networks and for pointing me towards productive ways to learn dynamical systems theory. Thank you Professor Barbara Finlay for introducing me to some exciting work in brain network development and evolution. Thank you Professor David Field for your insights on sensory coding and for your support and encouragement.

Several researchers at the IBM Almaden Research Center have also had a strong impact on my work. Thank you Dharmendra Modha, Bryan Jackson, Paul Merolla, John Arthur, Rodrigo Alvarez and Andrew Cassidy for your support and advice. I am looking forward to some exciting and productive years of collaboration ahead.

Thank you, Professors David Ahlgren, Mark Silverman, John Mertens and Harvey Picker at Trinity College. Your teaching, guidance and inspiration have been instrumental in my achievements so far.

My experience wouldn't have been complete without some wonderful friends. Kyle, you were a fantastic partner and it's unfortunate our collaboration was cut short. Carlos and Rob, thank you for those amazing tools. James and Kedar, thank you for some very

useful conversations and seminars. Ben, Dan, Raymond and gang, thank you for the hustle on the courts. Jon and Stephen, thank you for being contrasting but entertaining office mates. Filipp and Saber, thank you for a productive few months. The CSL crew, thank you for creating a fun community. Zac, Ali, Kirk, Basit and gang, and the SLC crew, thank you for those poker nights. Ruchira, thank you for being the most amazing person. Andrew, Pranav and gang, Ashesh and gang, Nikolay and gang, Asheaque, Farahin, Lisa and gang, and numerous other friends and acquaintances over the years, thank you for those crazy nights and great conversations.

Finally, thank you Mom, Dad and Tuhina for your support and encouragement, for the inspiration that you provide, and for your endless affection.

# TABLE OF CONTENTS

| 1             | Introduction                      |                                                        |    |  |  |

|---------------|-----------------------------------|--------------------------------------------------------|----|--|--|

| 2             | Neuromorphic Systems Architecture |                                                        |    |  |  |

|               | 2.1                               | Design Factors                                         | 5  |  |  |

|               |                                   | 2.1.1 Computing                                        | 5  |  |  |

|               |                                   | 2.1.2 Communication                                    | 6  |  |  |

|               |                                   | 2.1.3 Memory                                           | 9  |  |  |

|               |                                   | 2.1.4 Synchronization                                  | 10 |  |  |

|               | 2.2                               | Design of a Neuromorphic Core with Integrated Synapses | 11 |  |  |

|               |                                   | 2.2.1 Architecture and Operation                       | 12 |  |  |

|               |                                   | 2.2.2 Circuit Design                                   | 16 |  |  |

|               |                                   | 2.2.3 Results                                          | 27 |  |  |

|               | 2.3                               | Design of a Multi-Core System                          | 30 |  |  |

|               |                                   | 2.3.1 Spike Routing                                    | 30 |  |  |

|               |                                   | 2.3.2 Core Control                                     | 33 |  |  |

|               |                                   | 2.3.3 Results                                          | 36 |  |  |

| _             | ~                                 |                                                        |    |  |  |

| 3             | -                                 | ke-Based Information Coding                            | 38 |  |  |

|               | 3.1                               | Rate Codes                                             | 38 |  |  |

|               | 3.2                               | Temporal Codes                                         | 41 |  |  |

| 4             | Can                               | nonical Neural Computations                            | 46 |  |  |

|               | 4.1                               | Intensity Invariance                                   | 46 |  |  |

|               |                                   | 4.1.1 Relational Representations                       | 46 |  |  |

|               |                                   | 4.1.2 Global Inhibition                                | 47 |  |  |

|               | 4.2                               | Pattern Decorrelation                                  | 55 |  |  |

|               |                                   | 4.2.1 Inhibition Via Higher-Order Receptive Fields     | 57 |  |  |

|               |                                   | 4.2.2 Rhythm Generation and Phase Codes                | 59 |  |  |

|               |                                   | 4.2.3 Learning Inhibitory Weights                      | 60 |  |  |

|               |                                   | 4.2.4 Evaluation                                       | 63 |  |  |

|               | 4.3                               | Associative Recall                                     | 72 |  |  |

|               | 1.0                               | 4.3.1 Recurrent Associative Connections                | 73 |  |  |

|               |                                   | 4.3.2 Rhythm Generation and Phase Codes                | 73 |  |  |

|               |                                   | 4.3.3 Learning Associations                            | 74 |  |  |

|               |                                   | 4.3.4 Evaluation                                       | 76 |  |  |

|               | 4.4                               | Attentional Modulation                                 | 82 |  |  |

|               | 4.4                               | 4.4.1 Acetylcholine and Attention                      | 82 |  |  |

|               |                                   | 4.4.1 Acetylcholine and Attention                      | 83 |  |  |

|               |                                   | 4.4.2 Sahency Emhancement                              | 00 |  |  |

| 5             | Exa                               | mple Applications                                      | 87 |  |  |

| 6             | Con                               | Conclusion 93                                          |    |  |  |

| $\mathbf{A}$  | CH                                | CHP Notation 9                                         |    |  |  |

| $\mathbf{Bi}$ | Bibliography 96                   |                                                        |    |  |  |

# Chapter 1

# Introduction

Biological neural circuits are capable of an incredible range of energy-efficient real-time computations. Tasks such as sensory perception, motor pattern generation, autonomous learning and cognitive decision making are carried out by these circuits<sup>1</sup> in the brain much more effectively and efficiently than today's most advanced computer algorithms. Information is processed in these circuits through the spatiotemporal spiking activity of neurons, with different connectivity configurations between neurons with specific dynamical properties implementing distinct algorithms. The human brain consists of approximately  $10^{11}$  neurons and  $10^{14}$  synapses, all contained within a volume of 2L, weighing less than 4lbs, and running on a 20W power budget [1].

Simulation of brain circuits in general-purpose processors are common and specialized software environments such as NEURON [2] have been developed to facilitate them. General-purpose processors are based on a von Neumann computing architecture, wherein processing and memory are physically separated and instructions are largely executed following a sequential compute model. This architecture is not a natural fit to the parallel and event-driven nature of neural computations. The storage and retrieval of a large number of neuron and synapse parameters from off-chip memory arrays lead to high energy consumption and increased latency, limiting efficiency and scalability. In addition, the computing and communication circuitry of these processors are not customized for modeling the behavior of neurons and their networks. To achieve large-scale implementations using these processors requires supercomputer-levels of computational power and associated costs, for example [3] and [4]. More specialized off-the-shelf hardware such as GPUs [5] or FPGAs [6] can manage some parallel applications more efficiently, but the fine-grained parallelism of brain networks and their memory intensive simulations also

<sup>&</sup>lt;sup>1</sup>The basic computational units of the brain are nerve cells called neurons. The junction between the output of one neuron and the input of another is called a synapse. A configuration of neurons and synapses is referred to as a neural circuit or a neural network.

render these processors inefficient.

Custom-designed VLSI chips provide a means with which these inefficiencies can be overcome. Neural-inspired Application-Specific Integrated Circuits (ASICs), commonly referred to as "neuromorphic" circuits, are intended to mimic the parallel and distributed function of biological neural systems in real time and approach their compact size/weight and low power consumption. Implementing large numbers of model neurons and synapses in a scalable and reliable platform and within aggressive area and power constraints requires careful design and implementation choices to be made. Efficient design can lead to orders of magnitude better speed, energy consumption and compactness compared to off-the-shelf processors.

Traditionally, neuromorphic designs have used continuous-time analog circuits to model biological components, and digital asynchronous circuits for spike communication [7]. Analog circuits have been popular in the past, since they are compact, and reduce power consumption by directly using the transconductance properties of transistors to mimic the dynamics of neurons. Dense analog circuits however are sensitive to fabrication process variations, ambient temperatures and noisy environments, making it difficult to configure circuits that operate reliably under a wide range of external parameters. This limited correspondence between what the software (the neural algorithm) has been configured to do and how the hardware (the analog implementation) functions adversely affects the usability of such circuits in real-world applications and simulation-based research. In addition, analog circuits do not scale well to deep-submicron CMOS processes [8], in part due to a lack of high-density capacitors and increasing sub-threshold currents..

This thesis describes the architecture, implementation and application of a digital neuromorphic system that was designed to overcome the problems associated with implementing brain-like computations in off-the-shelf digital chips and neuromorphic analog hardware. The following features of the chip described here make it a highly-efficient brain-like processor –

- Parallel computing datapaths, custom-designed to model neuron-like dynamics in compact and low-power circuits, are distributed across the chip.

- Distributed memory arrays storing neuron and synapse configuration parameters are tightly coupled to the computing datapaths minimizing data movement across the chip. Each memory array has a crossbar architecture to efficiently implement a high neural fanout.

- Energy-efficient event-driven routing circuits, customized for spike-based communications, manage distributed communication between the computing and memory elements.

- Synchronization circuits maintain fidelity of freely-configurable algorithms.

- Deep submicron transistor feature sizes allow compact size and high energy-efficiency.

The resulting compact and low-power hardware can mimic large-scale brain-like networks in real-time, enabling new classes of algorithms in a variety of mobile and embedded systems. Example applications include brain-based robotics, neural-inspired pattern recognition systems, neural implants and brain-simulation platforms.

The thesis is organized as follows. Chapter 2 describes the architecture and circuitlevel description of a scalable neuromorphic processor that is inspired from the computing

and communication features of biological brains. Chapter 3 describes spike-based information coding mechanisms on the chip that reflect the operational principles of biological

neural circuits. Chapter 4 describes the configuration of four commonly observed neural

computations on the chip. The implementation of these computations are inspired from

the hypothesized mechanisms at play in several biological neural circuits, but are not

necessarily meant to be an exact replica. Rather, through necessary innovations and simplifications, it is shown that the configured computations are effective means of solving

pattern recognition tasks.

Together, these chapters demonstrate how the application of systems neuroscience principles to computer architecture and artificial intelligence can lead to new classes of powerful and efficient devices.

# Chapter 2

# Neuromorphic Systems Architecture

#### 2.1 Design Factors

Digital ASICs can be customized from the architecture level down to the transistor level to create compact, energy-efficient and real time neuromorphic systems. This section describes the design considerations associated with building such systems.

## 2.1.1 Computing

The response properties of neurons to synaptic inputs can be captured through various mathematical models. These range from low-level multi-compartment models to high-level phenomenological models [9]. Lower-level models precisely account for the morphological and electrochemical properties of neurons and synapses and capture their dynamical characteristics in detail. In contrast, higher-level models reduce the number of free parameters and capture the neuron's essential properties without accounting for all biophysical details.

These models, expressed as systems of differential equations, are implemented in a digital ASIC through customized circuitry that numerically solve the equations in discrete time. Because of this customization the solution of the differential equations are carried out with substantially higher speed, energy efficiency and compactness compared to that in general purpose processors. Any reduction in model complexity translates directly to simplifications in ASIC circuits and correspondingly reduces computing time, energy consumption and silicon footprint.

Transistors in modern digital circuits have switching speeds in the picosecond scale. Therefore these circuits easily solve the model differential equations within the millisecond timescales of biological neurons. For example, one iteration of the Izhikevich equations [9] with a 16-bit word length can be carried out within 86ns in a 65nm ASIC implementation

[10]. Thus a neuron model circuit can be run much faster than biological real time or alternatively, one instantiation of the circuit can be used to solve for multiple neurons (see Sec. 2.3.2).

The energy per neuron update, summed across all neurons, contributes to the overall system energy consumption and therefore should be kept low particularly for neuron models that require a large number of operations per update. For the 65nm ASIC neuron (point model) mentioned above, the energy consumption per neuron update is 0.5nJ. This is a relatively small number compared to the communication energy of the system (see Sec. 2.1.2).

The area footprint is the most significant factor in the design of a neuron circuit. Not only does it directly affect the number of neurons that can be implemented in a given silicon real estate it also affects the energy consumption associated with neural communications. To implement synapses, data storing connectivity information has to travel (often large distances) across the neuron circuits in the system. The large number of synapses in typical neural networks result in high energy consumption associated with this data movement (see Sec. 2.1.2). Smaller neuron circuits shorten the distance that this data moves and therefore increases the energy efficiency of neural communications. The 65nm ASIC neuron mentioned above occupies an area of  $0.03mm^2$ .

#### 2.1.2 Communication

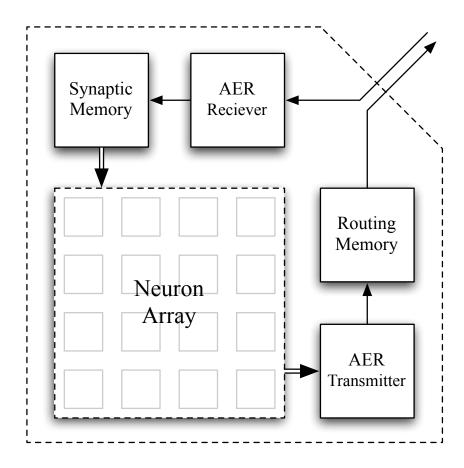

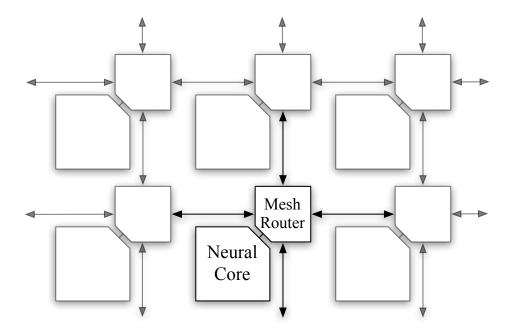

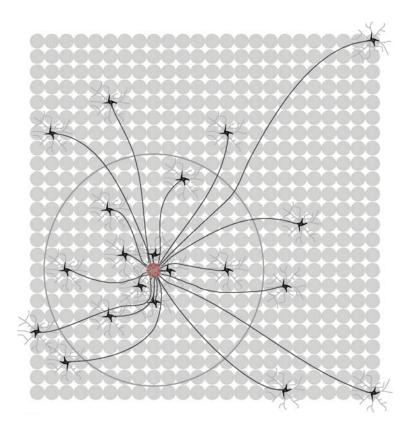

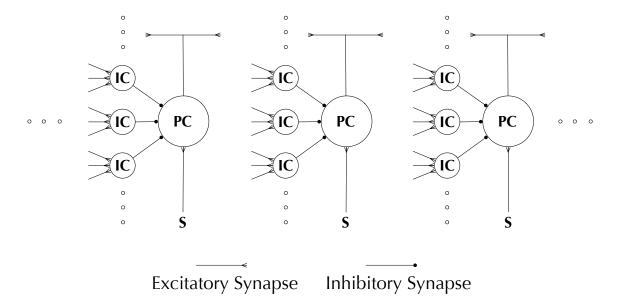

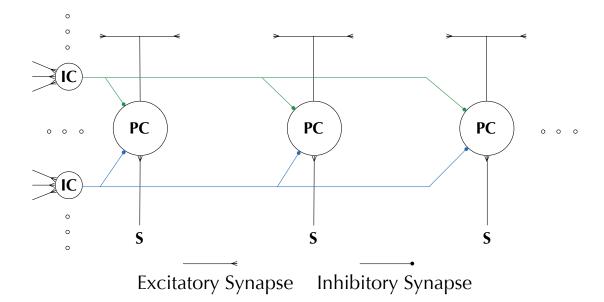

Typical neurons have 10<sup>3</sup> to 10<sup>4</sup> synapses, which make point-to-point connections among the neuron circuits with dedicated wires on an ASIC intractable for any significant number of neurons. However, neuron activity is measured in the Hz range, whereas ASIC wire bandwidth can reach hundreds of MHz to several GHz. Thus, neuromorphic systems [7, 11] time multiplex wire usage between groups of neurons to implement dense interconnectivity. These groups are encapsulated in *neural cores* (Fig. 2.1) and are tiled within a packet routing network (Fig. 2.2).

Figure 2.1: A typical neural core with on-core memory for storing connectivity configurations.

Communication circuits within a core time multiplex the connections of all neurons inside the core through a protocol termed Address-Event Representation (AER) [12]. In this protocol, each neuron in the core is associated with a unique address, and a shared I/O bus local to each core communicates all the spikes to and from the core via discretized AER packets. A packet usually takes the form of a (source, destination) tuple indicating the addresses of the source neuron and the destination neural core respectively. Some systems use other packet designs, for example packets with multiple destination fields or packets without destination fields where the direction of routing is determined via a memory look up at each routing stage.

The AER packet associated with each neuron is usually stored in on-core memory (illustrated as "Routing Memory" in Fig. 2.1). Packets are accessed from this memory when neurons spike and they are sent out of the core via an AER-packet router [13, 14]. These routers are distributed across the cores and they direct inter-core traffic using the

Figure 2.2: Array of neural cores, connected by a 2D Manhattan mesh network.

source or destination fields of the packets. When a packet reaches its destination core its postsynaptic targets (i.e. the neurons inside the destination core that connect to the source neuron) along with the associated parameters (e.g. the synaptic weights) are accessed from off-chip or on-chip (illustrated as "Synaptic Memory" in Fig. 2.1) memory to update the state of the network.

For a target temporal precision (usually 1 millisecond), the speed of this AER communication system (usually 100s of MHz of packet bandwidth) determines the degree of multiplexing that can be implemented as well as the total network size and network activity that can be supported. The area footprint of the communication circuits is relatively small compared to the area occupied by the neurons in the core, but nevertheless should be kept at a minimum to reduce area overhead.

The most critical factor in the design of the communication system is the active energy consumption of data movement. Because the number of synapses exceed the number of neurons by three to four orders of magnitude in typical neural networks, the energy consumption associated with fetching synaptic parameters from off-chip memory as well as that associated with AER packet traversal is a large determinant of the energy efficiency of the system. For example, in a system of ARM968 processors [15] that communicate across a custom-designed AER routing network and that store synaptic information in off-chip memory, the energy per neural update (Izhikevich equations [9]) is 27nJ while the energy per synaptic event is 8nJ. This means that a neuron with a 1ms timestep, firing at 40Hz and making 1000 synaptic connections will have over an order of magnitude more communication energy consumption than computing energy consumption. This effect is even more pronounced for custom neuron circuits where computing energy goes down by an order of magnitude (see Sec. 2.1.1).

A variety of ASIC design optimizations can significantly lower the communication energy consumption (see Sec. 2.2). These include for example, tightly coupling large memory blocks to the neural cores to reduce the distances of data travel associated with fetching synaptic configurations, arranging these memory blocks in structures that minimize storage and access requirements, restricting the number of cores that an AER packet can communicate to, customizing routing topologies to reflect the properties of typical neural networks, and using event-driven asynchronous communication circuits that naturally minimize energy consumption during idle periods while maintaining high throughput during bursty periods<sup>1</sup>.

# 2.1.3 Memory

Typical general-purpose multiprocessors have some amount of on-chip cache memory that compliment the computing cores of the processor. In the implementation of neural networks on these processors the on-chip memory is usually used up for the storage of neuron variables, parameters, and update instructions. For example, in the ARM968 implementation [15] mentioned above, all of of the 96 KBytes of tightly coupled memory

<sup>&</sup>lt;sup>1</sup>In addition, in both ASICs and general purpose multiprocessors, mapping highly communicating neural groups close to each other in the hardware can significantly reduce energy consumption.

associated with each core is used for the storage and update of 1000 neurons. The synaptic parameters in this system are stored in a 1 Gbits off-chip memory table.

As mentioned in the previous section, the energy consumption associated with fetching synaptic configuration parameters from off-chip memory tables is a large factor in the total energy consumption of the system. The energy consumption and latency of accessing off-chip memory in a medium-size chip (in the order of pJ/bit and 10s of ns respectively) are about 2 orders of magnitude higher compared to accessing on-chip memory that is tightly localized with the computing datapaths (in the order of fJ/bit and a 100s of ps). Therefore as mentioned earlier it is highly desirable to incorporate memory blocks storing synaptic parameters close to the neural cores in an ASIC implementation.

With hundreds or thousands of synaptic connections per neuron, the size of the onchip memory block for synapse storage becomes a critical design factor. For example, in a 65nm technology the size of a SRAM bit cell is approximately  $0.6um^2$ . Assuming 1000 connections per neuron for 256 neurons in a single core and 8-bit synaptic weights, this corresponds to approximately  $1.2mm^2$ . Assuming an Izhikevich neuron datapath  $(0.3mm^2$  in 65nm [10]) shared for all the neurons in the core, the synaptic memory area is  $4\times$  the neuron datapath area. Thus, reduction of the synaptic memory area, for example by using new memory technologies [16] and compact memory designs (see Sec. 2.2), is a crucial component of the ASIC implementation.

# 2.1.4 Synchronization

Digital neuromorphic systems can be designed to run discrete-time simulations of neural networks like those that run through software environments on general purpose processors. In such instances a fidelity between hardware operation and an equivalent software simulation is desirable. A one-to-one equivalency between the two allows users to develop and test algorithms in a software simulator of the neuromorphic system on any platform with the guarantee that it will run exactly the same way once mapped on the hardware.

For such equivalency between hardware and software with respect to a global simulation timestep, extra circuitry is necessary inside a neural core to synchronize the integration of presynaptic spikes (coming from a shared non-deterministic routing network) with the generation of postsynaptic spikes in the neurons. Such synchronization circuits, along with necessary bounds to the computation and communication time in the system, can keep hardware operation in lock step with a software simulator (see Sec. 2.2.1).

Alternatively, a system can be designed to run freely without synchronization to a global update signal of a discrete-time simulation. Neural updates can be carried out as AER packets come in, or updates can be continuously made and incoming packets checked for between updates. Without the need to lock to a global timestep, the speed of the system will only be bound by the speed of the circuits. Hardware-software correspondence will no longer be guaranteed due to indeterministic communication sequences.

#### 2.2 Design of a Neuromorphic Core with Integrated Synapses

This section presents the design and implementation of a scalable asynchronous neuromorphic computing core [11] named Golden Gate, specifically describing (i) the asynchronous circuits that mimic central elements of biological neural systems; (ii) an architecture that integrates computation, communication and memory; (iii) the asynchronous communication infrastructure required to accommodate the architecture; and (iv) the synchronization mechanisms required to maintain a one-to-one correspondence with software (this is the first neuromorphic system to demonstrate such an equivalence). A prototype chip consisting of a single core with 256 digital leaky-integrate-and-fire neurons, 1024 inputs, and  $1024 \times 256$  programmable binary synapses implemented with a SRAM crossbar array is described. The entire core fits in a 4.2mm<sup>2</sup> footprint in IBM's 45 nm SOI process and consumes 45pJ per spike in active power.

Two primary factors are behind the efficiency of the core. First, an on-chip memory array that stores synaptic parameters is integrated in close proximity to the neurons

minimizing data movement across the system. A crossbar architecture in the memory array is used to implement high neural fanout with low storage requirements. Second, an asynchronous design style results in circuits that naturally mimic the distributed event-driven processing of neural networks and ensures that power dissipation of inactive parts of the system are kept at a minimum.

#### 2.2.1 Architecture and Operation

#### Neurons and Synapses

The leaky integrate-and-fire model of a neuron captures the behavior of real neurons in a range of situations and offers an efficient implementation. This neuron model is used as the basic computational unit of the core.

The neurons in the chip are interconnected through axons and synapses. Each axon may correspond to the output of a neuron in the same core or somewhere else in a large system of many cores. Some axons may also be driven by embedded sensors or some external driver. The connection between axon j and neuron i is represented as  $S_{ji}$ . Each axon is parameterized by a type  $G_j$  that can take one of three different values indicating the type of synapse (e.g. strong excitatory, weak excitatory or inhibitory) that the axon forms with neurons it connects to. Each neuron is parameterized by a leakage current L, a spike threshold  $\theta$  and three synapse weights  $W^0$ ,  $W^1$ ,  $W^2$  that correspond to the different axon types. All these parameters are configurable during start-up.

The core implements a discrete-event simulation where the neuron states are updated at each timestep according to external input and interconnectivity. The state of neuron i at some time t, is represented by its voltage  $V_i[t]$ , while the state of axon j is represented by its activity bit  $A_j[t]$ .

The parameters and state variables of the system are tabulated in Fig. 2.3. Neuron i receives the following input from axon j:

$$A_j[t] \times S_{ji} \times W_i^{G_j}$$

.

| NAME           | DESCRIPTION                                | SIZE AND TYPE           |

|----------------|--------------------------------------------|-------------------------|

| V <sub>i</sub> | Voltage of Neuron i                        | 10 bit signed variable  |

| $W_{i}^{02}$   | 3 Synaptic Weights of Neuron <i>i</i>      | 9 bit signed constant   |

| Li             | Leak of Neuron i                           | 9 bit signed constant   |

| $\theta_i$     | Threshold of Neuron i                      | 8 bit unsigned constant |

| $S_{ji}$       | Connection between axon $j$ and neuron $i$ | Binary constant         |

| $G_j$          | Type of Axon <i>j</i>                      | 3 distinct constants    |

| $A_j$          | State of Axon j                            | Binary Variable         |

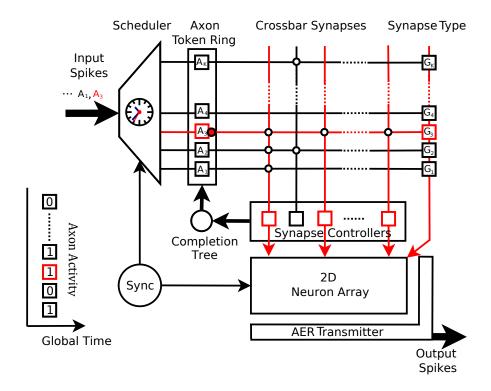

Figure 2.3: Top: Architecture of the neuromorphic core with K axons and N neurons. Each junction in the crossbar represents a synapse between an axon (row) and dendrite (column). Each neuron has a dedicated column in the crossbar. Active synapses are represented by an open circle in the diagram. An example sequence of events in the core is illustrated. The scheduler accepts an incoming address event and communicates with the axon token-ring. The token-ring activates axon 3 (A3) by asserting the third wordline of the SRAM crossbar array. As a result, a synaptic event of type G3 is delivered to neurons  $N_1$ ,  $N_3$ , and  $N_M$ . The AER transmitter sends out the addresses of these neurons if they consequently spike. Bottom: State variables and parameters of the system. All values are represented as integers, and all constants are configurable at start-up.

The neuron's voltage is updated at each time step by subtracting a leakage from its voltage and integrating the synaptic input from all the axons:

$$V_i[t+1] = V_i[t] - L_i + \sum_{j=1}^{1024} (A_j[t] \times S_{ji} \times W_i^{G_j}).$$

When V[t] exceeds a threshold  $\theta$ , the neuron produces a spike (represented by a digital '1' in its output) and its voltage is reset to 0. Negative voltages are clipped back to 0 at the end of each time step.

#### Communication Infrastructure

At the heart of the neurosynaptic core is a crossbar memory that forms the synapses between the axons and the neurons. This embedded memory allows large synaptic fanout without resort to off-chip memory, drastically reducing energy consumption and latency associated with accessing synaptic parameters (See Sec. 2.1.3). The crossbar array is user configurable and arbitrary networks can be set up in the system (e.g. Axons 1, 2, and 3 are connected to the first neuron in the 2D neuron array in Fig. 2.3). Each row of the crossbar corresponds to an axon, each column corresponds to the input of a neuron (the dendrite), and the junctions are binary synapses implemented by a two terminal memory cell (e.g., SRAM). Thus each of the N neurons may get up to K synaptic inputs depending on the activity in the axons and the configuration of the crossbar. K was chosen to be 1024 and N was chosen to be 256 resulting in 1024×256 crossbar synapses and an enormous configuration space. Each row of the crossbar memory has two additional bits that indentify the type of the axon. The postsynaptic neurons weigh a synaptic event on an axon with one of three distinct 8-bit weights based on this type information.

Spikes events are sent to and from the core using address-event representation (AER) packets (See Sec. 2.1.2 and Sec. 2.3.1). On the output side, an AER transmitter [12] encodes spiking activity by sending the locations of active neurons through a multiplexed channel, leveraging the fact that the bandwidth of wires (easily larger than 100s of MHz) is orders of magnitude larger than the bandwidth of biological axons (in the 10s of Hz

range). The spikes can be sent off chip, or routed to an axon of another core via a memory table. On the input side, an AER receiver delivers incoming spikes to the appropriate axon at a time determined by a configured field in the AER packet. As spikes are serviced sequentially, their addresses are decoded to the crossbar where all 256 synaptic connections of an active axon are read out in parallel.

Because the crossbar structure implements the synaptic connections of an axon using a 256-bit (+2 bits for the type information) vector, the need to store and access 256 multibit synaptic weights for each synapse is eliminated. As a result, the energy consumption and area associated with implementing synapses is reduced. These are achieved however at the cost of reduced flexibility since the type and delay of an axon in the crossbar structure has to be the same for all postsynaptic targets.

#### Discrete-time Operation

An example sequence of operation in the core is illustrated in Fig. 2.3. The operation has two phases during each time step.

The positive edge of a global synchronization clock (Sync) initiates the first phase of operation. In this phase, address-events along with their time stamps are sent to the core and are received by the scheduler. The scheduler evaluates the time stamps and asserts the appropriate axons that go into a token-ring. The units in the token-ring that receive active axons assert the rows of the crossbar in a mutually exclusive manner. Once a wordline in the crossbar is activated all the neurons that are connected to the axon (corresponding to the 1's in the row) receive an input spike along with information about the type of the axon. The neurons update their voltages as axon events come in. The first phase needs to complete within the first half of the global synchronization clock (that usually has a period of 1 millisecond) – a precise margin in which neural updates need to complete for potentially all 1024 axon inputs.

In the second phase of operation, the negative edge of the synchronization clock is detected by all the neurons. On receiving this event, neurons whose voltages have exceeded their respective thresholds produce spikes in their output ports. The spiking addresses are encoded by the AER transmitter and sent out of the core sequentially. This phase needs to complete within the other half of the global clock – i.e. the AER transmitter has to service 256 potential spikes within the global timestep.

A 1 millisecond global clock period (typical temporal precision in biological neural networks) means that the performance requirements of the circuits in the two phases of operation are easily met. Breaking neural updates into two phases ensures that the hardware is always in sync with an equivalent software simulation at the end of each time step. Specifically, the order in which address-events arrive to the core or exit from the core can be variable due to resource arbitration, especially when events are sent through a non-deterministic routing network. To preserve one-to-one correspondence, the different orderings must not influence the spiking dynamics, and this is achieved in the system by first accounting for all the synaptic events and then checking for spikes.

## 2.2.2 Circuit Design

The neuromorphic architecture described above was implemented using asynchronous quasi-delay-insensitive (QDI) circuits [17] that are synchronized with the global timestep. A QDI design style leads to extremely robust circuits that remain operational under a wide range of process, voltage and temperature variations, making them ideally suited for mobile, embedded applications.

In this section the concurrent processes of the architecture is described using Communicating Hardware Processes (CHP - see Appendix) that can be synthesized into QDI asynchronous circuits using Martin's synthesis method [17].

#### Scheduler

The scheduler receives packets from outside the core and delivers spikes on the axons at specific times. The packets may come from spiking neurons in the core or from outside the core. In addition to these packets, the scheduler also receives a clock and a global

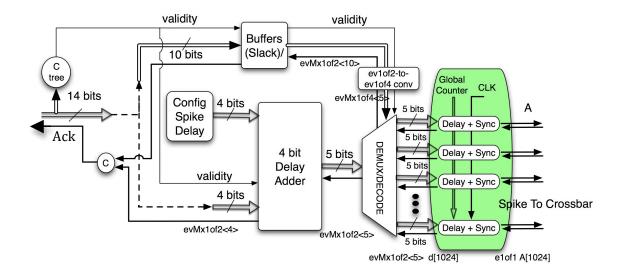

Figure 2.4: Internal structure of the Scheduler. The overall function is: (1) Receive input packets; (2) Add the stored axonal delay to the time field of the packet to get the spike delivery time; (3) Demultiplex the address field of the packet; and (4) Deliver the spike to the appropriate axons at the edge of a global clock when the global timestep equals the computed delivery time of the spikes.

counter time. The block also stores a configurable axonal delay (inside an SRAM array) for each of the axons. Each packet (y) coming in contains an axon address  $(y.dest\_addr)$  and a time of spike (y.dt - in units of clock ticks). The scheduler decodes the packet to determine where the spike should be delivered (the axon number). The time in the packet is added to the axonal delay for the specified axon, and this value is compared against the current global counter time on every tick of a clock that the scheduler receives. When the time matches, a spike is delivered to the crossbar. This makes the spike delivery to the crossbar synchronous with the global system clock. The CHP of the processes is:

```

Scheduler \equiv

*[[IN?y; \\ axon\_delay := SRAM[y.dest\_addr]; \\ delay\_y := y.dt + axon\_delay; \\ [delay\_y = timestamp]; \\ A[y.dest\_addr]!spike

]]

```

The scheduler implements the axonal delay stored in a 1024 (number of axons) by 4 (range of delays) SRAM array. It receives the packet in the channel IN, adds the axonal delay to the time in the packet, waits for the global time to reach this value and then delivers the spike to the axon corresponding to the address in the packet. Besides implementing the axonal delay, this procedure synchronizes input spikes to the core with the clock edge, implementing the first of the two phases of operation (Section 2.2.1) that allow the system to produce 1-1 correspondence with a software simulator.

The internal blocks of the scheduler are illustrated in Fig. 2.4. For the prototype chip, a common delay block was used instead of a full  $1024 \times 4$  SRAM array to implement the axonal delay. This fixed delay is a 4 bit number that can be configured at the chip's startup, and is the delay value for all axons. The Adder adds this delay to the time value in the packet and passes it to the DEMUX/DECODE unit. The control for the DEMUX/DECODE unit is the destination address in the input packet, slack-matched to the SRAM and the adder. The DEMUX then outputs 5 bits indicating the final timestamp for spike release to the axon. This value goes to 1 of 1024 [Delay + Sync] blocks. These blocks must contain full buffers at the input because all the hardware used prior to this stage is time-shared and the DEMUX output channel has to be "released" as soon as possible to allow assertion of the next spike. Each [Delay + Sync] unit compares the timestamp of the global timer with the obtained final timestamp and initiates a spikes to an axon when the value matches.

The clock synchronization is contained in the [Delay + Sync] unit. The synchronization part is not trivial and requires some design effort. The data obtained from the DEMUX/DECODE must be aligned to the clock without any knowledge of the data arrival time in relationship to the clock edge. Precautions have to be taken in order to avoid potential metastability during synchronization with the global clock. Such metastability may occur since there is no timing correlation between the edge of the global clock and the packets arriving from the router. A modified two flip-flop synchronization scheme is used in the design [18].

#### Axon Token-Ring

At an edge of the synchronizing clock, the scheduler pulls up the axon lines that have spikes. Each axon has a corresponding row (a wordline) in the crossbar memory array. The dendrites (inputs) of a neuron correspond to a column (bit line) of the crossbar array. Since a dendrite can potentially connect to multiple axons, the rows of the crossbar have to be asserted in a mutually exclusive manner. This function is carried out by an array of axon servers that implement a token-ring mutual exclusion algorithm [19]. Each server has an axon as its input and the wordline of the crossbar as its output. A token circulates among the servers to give them mutually exclusive access to the crossbar.

When an axon is asserted, its server requests its neighbor to pass the token. The request propagates through the token-ring, and the token is passed along to the requesting server. Upon the arrival of the token, the server asserts the corresponding row of the crossbar. The CHP of an individual server is given below. Channel A communicates with the axon from the scheduler and channel WL with the crossbar, while channels U and D communicate with the neighbor above or below. The local variable b represents the token. The D port of the last server is connected to the U port of the first server. The channel C communicates with a completion tree (see Fig. 2.3) that indicates when all the neurons have completed processing events for a particular axon.

$Axon\_Server \equiv$

$$\begin{split} * \llbracket [\overline{A} \longrightarrow \llbracket b \longrightarrow skip \ \llbracket \neg b \longrightarrow D!; b \uparrow \ \rrbracket; WL!; \\ & \llbracket \overline{C} \longrightarrow C; A? \rrbracket \\ & \llbracket \overline{U} \longrightarrow \llbracket b \longrightarrow skip \ \llbracket \neg b \longrightarrow D! \ \rrbracket; b \downarrow; U? \\ \rrbracket \rrbracket \end{split}$$

#### Crossbar Memory

The states of the memory cells of the crossbar array represent the synaptic configuration of a network (i.e. which axons connect to which neurons) and in part determine the unique properties of that particular network. Organizing the synapses in this crossbar structure allows an active axon to fan out to potentially 256 neurons in parallel through a single control operation. For large connectivity, this reduces the dynamic power consumption and accelerates the speed at which the network is updated.

The configuration of the crossbar has to be set up prior to the operation time of the chip. Shift register scanners were included to configure the bit cells of the array. Standard 6T SRAM cells were used as the bit cells. The axon token-ring controls the wordlines of the bit cells while a set of synapse controllers interfaces the bitlines with the neurons. The CHP of a synapse controller unit is given below.

$$Synapse\_Controller\_Unit \equiv$$

$$*[[BL.t \longrightarrow N!; C!$$

$$[BL.f \longrightarrow C!]$$

When the axon token-ring drives one of the wordlines of the crossbar, one of the two bitlines of each cell in the corresponding row will discharge asserting either the BL.t or the BL.f wires of the synapse controller. If BL.t is asserted the controller communicates with the neuron corresponding to the column to update the neuron's state. Once this communication is over, or if BL.f was the wire originally asserted, the controller

communicates with a completion tree. The right-most controller receives the "type" information for each axon (they are stored in the last 2 bit cells of each crossbar row) and communicates this information to the neurons. Once all synapse controllers have completed their operation, the completion tree communicates with the C channel of the axon token-ring, after which the token-ring unit with the token releases the wordline of the crossbar and token becomes free to travel. Another token-ring unit with an active axon will then get the token and assert its corresponding wordline.

#### Neuron

The neurons are the basic computational units in the system. They were implemented using dedicated circuits (non-multiplexed), allowing all the neural updates to happen in parallel. This parallelism comes at the cost of relative density inefficiency that is in part mitigated by the use of a dense technology.

The design of the neuron circuits needs to accommodate two conflicting requirements. On the one hand, a neuron must service events quickly to avoid holding up the crossbar. On the other hand, a neuron receives very few events in typical scenarios, so it must not burn dynamic power when it is idle. A purely event-driven design is therefore ideal: it has a fast service time (100MHz-GHz range), but only burns power during the rare occurrence of an event.

During the first phase of operation (Section. 2.2.1) each neuron receives event-driven synaptic input from the crossbar memory synapse controller. The neurons update their state (represented by an internal voltage V) by integrating the incoming synapses (Section. 2.2.1). During the second phase of operation, the neurons synchronize with the global clock edge, at which point they output a spike (represented by a 1 bit output) if their voltage is above threshold or leak out an amount of the voltage if it is below threshold. The synchronization of the neuron during the second phase of operation, along with the synchronization of the scheduler during the first phase (Section. 2.2.2) ensures that the operation in the core is in 1-1 correspondence with a software simulator.

The internal parameters of the neurons (the threshold, the leak, and the three synaptic strengths) are configured at start-up. They are all represented with 8-bit integers in 2's compliment form. The internal voltage of a neuron is represented by a 10-bit integer also in 2's compliment form.

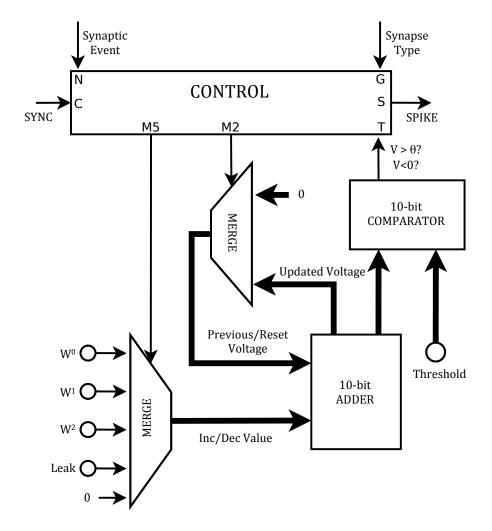

The operation of the neuron is decomposed into control and datapath blocks. A block diagram of the processes involved is illustrated in Fig. 2.5.

**Figure 2.5:** Block diagram of the neuron. The control block interfaces with the crossbar, directs information flow in the datapath, synchronizes with the global time step and outputs a spike when the neuron voltage exceeds its threshold. The datapath elements update the voltage after each synaptic event and check for a spike when directed by the control.

The CHP of the control block is:

$Neuron\_Control \equiv$

The control block interfaces with the synaptic input coming from the neuron's dedicated crossbar column through the channel N. Upon a communication request on this channel, the control reads in the "type" information of the axon through the channel G that connects to the synapse controller representing the last two columns of the crossbar. Before completing the handshake in N the control communicates with the datapath of the neuron through channels M5 (that relays synaptic type information) and M2 (for voltage control in the datapath). Once these communication actions have completed N and G are acknowledged and the next cycle of synaptic inputs may come in.

In the second half of the global timestep, the neurons receive a synchronization event in the channel C (that is driven by a process that uses one of the edges of the global clock to initiate a handshake). When this event comes in, the control initiates a communication with the datapath through the T channel. The datapath sends back one of three distinct values indicating whether the voltage for the current timestep is above threshold, below threshold but above zero; or below zero. If the voltage is above threshold the control communicates with the AER transmitter through the channel S to send out a spike. Through M2 the control also instructs the datapath to reset the voltage to 0 if there is a spike or if the voltage is below 0. If the voltage has not been reset to 0, the control instructs the datapath to apply the leak to the current voltage.

The CHP of the datapath units are:

$MERGE\_5 \equiv$

$$\begin{split} *\lceil [\overline{M5} \longrightarrow M5?d; \\ \lceil d = 0 \longrightarrow AI1! \, W^0 \\ \rceil d = 1 \longrightarrow AI1! \, W^1 \\ \rceil d = 2 \longrightarrow AI1! \, W^2 \\ \rceil d = 3 \longrightarrow AI1! L \\ \rceil d = 4 \longrightarrow AI1!0 \\ \rceil; \end{split}$$

]]

$MERGE_{-2} \equiv$

\*[[

$$\overline{M2} \longrightarrow M2?d$$

;

$$[d = 0 \longrightarrow AO0?x; \ AI0!x ] d = 1 \longrightarrow AI0!0 ] ;$$

]]

$ADDER \equiv$

$$\begin{split} * & [\overline{AI0} \wedge \overline{AI1} \longrightarrow AI0?x, \ AI1?y; \ z := x + y \\ & [ \overline{AO0} \longrightarrow AO0!z \\ & [ \overline{AO1} \longrightarrow AO1!z \\ ] ] \end{split}$$

$COMPARATOR \equiv$

```

*[\overline{T} \longrightarrow AO1?V;

[V > Threshold \longrightarrow T!0

[(V < Threshold) \land (V <= 0) \longrightarrow T!1

[(V < Threshold) \land (V > 0) \longrightarrow T!2

]; T

```

When the control drives  $MERGE\_5$ , the process forwards either a synaptic strength (during the integration phase), a leak (during the resetting phase if V > 0) or the value 0 (during the resetting phase if V <= 0) to one of the inputs of the ADDER process. When the control drives  $MERGE\_2$ , the process forwards either the previous voltage (during integration) or the value 0 (if V > threshold or V < 0 during the firing phase) to the other input of ADDER. The ADDER process is a 10 bit adder that sends out the sum of its inputs to the COMPARATOR and the  $MERGE\_2$  processes when they request it. The control drives COMPARATOR when it needs to evaluate the state of the neuron voltage.

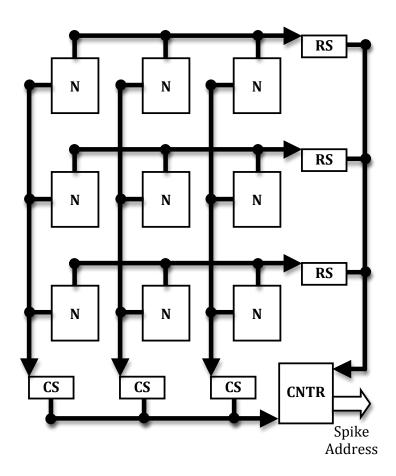

#### **AER** transmitter

Spikes from the 2-dimensional array of neurons are sent out of the core through token-ring AER transmitter circuits [12] that allow all the neurons to share one output channel. In this scheme, a set of row servers and column servers circulate tokens in each dimension of the neuron array and give spiking neurons mutually exclusive access to the shared communication channel. A counter keeps track of the location of the tokens, and sends out neuron addresses upon request. This methodology leads to compact transmitter circuits capable of efficiently servicing clusters of spiking activity.

The design of the transmitter is illustrated in Fig 2.6. The sequence of operation is: (1) A spiking neuron asserts a row request line; (2) The corresponding row server requests for the row token from its neighbors; (3) As the row token moves, the counter

Figure 2.6: Illustration of the AER transmitter architecture using a  $3\times3$  sample neuron array. When a neuron (N) has a spike, it communicates with its corresponding row server (RS) and column server (CS). A counter (CNTR) keeps track of circulating row and column tokens and sends out the spike address through the shared output bus.

keeps track of its position; (4) Upon receipt of the token, the row server acknowledges the row request; (5) The neuron then asserts a column request line; (6) The corresponding column server requests the column token from its neighbors; (7) As the column token moves, the counter keeps track of its position; (8) Upon receipt of the token the column server communicates with the counter to send out the row and column token addresses and then acknowledges the column request; (9) The neuron does a second communication with the row server to indicate the completion of service.

The neurons interface with their respective servers via open-drain shared row request lines and shared column request lines. The servers also communicate with the counter via shared wires. These wires need to be carefully implemented since transitions are shared across processes and span an entire dimension of the neuron array.

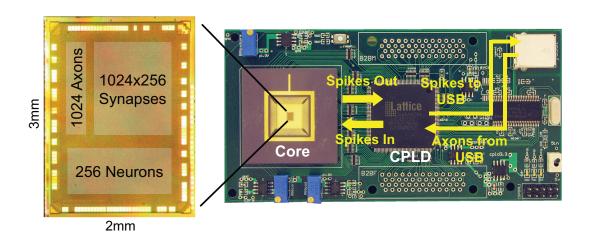

#### 2.2.3 Results

As demonstration of the architecture, one core (minus the scheduler) was implemented in a 45 nm SOI process. The fabricated chip occupies  $4.2mm^2$  of silicon (Fig. 2.7, left). Each of the 256 neurons in the core occupies  $35\mu\text{m} \times 95\mu\text{m}$ . Each SRAM bitcell in the  $1024 \times 256$  synaptic crossbar array occupies  $1.3\mu m^2$  (plus another 1.9  $\mu\text{m}^2$  associated with conservatively-designed periphery). A custom printed circuit board allows the chip to interface with a PC through a USB link (Fig. 2.7, right).

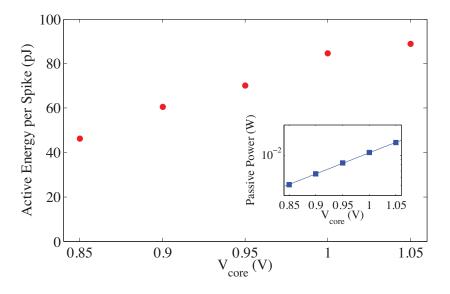

#### **Active Power**

The primary focus during the design was the reduction of active power since passive power can be addressed through fabrication options and active leakage reduction circuitry. The purely event-driven nature of the core results in very low power consumption since active power in such a design style is dependent only on the typically low activity rates of the neurons. The QDI methodology allows aggressive reduction of the operating voltage in the core without affecting chip functionality. As shown in Fig. 2.8, the core consumes only 45pJ of active power per spike at  $V_{dd} = 0.85$ .

Figure 2.7: Left: Die measures  $2mm \times 3$  mm including the I-O pads. Right: Test board that interfaces with the chip via a USB 2.0 link. Spike events are sent to a PC for data collection and can also be routed back to the chip via the CPLD.

Figure 2.8: Active and passive energy consumption in the core.

#### One-to-One Equivalence

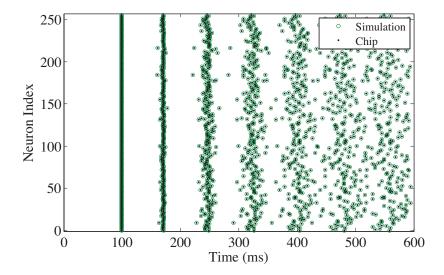

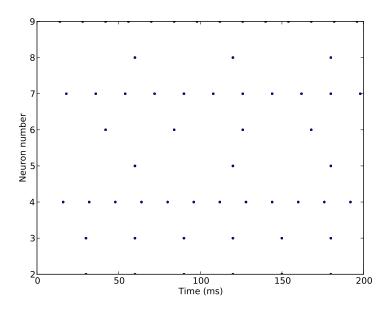

To test that the chip satisfied one-to-one equivalence, the synaptic strength and leak values of each neuron were set to +1 and the thresholds were set to to +100. Random connectivity was generated where each synapse had a 20% probability of being active. The CPLD was set to route all neuron spikes back into the core (neuron 0, 1, 2 drove axon 0, 1, 2, respectively), creating a complex recurrent network. After 100 time steps in the chip, all the neurons spike in unison due to their identical positive leaks. This first barrage of spikes is routed back around to the axonal inputs, activating the random pattern of excitatory recurrent connections. These inputs cause neurons to spike earlier in the next cycle, thereby having a de-synchronizing effect. Within a few cycles, the recurrently-driven activity dominates the dynamics leading to a complex spatiotemporal pattern. Results from a software simulation of a network with an identical configuration confirmed that the software and hardware have identical behavior (Fig. 2.9).

**Figure 2.9:** The spiking dynamics of the chip exactly matches software simulation when configured with the same parameters and recurrent connectivity. Spikes are plotted as dots for measured chip data and circles for simulation.

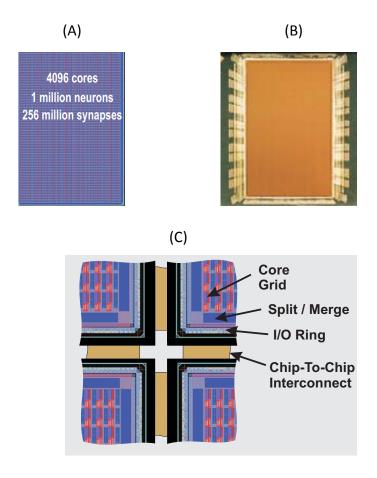

#### 2.3 Design of a Multi-Core System

A multi-core chip consisting of multiple instantiations of Golden Gate-like (Sec. 2.2) cores was fabricated in a 28 nm CMOS process [20]. The chip, named True North, consisted of 64 × 64 cores and a total of 1 million neurons and 256 million programmable synapses. For effective multi-core implementation, the design of the core was slightly modified from the design of Golden Gate. A router block was added to each core for the communication of spikes between cores. The number of axons in a core was reduced from 1024 to 256 to reduce the footprint of the core. The availability of many neurons and axons across numerous cores meant that this reduction did not have a significant effect on the types of networks that can be accommodated. Further reduction in the footprint of the core was achieved by multiplexing, via a control block, the datapath circuits that are used to update the states of the neurons in a core. The scheduler block (Sec. 2.2.2), that was not included in the 45 nm implementation (Sec. 2.2.3), was added to each core.

This section describes the design of True North, focusing on the communication and control circuitry required for efficient large-scale spike-based computing.

# 2.3.1 Spike Routing

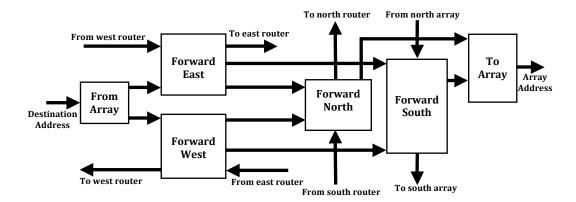

The cores were tiled in a 2-dimensional routing mesh and the router blocks of each core formed the backbone of the mesh. When a neuron of a core spikes, an associated AER (see Sec. 2.2.1) routing packet (stored in the local memory of the core) is sent to the local input terminal of the router. The router uses the information in the packet to direct it in one of five directions – east, west, north, south or local. Each router was also responsible for communicating traffic coming from the neighboring cores in each direction of the 2-dimensional mesh. A block diagram of the router is shown in Fig. 2.10.

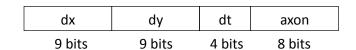

The AER routing packet produced by a spiking neuron is shown in Fig. 2.11. The packet encodes the address of one axon anywhere in the system. 5-bit dx and a dy fields in the packet relatively address the destination core by encoding the number of routing

Figure 2.10: Block diagram of the router associated with each core. The "To Array" and "From Array" blocks communicate packets to and from the local core. The "Forward East" and "Forward West" blocks communicate packets coming from each of the horizontal directions in the mesh. The "Forward North" and "Forward South" blocks do the same for the vertical directions in the mesh.

hops in the horizontal and vertical directions of the mesh respectively. At each hop, the router decrements the value in the dx field (for a horizontal hop) or the dy field (for a vertical hop). A 4-bit dt field in each packet encodes a delivery time that allows users to configure axonal delays. A 8-bit axon field in each packet encodes the address of the axon in the crossbar memory (see Sec. 2.2.1) of the destination core. The dt and axon fields are decoded by the scheduler block of the destination core to assert the destination axon at some time of the simulation. A necessary condition to maintain 1-1 correspondence between hardware and software (see Sec. 2.2.1) is that the routing network routes the spike to the destination core within dt ticks of the global timestep.

Figure 2.11: The AER routing packet associated with each neuron.

The AER packet design along with the on-chip crossbar memory structure (Sec. 2.2.1) results in efficient spike-based communication. When a neuron spikes it sends out one

packet addressing only one axon of the whole system instead of addressing its postsynaptic neurons individually. The drawback of this is that the postsynatpic targets of a neuron has to be restricted to one core (and 256 neurons) of the system<sup>2</sup>. As noted in Sec. 2.2.1, the integrated crossbar synaptic memory inside the core results in a drastic reduction of distances that data has to travel across the system compared to an implementation that uses off-chip memory.

The router was constructed with asynchronous QDI circuits that naturally mimic the event-driven nature of neural communications. In a typical application, neurons in a core will stay inactive for relatively long periods of time with intermittent bursts of spikes caused for example by some change in the external environment that the neurons represent. Spikes therefore are not expected to create regular traffic patterns in the router and therefore a synchronous design would result in energy overheads or extra circuit complexity.

The circuit-level description of the router and its deadlock free operation in the mesh are described in [14].

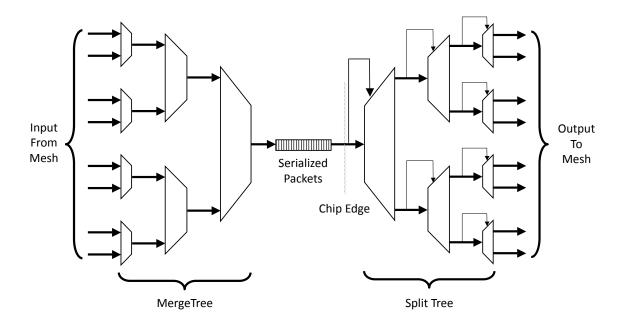

Circuitry for chip-to-chip spike communication at the edges of the chip enable the scalability of True North to multi-chip systems. These circuits implement serialization and deserialization processes that multiplex AER packets crossing chip boundaries through limited I/O pins. Before exiting a row (or column) of a mesh, each packet is tagged with a 6-bit value to identify the row (or column) of the destination mesh that the packet is to be delivered to.

The serialization and descrialization processes were implemented with asynchronous merges and asynchronous controlled splits as shown in Fig. 2.12. The splits at the destination use the 6-bit tag to direct the packet towards its destination in the receiving chip. With these processes at all four edges of a chip, multiple chips can seamlessly tile together without any modification to the routing processes inside a chip.

<sup>&</sup>lt;sup>2</sup>This restriction can be overcome using multi-stage synaptic communications using multiple neuron instantiations to simulate one neuron.

Figure 2.12: Chip-to-chip serialization/deserialization process illustrating the communication of AER packets across chip boundaries. The merge tree adds a tag to the AER packet and the split tree uses the tag to direct the packet towards its destination. The padded bits are stripped off before the packets enter the receiving mesh.

#### 2.3.2 Core Control

Whereas Golden Gate (Sec. 2.2) has 256 parallel neuron datapaths per core, True North uses one multiplexed datapath block to sequentially update the state of all 256 neurons in a core. This design choice lowers the area footprint of the neurons and consequently enables the implementation of a more complex neural update equation [21] within aggressive area constraints. The latency overhead associated with multiplexing is not significant because neural updates are in the millisecond scale (orders of magnitude slower compared to transistor switching speeds) and all 256 updates are carried out well within 1 millisecond unless held up by the spike communication system (see below). The variables and parameters of each neuron in a core reside in a memory array that is integrated with the synaptic memory array (Sec. 2.2.1) of the core. The memory block is tightly localized with the datapath block, and with the small feature sizes of a 28 nm process, the energy overhead associated with data movement from the memory onto the multiplexed neural

datapaths is not significant.

Parallelism is maintained at the multi-core level with 4096 cores operating in parallel and communicating through the mesh routing fabric.

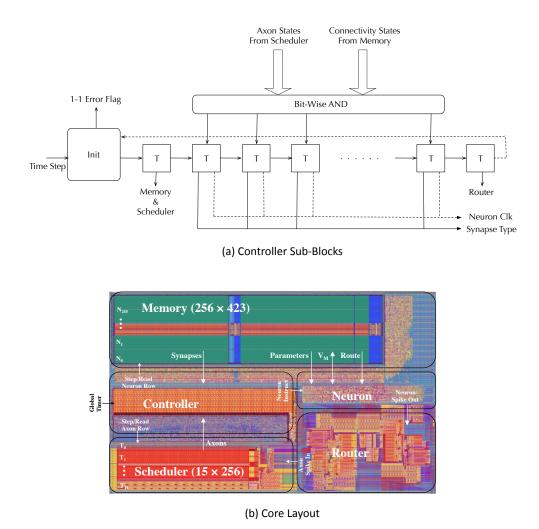

A control block inside each core coordinates the activity of the other blocks to implement the multiplexing. This is carried out with the following steps and is illustrated in Fig. 2.13.

- 1. At the positive edge of the global synchronization signal ("Time Step" in Fig. 2.13a) the control communicates with the memory to assert the wordline of one memory row. Consequently, the variables and parameters of a neuron are read by the neuron datapath, the state of the configured connections of the neuron are read by the control, and the value of the output AER packet of a neuron is buffered on the local input terminal of the router. The control also accesses the state of the axons in the given timestep from the scheduler. A sub-block of the control carries out a bit-wise AND between the state of the connections and the state of the axons.

- 2. Through a series of blocks (represented by T in Fig. 2.13a) that implement tokenring mutual exclusion [19], synaptic integration is carried out in the neuron datapath

for each active synapse (the output of the bit-wise AND). Each of these blocks store

the type information of its corresponding axon. An axon can be one of four types

representing different strengths of excitatory or inhibitory inputs to the neuron

(similar to the synaptic integration in Golden Gate described in Sec. 2.2). At the

arrival of the token in a token block, a clock signal is generated and the synapse

type communicated to the synchronous neuron datapath (see below) if the token

block has an active synapse. At the end of the period of the generated clock, the

token block passes the token to its neighbor.

- 3. After all axons have been accounted for, a final token block communicates with the router. The router in turn communicates with the neuron, and in the event of a spike the buffered AER packet is sent out from the core.

- 4. The updated state of the neuron is stored back into memory.

- 5. The steps are repeated for 256 neurons in sequence. Note that in the event of high traffic congestion in the local routing network, the token can circulate back to the block that communicates with the router before the router is able to send out the packet of the previous spiking neuron. In such a scenario the system will stall until the communication network frees up.

Figure 2.13: (a) The sub-blocks of the controller consist of an initialization block (Init) that initializes update at the arrival of the global timestep, a set of token blocks (T) that communicate with other elements of the core, and a bit-wise AND block that determines the state of the synapses. (b) Layout of the core illustrating its operation.

The control sub-blocks (Fig. 2.13a) are designed with asynchronous event-driven circuits that naturally fit with the other event-driven communication blocks of the system (namely the router and the scheduler). This design style is especially effective in the token blocks of the control since the state of the synaptic inputs are not known apriori—they are dependent on the network activity and the connectivity configuration. Instead of having to wait for predefined clock periods, the asynchronous token blocks swiftly skip inactive synapses thereby completing the neural updates at a faster pace. The extra speed is especially critical at times of spike traffic congestion in the local routing network that can hold up progress of sequential neural updates, as described above, and endanger the 1-1 correspondence feature of the chip.

In the event that traffic congestion slows down the operation of the control to a point where it is unable to carry out all 256 updates within the global timestep (1 ms), an error signal is sent out of the control to indicate a breakdown of 1-1 correspondence between hardware and software. In this scenario the user would be required to reconfigure the network (e.g. by mapping the network more efficiently or reducing the network activity) if 1-1 correspondence is to be maintained.

In contrast to the control, router and scheduler blocks, the neuron block was constructed with synchronous circuits. This allowed the use of commercial design tools that are more streamlined than asynchronous design tools. In addition, the reduced number of wires in a synchronous design compared to a QDI asynchronous one (where multiple wires are required to represent one bit) resulted in a smaller footprint of the datapath elements.

#### 2.3.3 Results

True North was fabricated in Samsung's 28nm process (Fig. 2.14 a and b) [20]. Each chip consists of  $64 \times 64$  cores tiled in two dimensions and occupies an area of  $4.3cm^2$ . Each core measures  $390um \times 240um$  (Fig. 2.13b), 18 times smaller than the core of Sec. 2.2.

A probabilistically-connected recurrent network with neurons firing at 20Hz and 50% utilization of the crossbar synapse array was configured onto each of the cores. At 0.775V the chip consumed 70mW, corresponding to 26pJ per synaptic event and 70uJ per millisecond timestep [20]. This is four orders of magnitude lower than a general-purpose processor running the same model [22].

With each chip supporting a million neurons and 256 million synapses, multi-chip systems (Fig. 2.14c) can be constructed to implement millions of neurons and billions of synapses. The system thus provides a platform for implementing scalable brain-like computations in compact, energy-efficient and real-time systems.

**Figure 2.14:** (a) The layout of the chip consists of cores tiled in a 64 × 64 mesh. (b) Picture of chip die. (c) Illustration of chip tiling for a multi-chip system.

## Chapter 3

# Spike-Based Information Coding

Trains of spikes between neurons communicate information across a neural circuit. These spike trains are encoded as either rate codes or temporal codes in a single neuron or in a population of neurons. Codes are distinguished by their time scale of operation<sup>1</sup>, their tolerence to noise, and their energy efficiency. This section describes the implementation of these spike codes in Golden Gate (the neuromorphic core of Section 2.2). The neural computations described in Section 4 use these codes.

#### 3.1 Rate Codes

Neurons may change their average firing rate over some interval of time as the strength of their inputs are varied. Such firing rate modulations are ubiquitous across the brain [23]. Examples of neurons that use firing rate codes include retinal ganglion cells, olfactory sensory neurons, and motor neurons at neuronuscular junctions.

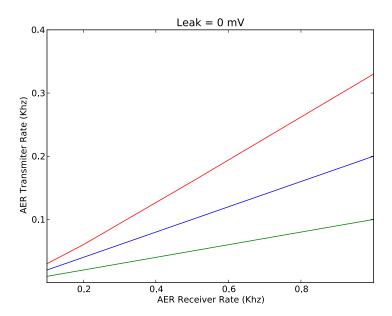

The neurons in Golden Gate support a rate coding mechanism. As the rate of AER packet receipt (firing rate stimulus) of a neuron increases, the neuron integrates faster towards its spike threshold and consequently increases its rate of AER packet transmission (firing rate response).

Three parameters (freely configurable by the user) in the neuron affect the output transmission rate given a receipt rate. These are the periodic leak (L), the firing threshold  $(\theta)$ , and the weight of the synaptic input (W). They determine the number of excitation cycles required to reach threshold. This value is  $\text{ceil}[\theta/W]$  with L=0, where ceil[x] refers to the rounding of x to the next highest integer.

For a neuron with L=0, the time between two consecutive AER output packets  $p_o$

<sup>&</sup>lt;sup>1</sup>Spike codes in biological neural circuits typically have precisions of a few milliseconds to hundreds of milliseconds. The precision of spike codes in Golden Gate is bound by the global time step of operation.

(the period of spiking) can be expressed in relation to the time between two consecutive AER input packets  $p_i$  as

$$p_o = ceil[\frac{\theta}{W}]p_i \tag{3.1}$$

The output firing rate  $f_o$  (equals  $1/p_o$ ) of the neuron is thus related to the input firing rate  $f_i$  (equals  $1/p_i$ ) as

$$f_o = ceil\left[\frac{W}{\theta}\right] \times f_i. \tag{3.2}$$

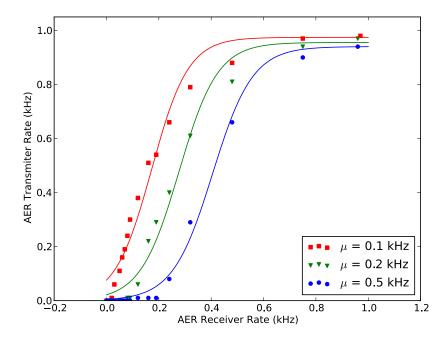

A non-zero transmission rate of a neuron with zero leak is thus linearly related to the receiver rate with a slope determined by the value of  $W/\theta$  as shown in Fig. 3.1.

The amount of traffic in the local AER routing network of a neuron affects how large its AER transmission/receipt rates can be. The maximum rate is bounded by the temporal precision (the period of the global synchronization signal of Fig. 2.3 – usually set to 1 ms) of the system.

Figure 3.1: Firing rate code with zero leak of a Golden Gate neuron. Different colors represent different values of  $W/\theta$ . Higher slopes correspond to higher ratios.

An input-independent temporal component to the neural voltage integration is added by setting a non-zero leak. In between AER inputs, there is now a decrease of the neuron voltage. The net excitation of the neuron between two consecutive excitatory synapses is  $W - (L \times p_i)$ . The number of excitatory synapses required to excite the neuron to a voltage of  $\theta$  is

$$\frac{\theta}{W - (L \times p_i)}. (3.3)$$

The number of excitatory synapses required to excite the neuron to threshold is

$$ceil\left[\frac{\theta}{W - (L \times p_i)}\right]. \tag{3.4}$$

The relationship between  $p_i$  and  $p_o$  is thus

$$p_o = ceil\left[\frac{\theta}{W - (L \times p_i)}\right] \times p_i, \tag{3.5}$$

and I/O firing rate relationship is

$$f_o = ceil\left[\frac{\theta}{W - \left(\frac{L}{f_i}\right)}\right] \times f_i. \tag{3.6}$$

As  $f_i$  changes, the slope of the  $f_o - f_i$  curve encounters discrete jumps because of the ceil[] term. For example, consider a neuron with  $\theta = 30mV$ , L = 1mV and W = 10mV that has one input. As the period of the input changes from  $p_i = 4ms$  to  $p_i = 3ms$  the number of presynaptic spikes required to excite the neuron to threshold stays at 5. However as  $p_i$  reduces further to 2ms, the number of presynaptic spikes required for a postsynaptic spike changes to 4. These abrupt changes correspond to changes in the slope of the  $p_o - p_i$  (and  $f_o - f_i$ ) curve.

Rate codes are robust to interspike-interval noise when spikes are averaged over wide time windows. Encodings over narrower windows are less tolerant because of erroneous inclusion or exclusion of spikes that may result from spike-time jitters.<sup>2</sup>

<sup>&</sup>lt;sup>2</sup>Because of the high signal-to-noise ratio of digital circuits, spike-time jitters in digital

A population of neurons can represent a vector with a firing rate code, with individual neurons representing individual components of the vector. A population rate code in Golden Gate is represented in Fig. 3.2, where a group of 8 neurons is driven by a 8-dimensional input signal.

**Figure 3.2:** Peri-stimulus time histogram illustrating population rate coding in Golden Gate. The presynaptic spike rate of each neuron is chosen from a Gaussian distribution with mean = 100 Hz, standard deviation = 50 Hz.

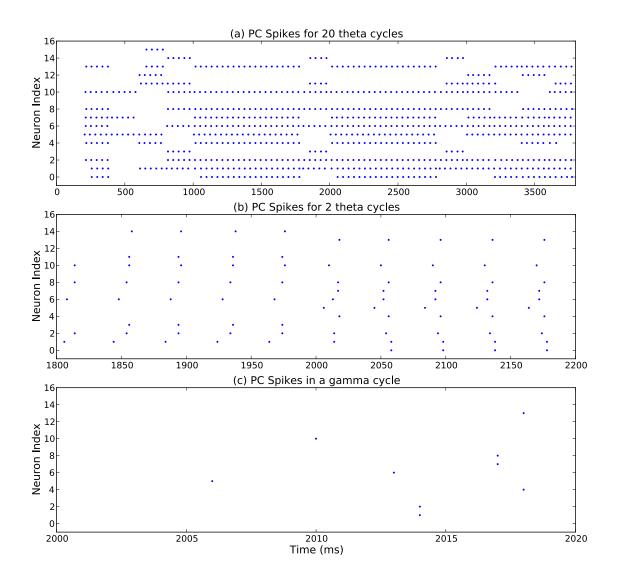

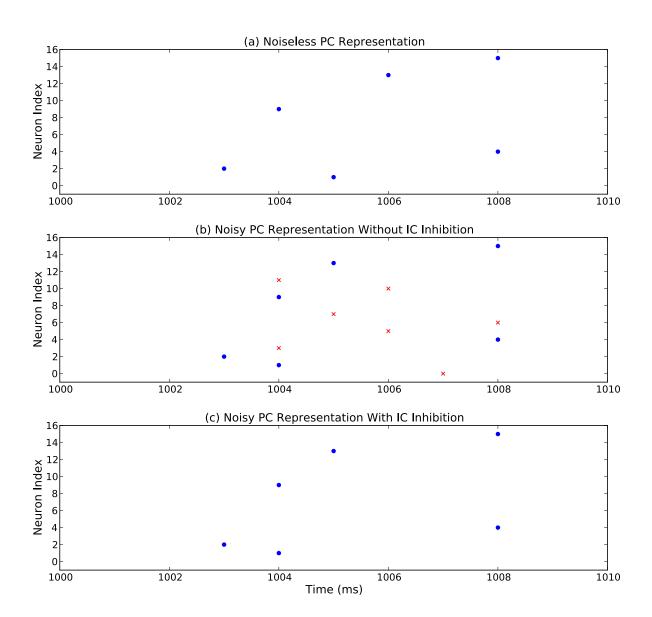

## 3.2 Temporal Codes

A temporal code enables faster and more energy-efficient processing compared to a rate code by using the precise spatiotemporal pattern of individual spikes in a population of neurons to encode information. This type of code however may have a lower tolerance to interspike interval noise especially when defined over fine timescales. Temporal codes have been observed in numerous neural circuits, such as those in the hippocampus, the olfactory bulb, and the primary visual cortex [23].

neuromorphic systems are solely from the noise associated with external signals or internal random number generators.

In Golden Gate, the timings of neuronal spikes are maintained across the system within a precision determined by the global synchronization clock (usually 1 ms). This feature, along with the neuronal leak and the axonal time delay, can be exploited for neural processing using temporal codes.

One form of a temporal code is a *latency code*. Since the strength of excitation of a Golden Gate neuron translates to how fast it integrates its interval voltage, the time  $t_s$  between the start of a stimulus and the generation of a spike can code for input strength. For a neuron with a threshold of  $\theta$ , a leak of L and one synaptic input with weight W and period  $p_i$ ,  $t_s$  (related to Eq. 3.3) can be expressed as

$$t_s = \frac{\theta}{W - (L \times p_i)} \times p_i. \tag{3.7}$$

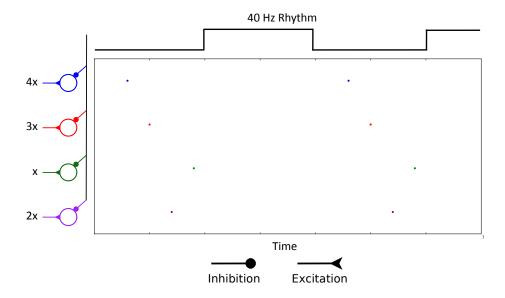

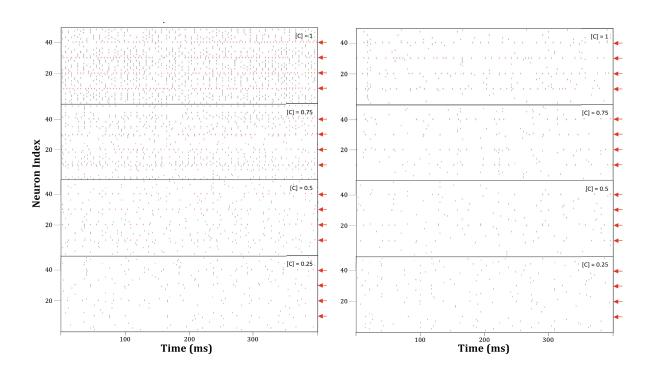

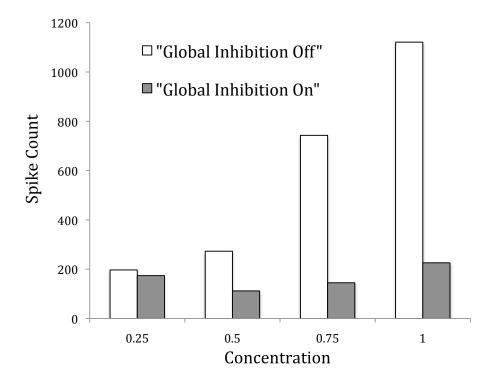

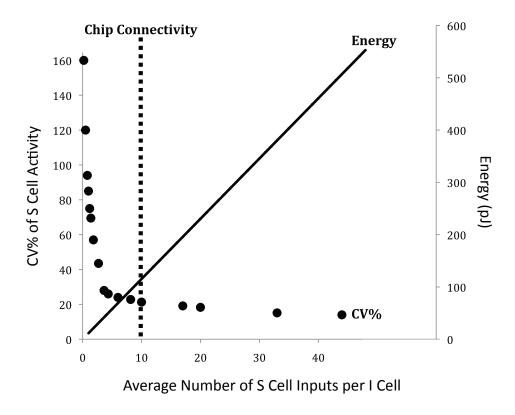

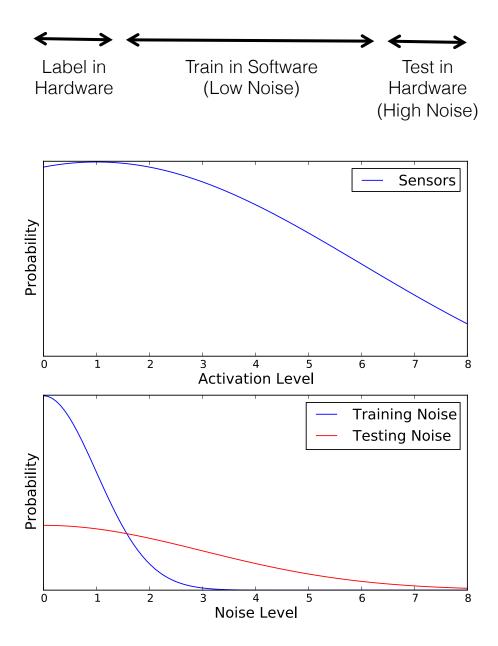

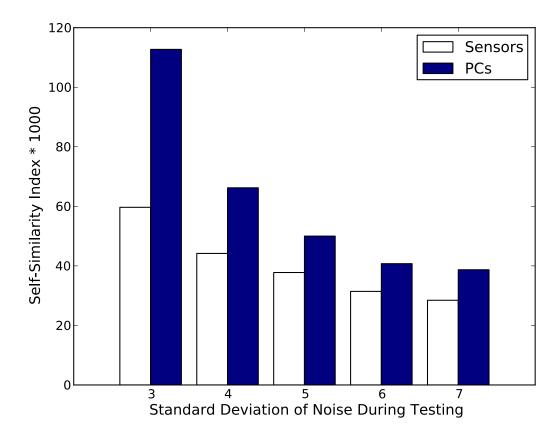

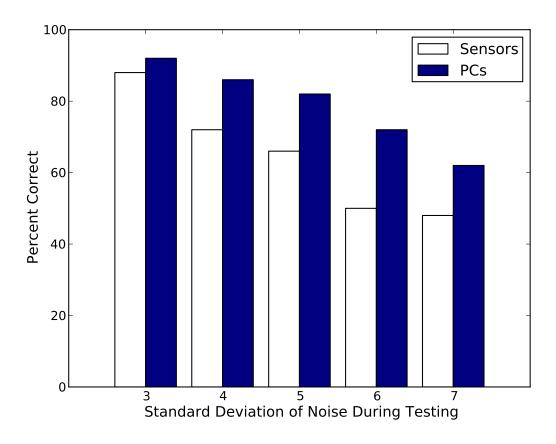

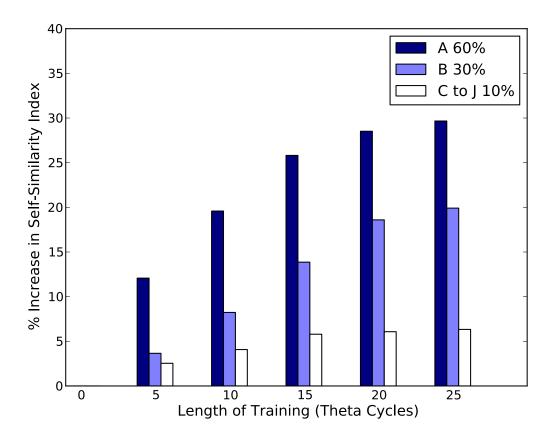

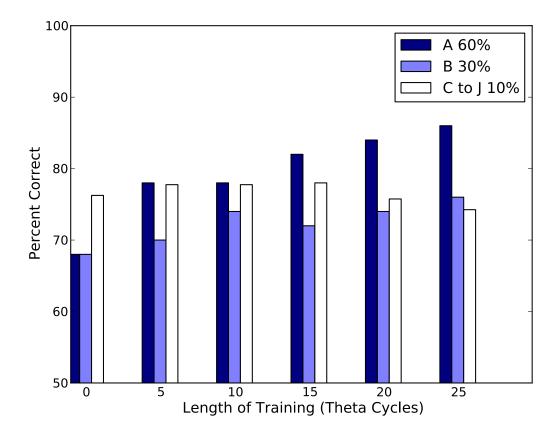

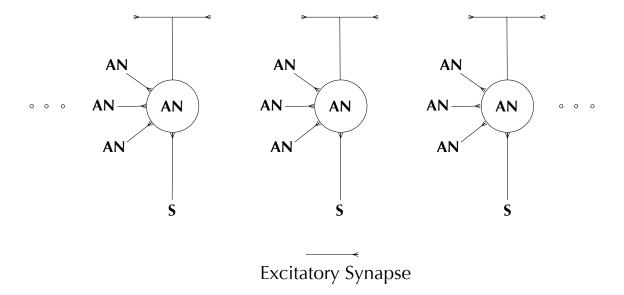

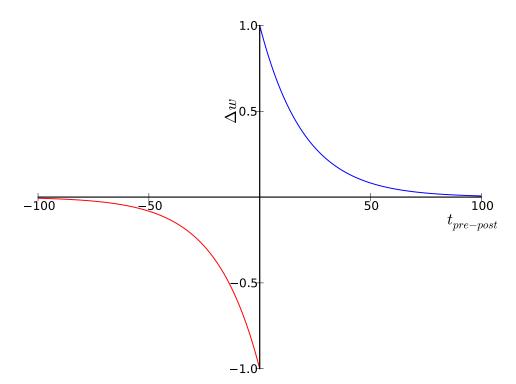

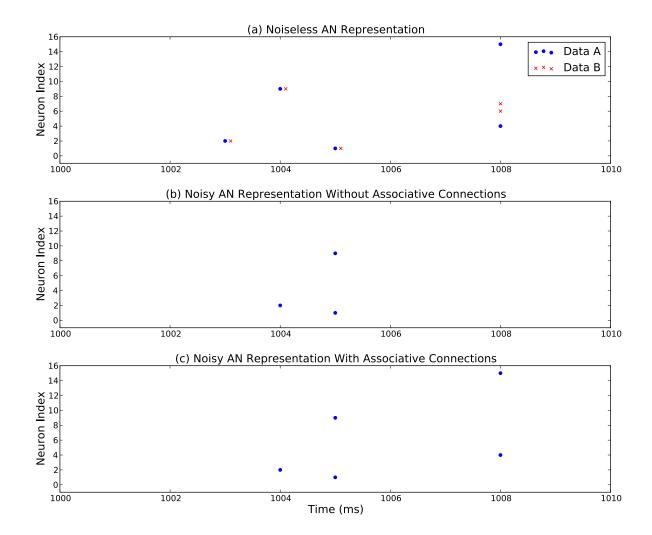

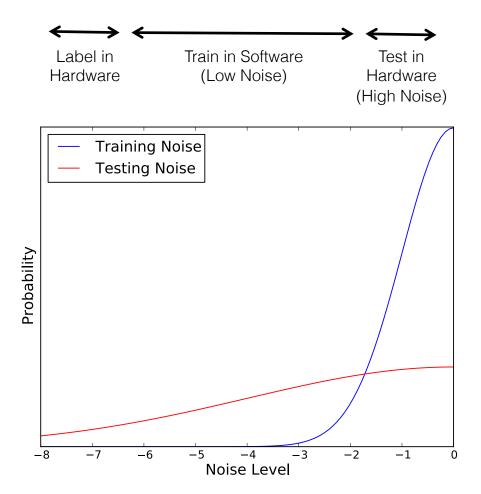

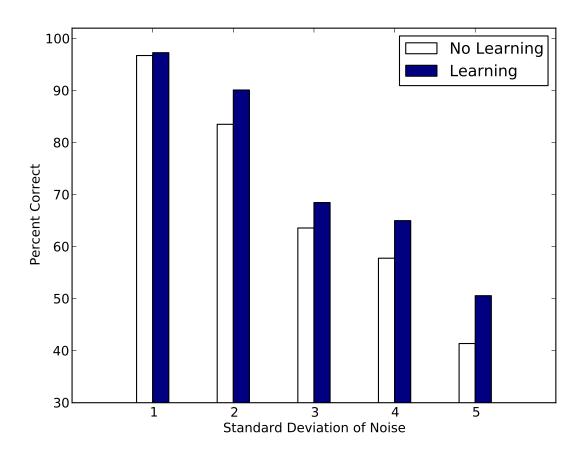

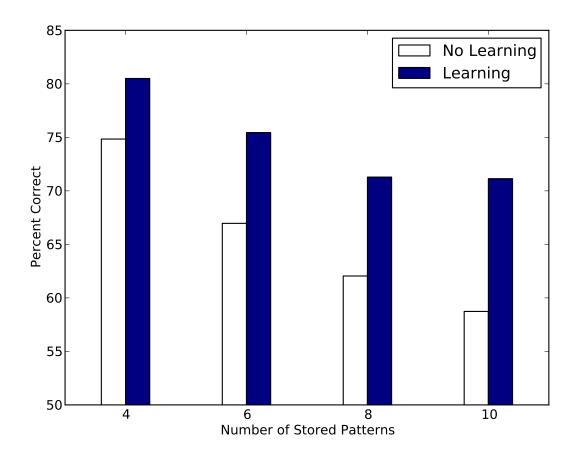

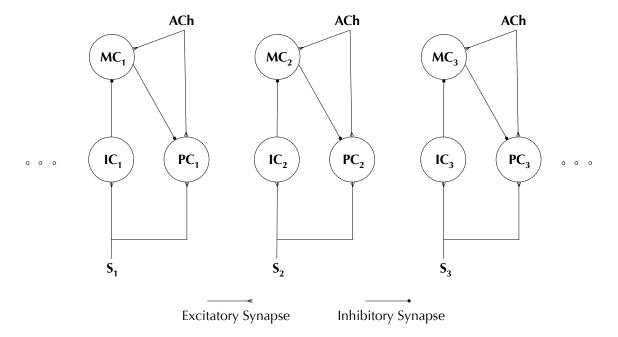

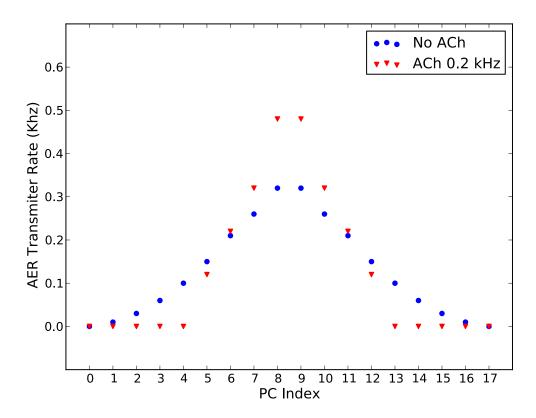

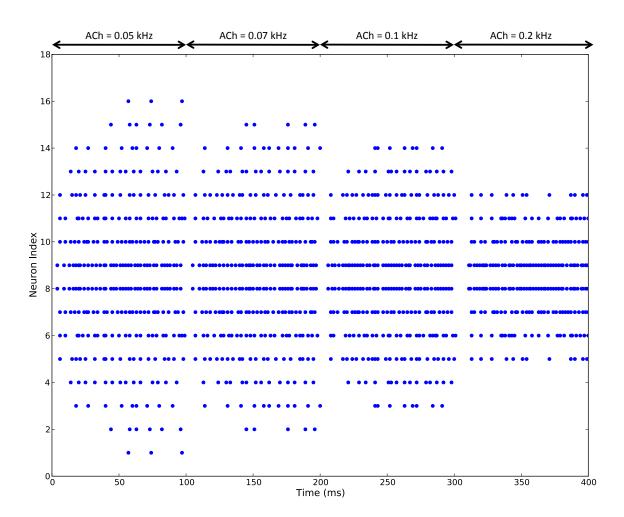

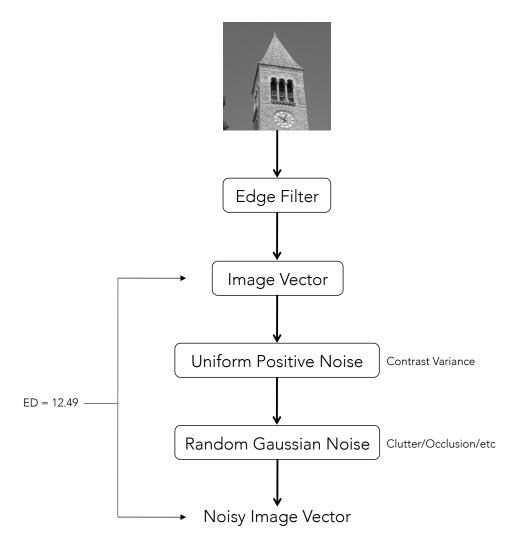

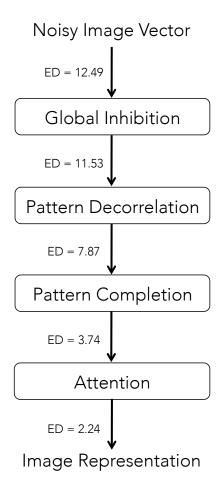

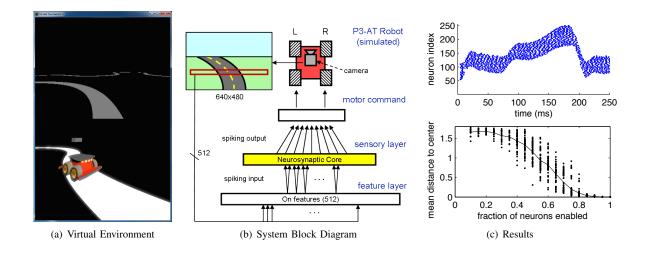

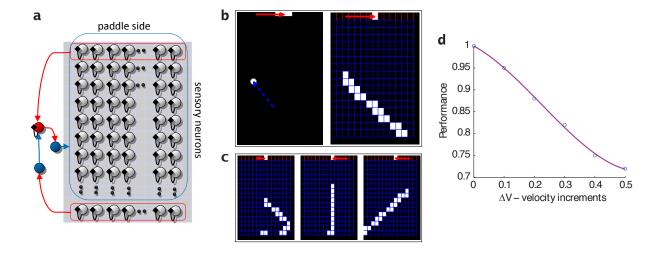

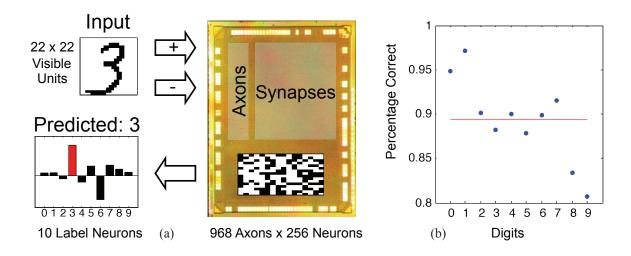

A common temporal reference frame is necessary in a population of neurons coding for a stimulus vector using latency codes. In-vivo such a reference frame may be provided for example by oscillatory potentials arising from shared interactions across a population [23]. Neurons lock their spike times to a constant phase of the oscillation that reflect their activation levels and therefore this coding scheme is also referred to as a *phase code*. One way of mimicking this mechanism in Golden Gate is by periodically driving a common inhibitory rhythm that connects to all neurons in a population and resets their voltages to zero. This implementation is illustrated in Fig. 3.3 where a rate-coded input vector is transformed into a latency code. The timing of a neuron's spike after inhibition is released is dependent on the strength of its input. Multiple spikes within one oscillation cycle from the same neuron is prevented by "handshaking" with a spiking neuron's input that results in a shut down of the input until the start of the next cycle.