# THREE-DIMENSIONAL INTEGRATION FOR FLASH MEMORY CELL

# A Dissertation

Presented to the Faculty of the Graduate School

of Cornell University

In Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by

Jaegoo Lee

August 2009

#### THREE-DIMENSIONAL INTEGRATION FOR FLASH MEMORY CELL

#### Jaegoo Lee, Ph. D.

#### Cornell University 2009

Scaling of flash memory cell structures for large-capacity nonvolatile storage will encounter serious technical challenges in lithography, disturbance and gate stack designs. An alternative way to increase the number of bits per unit chip area can be achieved by 3-D stacking of thin-film memory layers. 3-D stacking has caused different technology issues that must be overcome before it can be competitive. Due to the lack of a repeatable and affordable epitaxial growth method, the polycrystalline or amorphous thin films must be deposited with small thermal budget, good transistor quality and minimal parametric variation. The thin-film device geometry must allow reasonable scaling down to 20nm gate pitch. The electrical operation will need to minimize the power consumption and program/erase voltage to avoid reliability problems from temperature and migration due to heat dissipation and defect density concerns in 3-D integration.

In this dissertation, we propose new device solutions to support the 3-D stacking memory IC technology. We will first presents the fabrication process, material and electrical characteristics of ultra thin body (UTB) thin-film transistor (TFT) metal nanocrystal memories by using *in-situ* doped polysilicon chemical vapor deposition (CVD) followed by the chemical mechanical polishing (CMP) process, where surface roughness below 1nm is achieved. The resulting film is about 13nm thick with 10<sup>19</sup> cm<sup>-3</sup> body doping. SEM and STEM observation demonstrated that size, distribution, and density of nanocrystals could be controlled for electronic device purposes. CBED, 3D tomographic image and EELS analyses also confirmed the physical stability of the

nanocrystals. We are able to achieve memory windows of about 1.6V and 2.3V by ±6V program/erase (P/E) voltages in single and double layer NCs. From these results, it is confirmed that double layer nanocrystal memories demonstrate retention and charge density improvement over single-layer metal nanocrystals due to the increased number density of nanocrystals.

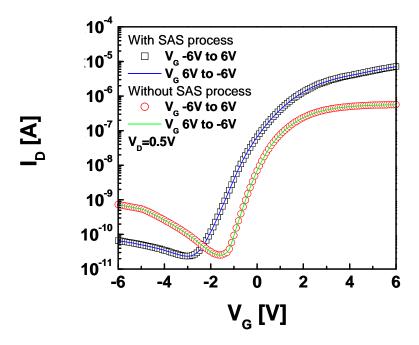

To obtain low contact resistance in the source and drain region, we then demonstrate the self-aligned silicidation (SAS) process. The device split without SAS is also shown where the source/drain resistance improvement by SAS can be clearly observed. Retention time characteristics were monitored in the  $Al_2O_3/Au/(Ti,Dy)_xO_y$  devices with Ni SAS , and were extracted to be well beyond 10 years.

Vertical integration of Ge TFT devices is another promising method to achieve 3D integration from the low processing temperature and smaller bandgap. We have obtained a memory window of about 1.8V by  $\pm 5$ V P/E voltages for UTB Ge TFT with the gate stack of Al<sub>2</sub>O<sub>3</sub>/Au/(Ti,Dy)<sub>x</sub>O<sub>y</sub> and single layer NCs. Retention characteristics were also satisfactory.

From these results, the ultra-thin planar polysilicon or Ge layer, SAS process and the gate stack design contribute to the long retention time and large memory window. Therefore, the demonstrated processes are expected to be applicable for 3D integration to meet high-density flash memory requirements.

#### BIOGRAPHICAL SKETCH

Jaegoo Lee was born in Jeonju, Jeonbuk province, South Korea on August 29, 1968 to parents Jonggeon Lee and Boksoon Baik. When he was 11 years old, his family moved to Seoul, the capital city of South Korea, where he received all his education from middle school to graduate school. In 1989, he entered Kwangwoon University in Seoul, and majored in Electronic Materials Engineering, where he developed a solid foundation in engineering and science, graduating with a B.S. degree in Feb. 1995 and a M.S. degree in Feb. 1997. His research at Kwangwoon University focused on the material growth and device fabrication of Al<sub>x</sub>Ga<sub>1-x</sub>Sb under the guidance of Professor Dong Chan Moon.

Upon completion of his M.S. program, he joined Samsung Electronics Company in Yongin, Korea and worked as a researcher with the Advanced Technology Team at the Semiconductor Research and Development Center until August 2004. His research projects at Samsung were 140nm and 90nm 1Gb (Giga bit) DRAM (Dynamic Random Access Memory).

To expand his expertise in electrical engineering, he joined the Ph.D. program at the School of Electrical and Computer Engineering at Cornell University in Ithaca, New York, U.S.A. from September 2004 to July 2009, during which time he was awarded the Samsung Fellowship for Ph.D. study from Samsung Electronics Company. At Cornell he worked with his advisor, Professor Edwin C. Kan, on three-dimensional integration flash memory with metal nanocrystals and high-k dielectric on polysilicon and Ge TFT. He has authored 29 publications and holds 13 U. S. patents in his research area.

#### **ACKNOWLEDGMENTS**

It has been five years since I joined the graduate school of Cornell University to pursue my doctoral degree. During this time, there have been many hard times but also happy times, good people and memories. I'll never be able to forget these years.

I am greatly indebted with much gratitude to my advisor, Professor Edwin C. Kan for his support and guidance during my graduate studies at Cornell. He inspired me to ask endless questions while I moved forward in my research. It has also been a great honor to have Professor George Malliaras and Professor Sunil Bhave on my Ph.D. committee. They were very generous with their time and feedback throughout the course of my experiments. I also appreciate to Professor David A. Muller and Professor R. B. van Dover for their valuable help on STEM and high-k dielectric deposition.

I deeply appreciate to Samsung R&D director Kinam Kim and Vice President Taeyoung Chung for their endless help and encouragement, and the Samsung Electronics Company for financially supporting me and my family. I would like to express special gratitude to Professor Dong Chan Moon and Professor Dong Wook Kim for their encouragement and love.

I would like to extend my thanks to Dr. Chungho Lee for his mentoring during my first year at Cornell and for teaching me all the essential clean room skills and to Dr. Cha for preparing STEM samples on planar UTB TFT. Additionally, I must thank Dr. Barron and Taro Naoi for her invaluable support with (Ti,Dy)O sputtering deposition, Dr. Raza for all the delightful chats and scientific brainstorming, and Dr. Hou for his sincere discussions and assistance during my experiments. Honestly, my research work could not have been done without the excellent support of them all.

I am grateful to my other group members: Dr. Myoungseob Kim, Dr. Udayan Ganguly, Dr. Venkat Narayanan, Dr. Jinsook Kim, Dr. Weiping Ni, and Dr. Blake

Jacquot for their assistance and advice in my early days here and to Keith Lyon, Nini Muñoz, Jonathan Shaw, Shantanu Rajwade, Xiaoyang Li, Fan Yu, Krishna Jayant, Ebenezer Kwame Amponsah, Ravneet Bajwa, Federico Garcia, Daniel Ruebusch, Sarah Xu and Joshua Phelps for their warm support and helpful advice. I also would like to thank my colleagues at Cornell, Dr. Xingqun Jiang, Dr. Young Chul Choi, Dr. Moon Kyoung Kim, Dr. Ho Young Cha, Soo Doo Chae, Professor Yongwook Park, Yuchul Jeong, Dr. Jong Bum Lee, Dr. Junghyun Hwang, Seung Yeol Lee, Sang Hyeon Lee, Seung Keun Youn and Tae Ung Sung, Jaesung Lee, Youjin Hwang, Wooram Lee, Jinseob Kim, Changhyuck Lee, Juhyung Joe, Jihyuck Park, Jin Moo Baik, Sang Ho Song, Professor Seung Jin Oh, Dr. Yongkwan Dong, Bum Seok Baik, Sung Gi Lee, Professor Manyoung Han and Professor Jooyeon Kim, for all their friendship and support. I greatly appreciate Julie Coulombe for her valuable support during my thesis review and throughout my stay in Ithaca.

I would like to acknowledge the staff members at the Cornell Nanoscale Science and Technology Facilities (CNF) and the Cornell Center for Materials Research (CCMR) for the facility maintenance and training, in particular, Michael Skvarla, Rob Ilic, Phil Infante, Darren Westly, Daniel Woodie, Garry Bordonaro, Paul Pelletier, John Grazul, Malcolm Thomas and Jerry Drumheller.

Special thanks go to many seniors and co-workers in Samsung Electronics Company - Senior Vice President Woo Seok Lee, Senior Vice President Donggun Park, Senior Vice President Kyoung Seok Oh, Vice President Hong Sik Jeong, Dr. Chang Hyun Cho, Dr. Gitae Jeong, Dr. Wonseok Yang, Dr. Kwanhyeob Koh, Kyu Hyun Lee, Byung Hyug Roh, Dr. Hyungseob Kim, Dr. Choongho Lee, Dr. Dong Won Kim, Dr. Daewon Ha, Dr. Donghwa Kwak, Dr. Yang Keun Park, Jinwoo Lee, Soo Ho Shin, Dong Jun Lee, Sang Ho Song, Ju Yong Lee, Minsang Kim, Min Hee Cho, Junghoon Oh, Yongseok Ahn and Yong Kyu Choi - for their trust and excellent

support.

To my beloved mother, Boksoon Baik, and parents-in law, Nakjun Kong and Soonbok Lim, thanks for their everlasting love. Without their positive support and cheerful encouragement, I might not have had the faith to embark on my studies five years ago. Also thanks are due my brother, sisters and their families for their warm support.

I have not enough words of gratitude to my wife Jungeun Kong for her trust, encouragement, understanding and love during these long five years. Without her sacrifice, I could not have accomplished even half of what I did. I also give my deepest thanks to my sons Donghoon and Jaehoon. Their charm and laughter have brightened my every day and made this time seem short.

# TABLE OF CONTENTS

| Biographical Ske | etch                                        | iii  |

|------------------|---------------------------------------------|------|

| Dedication       |                                             | iv   |

| Acknowledgmen    | ıts                                         | v    |

| List of Figures  |                                             | xi   |

| List of Tables   |                                             | xvi  |

| List of Abbrevia | tions                                       | xvii |

| List of Symbols  |                                             | xix  |

| CHAPTER 1:       | Introduction                                | 1    |

| 1.1 Revie        | ew of Memory Technology                     | 1    |

| 1.2 Flash        | h Memory Trend                              | 3    |

| 1.3 High         | h-k Dielectric                              | 6    |

| 1.4 Stack        | kable Flash Memory Cell for 3-D Integration | 9    |

| 1.5 Over         | view of Dissertation                        | 12   |

| REFERENC         | CES                                         | 14   |

| CHAPTER 2: 3-    | D INTEGRATION FLASH MEMORY CELL             | 20   |

| 2.1 Plane        | ar Polysilicon UTB TFT Cell                 | 20   |

| 2.1.1            | Motivation                                  | 20   |

| 2.1.2            | The Concept of Ultra-Thin Body TFT          | 21   |

| 2.1.3            | CMP Process                                 | 24   |

| 2.2 Ni S         | ilicidation                                 | 30   |

| 2.2.1            | Motivation                                  | 30   |

| 2.2.2            | Nickel Silicide (NiSi) Formation            | 31   |

|      | 2.3 | Ge T     | hin Film Transistor (TFT)                                                               | 34  |

|------|-----|----------|-----------------------------------------------------------------------------------------|-----|

|      |     | 2.3.1    | Ge Oxide Treatment                                                                      | 34  |

|      |     | 2.3.2    | High-k/Ge Gate Stack                                                                    | 37  |

|      | 2.4 | Nano     | crystal Floating-Gate Memory with High-k Tunneling Barrier                              | 42  |

|      | REI | FERENC   | CES                                                                                     | 44  |

|      |     |          |                                                                                         |     |

| СНА  | PTE | ER 3: P  | LANAR POLYSILICON TFT WITH Au NC AND HIGH                                               | H-K |

| DIEI | LEC | TRICS    |                                                                                         | 50  |

|      | 3.1 | Motiv    | vation                                                                                  | 50  |

|      | 3.2 | Polys    | rilicon TFT with Single Au NC and (Ti,Dy) <sub>x</sub> O <sub>y</sub> High-k Dielectric | 51  |

|      |     | 3.2.1    | Device Fabrication and Material Characterization                                        | 51  |

|      |     | 3.2.2    | Electrical Characterization                                                             | 57  |

|      | 3.3 | Polys    | rilicon TFT with Single Au NC and Al <sub>2</sub> O <sub>3</sub> High-k Dielectric      | 59  |

|      |     | 3.3.1    | Device Fabrication and Material Characterization                                        | 59  |

|      |     | 3.3.2    | Electrical Characterization                                                             | 63  |

|      | 3.4 | Polys    | cilicon TFT using Double Au NC and $Al_2O_3$ High-k Dielectric                          | 65  |

|      |     | 3.4.1    | Device Fabrication and Material Characterization                                        | 65  |

|      |     | 3.4.2    | Electrical Characterization                                                             | 68  |

|      | REI | FERENC   | CES                                                                                     | 72  |

|      |     |          |                                                                                         |     |

| СНА  | PTE | ER 4: FI | ULL SILICIDATION PROCESS                                                                | 76  |

|      | 4.1 | Moti     | vation                                                                                  | 76  |

|      | 4.2 | Devic    | ce Fabrication and Material Characterization                                            | 76  |

|      | 4.3 | Elect    | rical Characterization                                                                  | 78  |

|      | REI | FERENC   | CES                                                                                     | 83  |

| CHAPTER  | 5: PLANAR Ge TFT FLASH MEMORY CELL               | 86  |

|----------|--------------------------------------------------|-----|

| 5.1      | Motivation                                       | 86  |

| 5.2      | Device Fabrication and Material Characterization | 87  |

| 5.3      | Electrical Characterization                      | 90  |

| REFEREN  | CES                                              | 95  |

|          |                                                  |     |

| CHAPTER  | 6: CONCLUSIONS AND FUTURE WORK                   | 98  |

| 6.1      | Conclusions                                      | 98  |

| 6.2      | Future work                                      | 99  |

| REFEREN  | CES                                              | 101 |

|          |                                                  |     |

| APPENDIX | X 1                                              | 103 |

| APPENDIX | X 2                                              | 109 |

| APPENDIX | X 3                                              | 115 |

# LIST OF FIGURES

| Figure 1.1 | ITRS roadmap for NAND flash transistor                                                                     |

|------------|------------------------------------------------------------------------------------------------------------|

| Figure 1.2 | Schematic cross section of a floating-gate memory device                                                   |

| Figure 1.3 | Energy band diagram of floating gate memory cell at (a) equilibrium                                        |

|            | enlarged conduction band edge of floating gate/tunneling barrier                                           |

|            | substrate at (b) programming and (c) erase states                                                          |

| Figure 2.1 | Vertical structures (schematics of (a) Samsung and (b) Toshiba) or                                         |

|            | promising candidates for 3-dimensional (3-D) integration of flash                                          |

|            | memory cells                                                                                               |

| Figure 2.2 | Schematics and channel potentials of (a) conventional TFT without                                          |

|            | CMP and (b) the proposed CMP processes23                                                                   |

| Figure 2.3 | (a) Schematic of chemical mechanical (CMP) process and (b)                                                 |

|            | experimental apparatus of CMP process                                                                      |

| Figure 2.4 | AFM results according to CMP factors                                                                       |

| Figure 2.5 | The schematic of CMP process and statistical distribution of thickness                                     |

|            | (a) After polsilicon deposition, (b) without the HF dip process, (c) with                                  |

|            | the HF dip process and (d) after polysilicon CMP processOxide electric                                     |

|            | field at the SiO <sub>2</sub> /Si interface and tunneling current density into NCs as                      |

|            | a function of the NC spacing                                                                               |

| Figure 2.6 | Schematic diagrams for nickel silicide formation between in Ni and                                         |

|            | polysilicon                                                                                                |

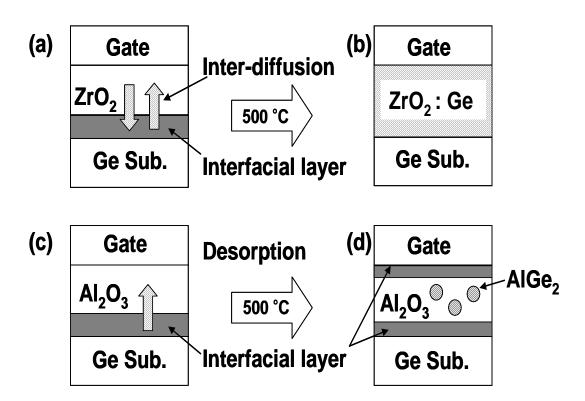

| Figure 2.7 | Schematic on the effect of annealing on ZrO <sub>2</sub> /Ge gate stack (a, b) and                         |

|            | Al <sub>2</sub> O <sub>3</sub> /Ge gate stack (c, d)                                                       |

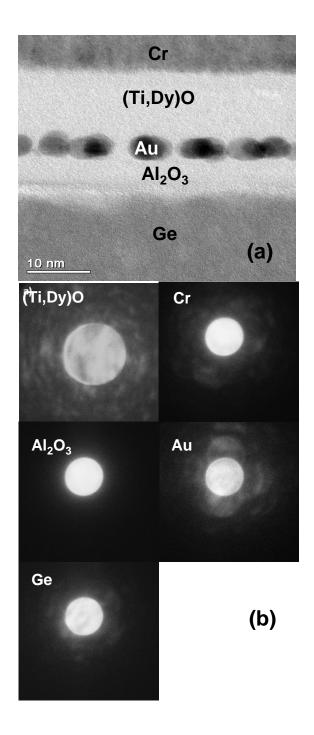

| Figure 2.8 | (a) BF-STEM image of a single NC layer embedded in the Ge gate                                             |

|            | stack, (b) CBED pattern of Al <sub>2</sub> O <sub>3</sub> layer at Al <sub>2</sub> O <sub>3</sub> /Ge gate |

|            | stack40                                                                                         |

|------------|-------------------------------------------------------------------------------------------------|

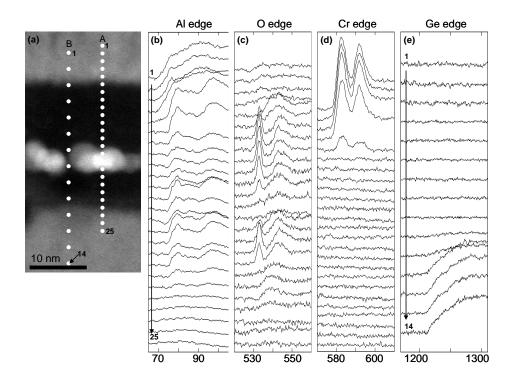

| Figure 2.9 | (a) DF-STEM image of a single layer Au NCs Ge TFT gate stack, (b)                               |

|            | Al EELS edge (taken from line A), (c) O EELS edge (taken from line                              |

|            | A), (d) Cr EELS edge (taken from line A), and (d) Ge EELS edge                                  |

|            | (taken from line B)41                                                                           |

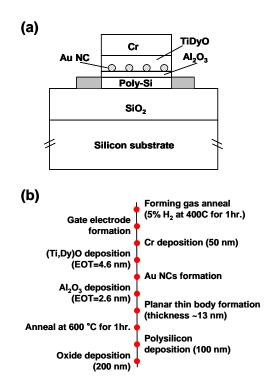

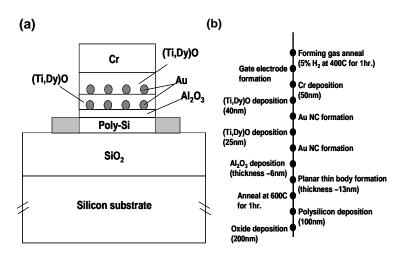

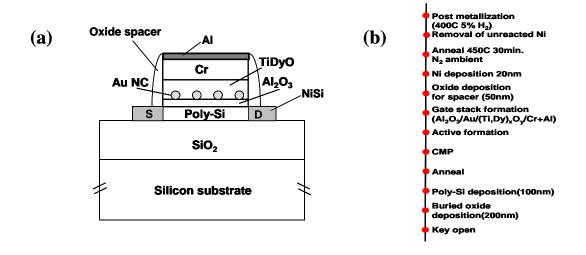

| Figure 3.1 | (a) Vertical device schematics of a UTB TFT memory with metal NC                                |

|            | charge storage and (Ti,Dy) <sub>x</sub> O <sub>y</sub> tunneling barriers and (b) the main      |

|            | process sequence                                                                                |

| Figure 3.2 | The polysilicon removal rate and standard deviation of the film                                 |

|            | thickness under different CMP conditions                                                        |

| Figure 3.3 | $3~\mu m \times 3~\mu m$ AFM images of polysilicon thin film: (a) before CMP and                |

|            | (b) after CMP54                                                                                 |

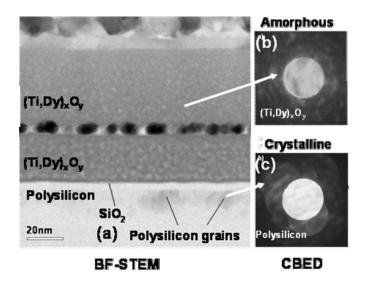

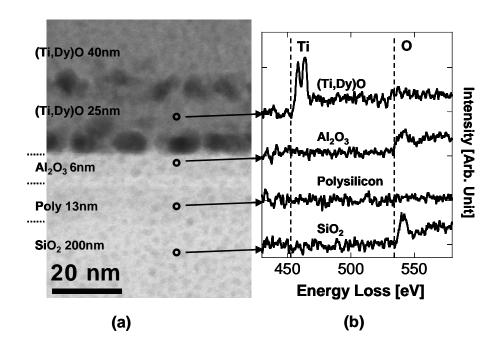

| Figure 3.4 | (a) BF-STEM image of a single NC layer embedded in the (Ti,Dy) <sub>x</sub> O <sub>y</sub>      |

|            | gate stack, CBED patterns of (b) (Ti,Dy) <sub>x</sub> O <sub>y</sub> layer, and (c) polysilicor |

|            | layer                                                                                           |

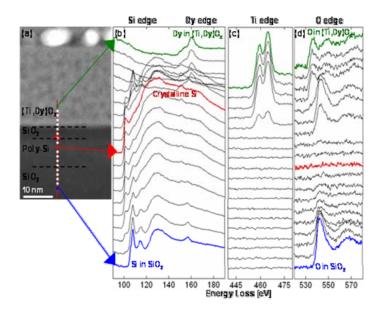

| Figure 3.5 | (a) DF-STEM image of a Au NC TFT gate stack with a (Ti,Dy)O layer                               |

|            | (b) Si and Dy EELS edge, (c) Ti EELS edge, and (d) O EELS                                       |

|            | edge                                                                                            |

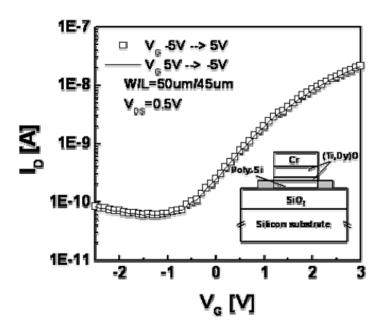

| Figure 3.6 | Lack of memory window in control polysilicon TFT without Au NC                                  |

|            | $W/L = 50 \ \mu \text{m} / 45 \ \mu \text{m}$                                                   |

| Figure 3.7 | Output characteristics of the $(Ti,Dy)_xO_y/Au/(Ti,Dy)_xO_y$ TFT                                |

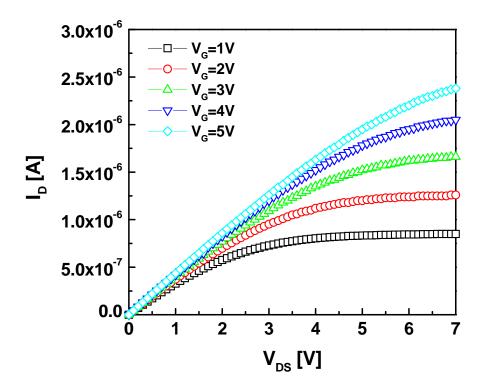

|            | device58                                                                                        |

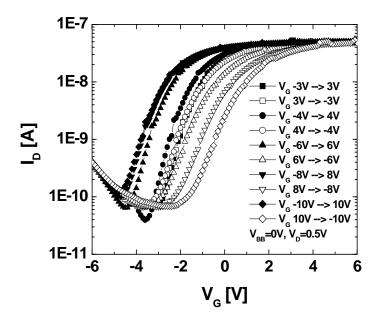

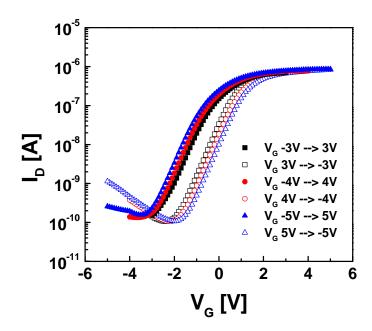

| Figure 3.8 | Transfer characteristics with gate voltage sweeps for (Ti,Dy) <sub>x</sub> O <sub>y</sub>       |

|            | Au/(Ti,Dy) <sub>x</sub> O <sub>y</sub> TFT flash memory cells                                   |

| Figure 3.9 | (a) Vertical device schematics of a UTB TFT memory with metal NC                                |

|            | charge storage and Al <sub>2</sub> O <sub>3</sub> tunneling barriers and (b) the main process   |

|             | sequence                                                                                                               |

|-------------|------------------------------------------------------------------------------------------------------------------------|

| Figure 3.10 | BF-STEM image of single Au NCs TFT gate stack embedded in                                                              |

|             | $Al_2O_3/(Ti,Dy)_xO_y$ layers60                                                                                        |

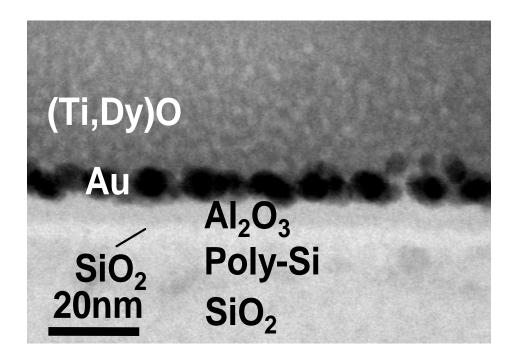

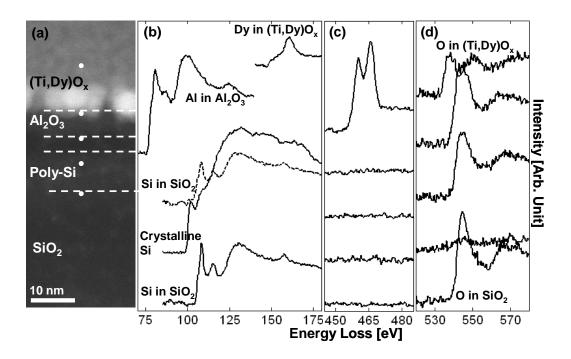

| Figure 3.11 | (a) DF-STEM image of single Au NCs TFT gate stack embedded in                                                          |

|             | Al <sub>2</sub> O <sub>3</sub> /(Ti,Dy) <sub>x</sub> O <sub>y</sub> layers, (b) Dy EELS edge, (c) Ti EELS edge and (d) |

|             | O EELS edge (taken from line A)                                                                                        |

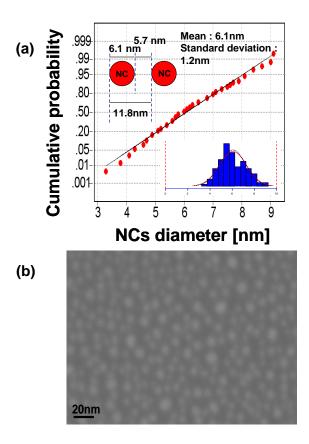

| Figure 3.12 | (a) Size distribution of Au NCs deposited by e-beam evaporator on                                                      |

|             | ALD Al <sub>2</sub> O <sub>3</sub> and (b) an SEM image62                                                              |

| Figure 3.13 | Lack of memory window in control polysilicon TFT without Au NC                                                         |

|             | $(W/L = 50 \ \mu m/45 \ \mu m)$                                                                                        |

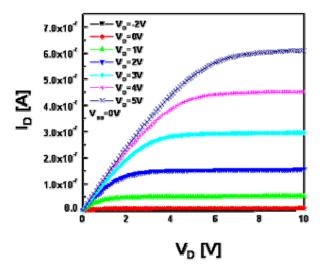

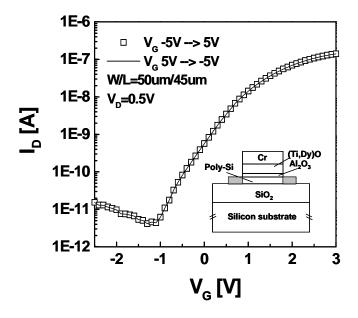

| Figure 3.14 | Output characteristics of Al <sub>2</sub> O <sub>3</sub> /Au/(Ti,Dy) <sub>x</sub> O <sub>y</sub> TFT device64          |

| Figure 3.15 | Transfer characteristics with gate voltage sweeps for Al <sub>2</sub> O <sub>3</sub> /Au/                              |

|             | (Ti,Dy) <sub>x</sub> O <sub>y</sub> TFT flash memory cells                                                             |

| Figure 3.16 | (a) Structure and (b) process sequence of a double-layer nanocrystal                                                   |

|             | TFT memory66                                                                                                           |

| Figure 3.17 | (a) STEM image of the double-layer Au NCs TFT gate stack. (b) Ti                                                       |

|             | EELS edge appears at 455 eV while O edge appears at ~525 eV. Si                                                        |

|             | edge was also observed, but not shown here                                                                             |

| Figure 3.18 | (a) Transfer and conductance characteristic of polysilicon TFT, (b)                                                    |

|             | transfer characteristics of lack of memory window in control TFT                                                       |

|             | without Au NC. ( $W/L = 50 \mu m/45 \mu m$ )                                                                           |

| Figure 3.19 | Output characteristics of polysilicon TFT with double layer NCs70                                                      |

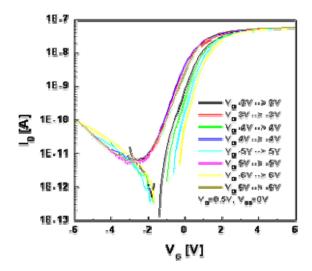

| Figure 3.20 | Transfer characteristics with gate voltage sweeps for Au double NCs                                                    |

|             | layer TFT flash memory cells70                                                                                         |

| Figure 3.21 | Retention time for TFT flash memory cells with single- and double-                                                     |

|             | NCs gate stack71                                                                                                       |

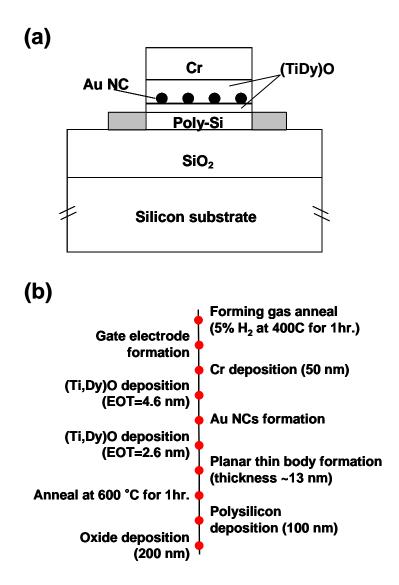

| Figure 4.1 | (a) Vertical structure of Au NCs embedded in Al <sub>2</sub> O <sub>3</sub> /(Ti,Dy)O gate |

|------------|--------------------------------------------------------------------------------------------|

|            | stacks on SAS polysilicon TFT and (b) process sequences using SAS                          |

|            | process                                                                                    |

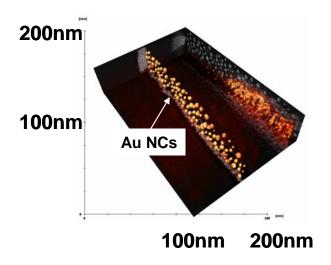

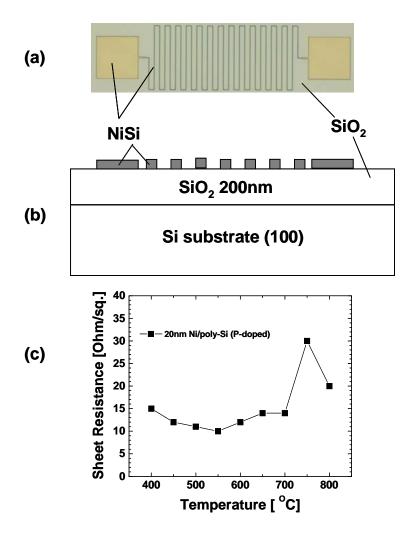

| Figure 4.2 | 3-D tomographic image of self-assembled Au NCs                                             |

| Figure 4.3 | (a) Test pattern for sheet resistance measurement of NiSi film after                       |

|            | annealing, (b) the cross section of the test structure and (c) sheet                       |

|            | resistance of the NiSi film of 13 nm thickness after various annealing                     |

|            | temperatures                                                                               |

| Figure 4.4 | Lack of memory window in control FUSI polysilicon TFT without Au                           |

|            | NC. W/L=50μm /45μm using SAS process80                                                     |

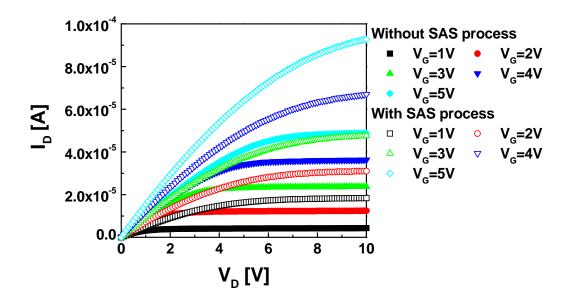

| Figure 4.5 | Output characteristics of polysilicon TFT with and without SAS                             |

|            | process                                                                                    |

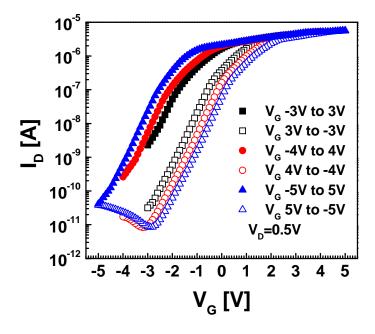

| Figure 4.6 | Transfer characteristics with gate voltage sweeps for Au NCs TFT flash                     |

|            | memory cells using SAS process with various voltage sweep                                  |

|            | ranges81                                                                                   |

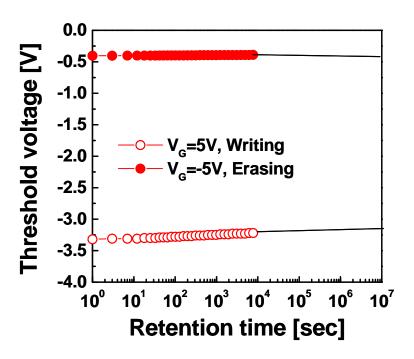

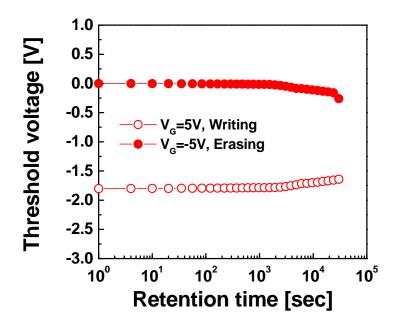

| Figure 4.7 | Retention time for Au NCs TFT flash memory cells using SAS process                         |

|            | under 5V writing and -5V erasing conditions                                                |

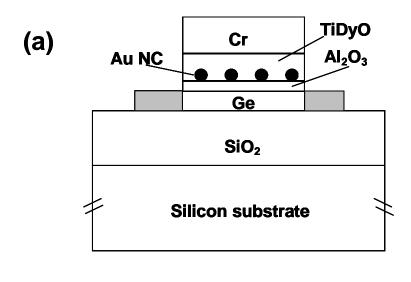

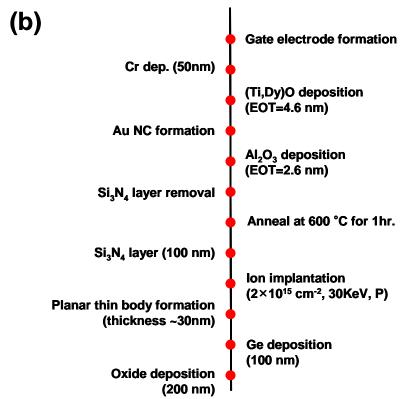

| Figure 5.1 | (a)Vertical structure of Au NCs embedded in Al <sub>2</sub> O <sub>3</sub> /(Ti,Dy)O gate  |

|            | stacks on Ge TFT and (b) process sequences Ge TFT process88                                |

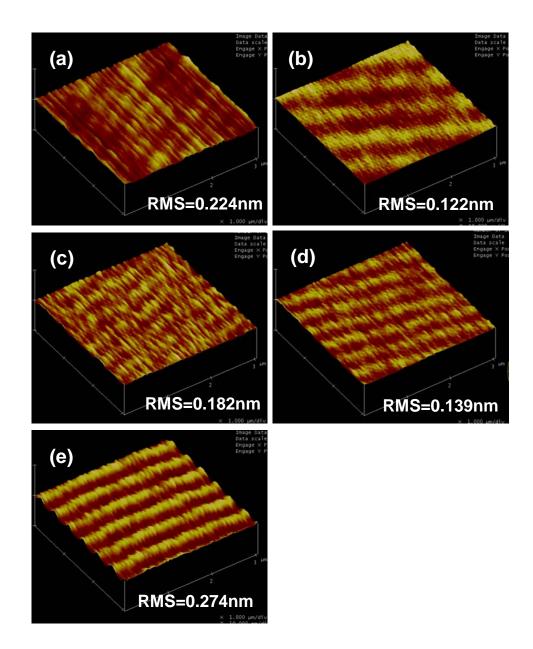

| Figure 5.2 | 3 $\mu m \times$ 3 $\mu m$ AFM images of Ge thin film: (a) as-deposited without            |

|            | CMP, (b) with CMP, 4psi-15RPM-15RPM (back pressure-table                                   |

|            | rotation speed-chuck rotation speed), (c) 4psi-25RPM-15RPM, (d)                            |

|            | 4psi-15RPM-25RPM and (e) 4psi-25RPM-25RPM89                                                |

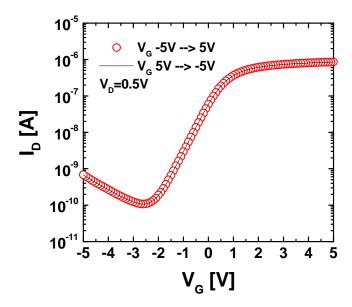

| Figure 5.3 | Lack of memory window in control Ge TFT without Au NC (W/L=50                              |

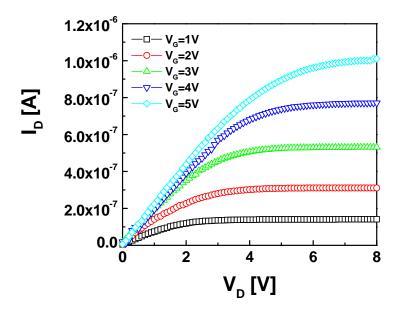

|            | μm /45 μm)91                                                                               |

| Figure 5.4 | Output characteristics of the planar Ge TFT 91                                             |

| Figure 5.5 | Transfer characteristics with gate voltage sweeps for Ge TFT flash                    |

|------------|---------------------------------------------------------------------------------------|

|            | memory cells with Au NCs92                                                            |

| Figure 5.6 | Retention time for Ge TFT flash memory cells with Al <sub>2</sub> O <sub>3</sub> /Au/ |

|            | (Ti,Dy) <sub>x</sub> O <sub>y</sub> gate stack93                                      |

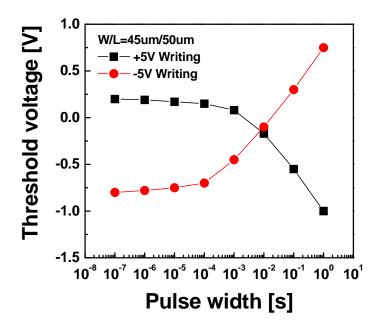

| Figure 5.7 | Write/erase time test of Au nanocrystal Ge TFT at ±5V93                               |

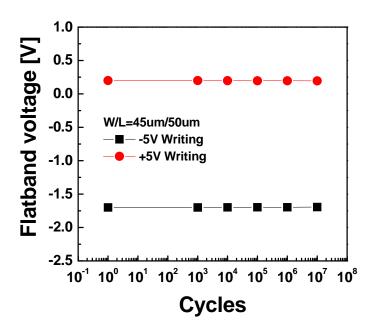

| Figure 5.8 | Cycle endurance characteristics of Au nanocrystal Ge TFT at                           |

|            | ±5V94                                                                                 |

# LIST OF TABLES

| Table 1.1 | Material characteristics of high-k dielectric                       | 7  |

|-----------|---------------------------------------------------------------------|----|

| Table 2.1 | Chemical mechanical polishing condition                             | .7 |

| Table 2.2 | The material characteristics of promising channel materials Chemica | al |

|           | mechanical polishing condition                                      | 5  |

| Table 2.3 | Material characteristics of Ge oxides and Si dioxide                | 6  |

| Table 3.1 | The CMP process chosen in this study for the UTB TFT 5              | 3  |

| Table 3.2 | The statistical parameters of Au NCs                                | 4  |

#### LIST OF ABBREVIATIONS

3-D Three-Dimensional

AFM Atomic Force Microscopy

ALD Atomic Layer Deposition

BF-STEM Bright-Field Scanning Transmission Electron Microscopy

BiCS Bit-Cost Scalable

BJT Bipolar Junction Transistor

CBED Convergent Beam Electron Diffraction

CMOS Complementary Metal-Oxide-Semiconductor

CMP Chemical Mechanical Polishing

CNF Cornell Nanoscale science and technology Facility

CNS Center for Nanoscale Systems

CVD Chemical Vapor Deposition

DIBL Drain Induced Barrier Lowing

DRAM Dynamic Random Access Memory

DF-STEM Dark-Field Scanning Transmission Electron Microscopy

EELS Electron Energy Loss Spectra

EOT Equivalent Oxide Thickness

EUV Extreme Ultra-Violet

FET Field Effect Transistor

FN Fowler-Nordheim

FRAM Ferroelectric Random Access Memory

GOI Ge-On-Insulator

ITRS International Technology Roadmap for Semiconductor

LOR Lift-Off Resist

MRAM Magnetoresistive Random Access Memory

MOS Metal-Oxide-Semiconductor

NCs Nanocrystals

P/E Program/Erase

PECVD Plasma Enhanced Chemical Vapor Deposition

RF Radio Frequency

RMS Root Mean Square

RPM Rotation Per Minute

Single-crystal Si layer Stacking

SAS Self-Aligned Silicidation

SEC Samsung Electronics Company

SEM Scanning Electron Microscopy

STEM Scanning Transmission Electron Microscopy

SOI Silicon-On-Insulator

SONOS Silicon-Oxide-Nitride-Oxide-Silicon

TEC Toshiba Electronics Company

TFT Thin-Film Transistor

ULSI Ultra Large Scale Integration

UTB Ultra-Thin Body

# LIST OF SYMBOLS

a Lattice constant

$dlog (I_d)$  Differential log drain current

$dV_g$  Differential gate voltage

$E_{C FG}$  Floating gate conduction band energy level

$E_{C sub}$  Substrate conduction band energy level

$E_g$  Energy bandgap

FG Floating gate

*I*<sub>dsat</sub> Maximum drive current

$I_{off}$  Off state drain current

$I_{ON}$  Drive current

$J_g$  Gate leakage current density

*k* Dielectric constant

$N_C$  Effective density of states in conduction band,

$N_V$  Effective density of states in valence band,

Sub-threshold slopes

$T_m$  Melting point

$V_{CG}$  Control gate volatge

$V_{DS}$  Drain-source voltage

$V_{GS}$  Gate-source voltage

$V_T$  Threshold voltage

$e^{-}$  Electron

*χ* Electron affinity

$\mu_{e}/\mu_{h}$  Electron mobility/ Hole mobility

# CHAPTER 1

#### **INTRODUCTION**

## 1.1 Review of Memory Technology

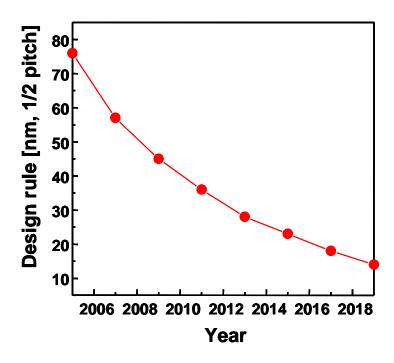

The semiconductor industry has been steadily growing since the development of the first integrated circuits. Metal-oxide-semiconductor (MOS) devices continue to be scaled to achieve the basic goals of VLSI semiconductor manufacturers. As a result, the number of transistors on a chip has doubled every two years and it is predicted that this trend will continue until 2018 [1]. According to the International Technology Roadmap for Semiconductor (ITRS), it is anticipated that gate length will be scaled down to 32 nm by the year 2011 as shown in Figure 1.1 [2].

**Figure 1.1** ITRS roadmap for NAND flash transistors.

During the next decade, device scaling challenges are expected to proliferate. The most severe problems include lithography, process integration and control, gate oxide thickness scalability, increased parasitic capacitance and resistance, novel material integration, and escalating development cost and time. Ever-increasing scaling demands and decreasing operational voltage also make it difficult to develop high-performance memory devices with faster read/write, longer retention, higher endurance, lower voltage/power operation, and higher density [3].

The solid-state memories can be categorized as volatile and nonvolatile memories according to their data retention capabilities. A typical volatile memory, dynamic random access memory (DRAM), which consists of one transistor and one capacitor, offers very high density and low cost per bit, but requires periodic refreshing or rewriting due to short retention time [4].

In contrast to the volatile high-speed memory of DRAM, flash memory can retain its data for at least 10 years without a power supply. However, its slow write/erase operations, limited endurance, and poor scaling require further improvement and new technologies [5-7].

Ferroelectric random access memory (FRAM) has been introduced as a potential replacement for the flash memory [8-12]. However, problems such as poor reliability due to fatigue [13] and imprint [14] of PZT, as well as poor scaling and high fabrication costs, need to be resolved before FRAM can be a viable alternative in the memory market. Another candidate is the magnetic random access memory (MRAM) [15-20]. Here, fabrication issues such as CMOS compatibility of magnetic materials and tight thickness control of the tunnel junction insulator are the main challenges [21]. Phase-change random access memory (PRAM) is another resistance-change-based memory similar to MRAM [22-26]. As the scaling proceeds, potential concerns

regarding thermal disturbance to adjacent bits must be addressed. [27]. In summary, even though new technologies are emerging, thus far none has proved to be the competitive substitute for conventional flash memories.

Despite enormous challenges facing the development of memory devices, the continuous improvement of flash memory in terms of fabrication, structural design, and operational schemes has strengthened their competitiveness in the market. However, reliability concerns accompanied by the aggressive scaling-down of the device geometries in order to achieve high density remain the primary obstacles for the future of the charge-storage-based approach.

#### 1.2 Flash Memory Trend

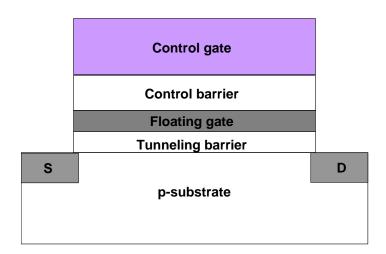

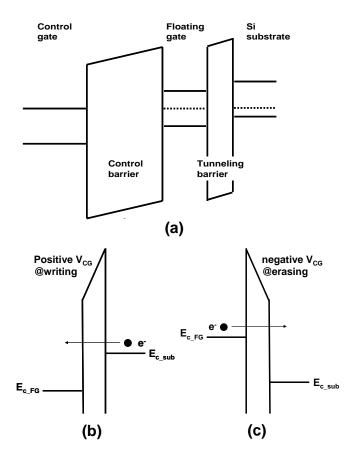

The floating gate structure has been most popularly used for the nonvolatile memory application, as first proposed by S. M. Sze of the Bell Labs [28]. The schematic cross section of a floating-gate memory device is shown in Figure 1.2.

Figure 1.2 Schematic cross section of a floating-gate memory device

The upper gate in Figure 1.2 is the control gate, and the lower gate, which is completely isolated by dielectrics, is the floating gate. This floating gate acts as a potential well. Once the charges are injected into the potential well, they can hardly escape without an external electric field. In this device structure, the programming and erasing of the memory cell are implemented by applying a positive and negative electric field to the control gate, respectively, as shown in the band diagram in Figure 1.3.

**Figure 1.3** Energy band diagram of floating gate memory cell at (a) equilibrium, enlarged conduction band edge of floating gate/tunneling barrier/substrate at (b) programming and (c) erase states.

Therefore, programming and erasing operations depend not only on the applied electric field, but also on the tunneling current through the dielectric between the floating gate and the substrate, namely the tunneling barrier. For this reason, it is very important to scale down the tunneling barrier both for the low voltage and high speed operation of the memory cell by providing enough tunneling current [29]. However, the scaling down of the tunneling barrier is severely limited. For instance, the data retention characteristics which are also determined by the tunneling current (leakage current in this case) with zero gate bias must be considered in order for the memory cell to provide sufficient nonvolatility.

In conventional floating gate structure, percolation defects in the tunneling barrier will result in the whole charge loss. Similarly, charge losses along the lateral path to the source and drain can be a serious problem [30]. Moreover, the electrostatic potential is very high in the floating gate structure when the memory cell is programmed, resulting in high leakage current through the tunneling dielectric. These various leakage sources induce significant charge losses in the memory cell, resulting in the degradation of data retention. This trade-off between programming efficiency and data retention has been a fundamental limitation in scaling down the tunneling barrier. For that reason, nanocrystal floating-gate structure was introduced to overcome scaling limitation [31].

Because the nanocrystal floating gate structure has every nanocrystal electrically and physically separated in the cell, the local defects in the tunneling dielectric and/or the leakage current through the lateral path to the source and drain may cause the charge loss of only one or a few nanocrystals, maintaining the stored charges in the rest [32].

#### 1.3 High-k Dielectric

There are two basic types of device scaling strategies in MOSFET logic technology: constant field scaling and constant voltage scaling, although in practice they are often used in a mixed manner to give the best overall performance and compatibility. In order to understand the device scaling factor on critical device operations, we will need to establish a minimalistic set of design parameters. When a MOSFET is turned on, the key electrical parameters are  $I_{dsat}$  (maximum drive current),  $V_T$  (threshold voltage), and the DIBL (Drain Induced Barrier Lowing) effect that changes the threshold voltage and self gain. When turned off, the parameters are  $I_{off}$  (off state drain current) and the sub-threshold swing ( $dV_g/dlog(I_d)$ ), which is also affected by DIBL.

These on/off characteristics should be closely monitored when the MOSFET device is scaled down. In order to achieve the required turn-off characteristics, the gate oxide thickness, source drain junction depth, and operating voltage must be decreased. In the 2007 ITRS road map [2], the required gate oxide thickness for 32 nm transistor is 0.5 - 1.0 nm. But in this thickness range, direct tunneling is dominant for SiO<sub>2</sub>, which means that silicon oxide leakage can be greater than 10 A/cm<sup>2</sup>. This is not an acceptable level for standby power consumption. Furthermore, the absolute scaling limit of pure silicon dioxide is believed to be 7 Å, since the wave length penetration effect is 3.5 Å for each surface of silicon dioxide [28]. Therefore, SiO<sub>2</sub> films less than 7 Å will hardly function as an insulator. SiO<sub>2</sub> has been used in the MOSFET process for more than 30 years due to its superior chemical stability, outstanding thermal stability, excellent dielectric performance, low interface state densities, diffusion barrier properties, low leakage current and good reliability performance. When we consider the selection of an alternative gate dielectric for a sub-30 nm MOSFET

process, characteristics such as high thermodynamic stability, low impurity diffusion coefficient, high interfacial layer quality, and large barrier height (>1 eV) for electrons and holes [33-35] should be considered. A wide range of high-k dielectric in Table 1.1 has been studied [36, 37].

Table 1.1 Material characteristics of high-k dielectric.

| Material                                           | Method                             | $\mathcal{E}_r$ | E <sub>br</sub> (MV/cm) | Stored energy density $\varepsilon E_{br}^2/2$ (J/cm <sup>3</sup> ) | Stored charge $Q_{max}$ ( $\mu$ C/cm <sup>2</sup> ) |

|----------------------------------------------------|------------------------------------|-----------------|-------------------------|---------------------------------------------------------------------|-----------------------------------------------------|

| $Al_2O_3$                                          | wet anodized                       | 6               | 8                       | 17                                                                  | 4.3                                                 |

|                                                    | reactive sputter                   | 8               | 6                       | 13                                                                  | 4.3                                                 |

| Ta <sub>2</sub> O <sub>5</sub>                     | wet anodized                       | 25              | 6                       | 40                                                                  | 13.3                                                |

|                                                    | reactive sputter                   | 23              | 4                       | 16                                                                  | 8.2                                                 |

| $ZrO_2$                                            | wet anodized                       | 21              | 4                       | 15                                                                  | 7.4                                                 |

|                                                    | reactive sputter                   | 24              | 4                       | 17                                                                  | 8.5                                                 |

| $SiO_2$                                            | thermal oxidation (MOS gate oxide) | 3.9             | 18                      | 57                                                                  | 6.2                                                 |

|                                                    | reactive sputter                   | 3.9             | 10                      | 17                                                                  | 3.5                                                 |

| (Ba,Sr)TiO <sub>3</sub>                            | CVD                                | 400             | 0.1                     | 0.2                                                                 | 3.5                                                 |

| Ti <sub>0.8</sub> Dy <sub>0.2</sub> O <sub>x</sub> | reactive sputter                   | 47              | 2.5                     | 13                                                                  | 10.4                                                |

| Zr.25Sn.42Ti.33O2                                  | reactive sputter                   | 27              | 7.6                     | 70                                                                  | 18.2                                                |

Here, band alignment becomes critical [38]. For example, Ta<sub>2</sub>O<sub>5</sub> (tantalum has a much lower gap for electrons than SiO<sub>2</sub>, which results in high leakage problems due to Schottky emission of carriers into the band states. Ta<sub>2</sub>O<sub>5</sub> has been studied extensively for capacitor application, having a reasonably large band gap of 4.4 eV.

However, as its electron barrier height with silicon is only 0.36 eV, high leakage current at high operation temperature is inevitable. On the other hand,  $(Ti,Dy)_xO_y$  and  $Al_2O_3$  have acceptable barrier heights for both electrons and holes, minimizing Schottky emission and making these compounds attractive candidates for gate dielectric application. Consequentlyafter 2005, microprocessor manufacturers have begun integrating high-k dielectrics and metal gates into mainstream silicon integrated circuits [39].

Fundamentally, high-k dielectrics are electrical insulators with significant polarizability in an electric field. This high polarization enables a high charge buildup on the oxide's electrodes when minimal voltage is applied, thus minimizing the power necessary to switch a transistor. The energy  $(\varepsilon_r \varepsilon_0 E_{br}^2)$  and charge  $(\varepsilon_r E_{br})$  storage capacities are listed in Table 1.1 as well.

Sputtering deposition and atomic layer deposition (ALD) are common tools in researching dielectric oxides [40]. In the conventional manufacturing, another deposition technique, chemical vapor deposition (CVD), is more common for depositing the dielectric material in high performance transistors in consideration of the low global defect density [41]. Chemical vapor deposition, along with its many derivatives, is a versatile deposition technique for oxides, nitrides, carbides, and metals [42]. The desired film components are introduced into the reaction chamber as volatile compounds which react in the gas or on the substrate [43].

ALD is a related technique, which relies on sequential introduction of each precursor compound into the chamber, separated by vacuum pump-out or purging cycles of argon [43]. Precursors are chosen which do not self-react, and because each precursor is introduced individually, at most a monolayer of material can be deposited with each cycle, controlled by surface adsorption. For oxide deposition, a volatile

compound of the metal (AlCl<sub>3</sub>, Al(CH<sub>3</sub>)<sub>3</sub>, or TiCl<sub>4</sub>, or HfCl<sub>4</sub>) is sequentially introduced with water vapor [44]. The technique affords strong control of the oxide thickness and conformity to step edges, highly desirable for the convoluted structures of non-planar transistor geometries.

Some high-k dielectric materials, including Ta<sub>2</sub>O<sub>5</sub> [45] and TiO<sub>2</sub> [30], have been found to be thermally unstable in direct contact with polysilicon substrate. The use of thermo-dynamically stable high-k dielectric in direct contact with polysilicon is needed to integrate simple gate structure. ALD Al<sub>2</sub>O<sub>3</sub> and (Ti,Dy)<sub>x</sub>O<sub>y</sub> are two of the most promising high-k materials in this regard. Replacement gate technology was used in order to avoid the exposure of metal to high-temperature source drain activation annealing.

## 1.4 Stackable Flash Memory Cell for 3-D Integration

Three-dimensional (3-D) integration is an emerging technology that can form highly integrated systems by vertically stacking and connecting various materials, technologies and functional components together [46, 47]. The potential benefits of 3-D integration can vary depending on approach. They include multi-functionality, increased performance, reduced power, small form factor, reduced packaging, increased yield and reliability, flexible heterogeneous integration and reduced overall costs. The industry paradigm will shift to a new industry-fusing technology era that will offer tremendous global opportunities for expanded use of 3-D silicon-based technologies in highly integrated systems.

Recently, the great demand for higher density and lower bit cost in NAND flash memories is growing because these devices are keys for mass data storage applications in various portable electronic products, such as portable audio and video

players, cellular phones, USB memories and newly introduced solid state disks for mobile PCs.

In order to continue reducing the bit cost and increasing the bit density, the linear shrink of the patterns has been aggressively pursued by developing MLC (multi level cell) technology and early adoption of advanced lithographic tools [1]. However, the linear scaling down of the NAND flash memories is approaching the physical, electrical and reliability limitations, especially as the dimension of the technology node is below 30 nm.

First, EUV (extreme ultra-violet) lithography must be used for the patterning, since other nano-scale lithography based on scanning such as E-beam and nanoimprint still involves too much cost per chip due to the low throughput. The EUV technology, combined with immersion, is expected to be available after the year 2009, according to the ITRS roadmap [2]. Even when the tool is prepared, its cost will be quite high and its throughput will not be comparable to that of the conventional ArF lithography. In terms of the bit cost, even if the dimensions are shrunk and the density is increased, the bit cost may not continue its historical downward trend. Therefore, the economic need for increasingly small devices with higher density will diminish and the bit growth rate in the data storage applications will likely slow down if only a single layer of active memory is implemented in the chip area.

Secondly, from the electrical and reliability perspectives, shrinking the dimensions of the device to smaller than 30 nm will cause serious problems such as electrical isolation between the word-lines and the cell nodes, short channel effect, cell current reduction and tolerable charge losses of the stored charges for data retention even in newly developed SONOS (Silicon-Oxide-Nitride-Oxide-Silicon)-like structures.

Furthermore, these problems result from fundamental physical limits, which are difficult to overcome by the conventional modifications used in past nodes. Therefore, one of the best ways to circumvent these barriers caused by simple conventional linear shrinking technology is to stack the cell arrays in a 3-D manner while minimizing the additional stacking processes. An easy solution to increase density has been to stack chips or packages using bonding or packing technology. However, this stacking process does not reduce the bit cost nor the fabrication costs because they stack chips which have already been completely integrated.

Heat dissipation is a major concern in 3-D integration whether in the chip or packaging level. This will pose a performance improvement limit for most logic circuits. The 3-D integration technology for better control of heat dissipation is out of scope of this thesis. Fortunately, for 3-D integration of memory arrays, heat is much less a problem due to the very low percentage of device activation.

Recently, Bit-Cost Scalable (BiCS) flash technology has been introduced as a promising candidate [45]. With BiCS, an entire stack of electrode plates is punched through and plugged with poly-silicon all at once, forming a series of vertical FETs which act as a NAND string of SONOS-type memories. The memory FETs work in depletion-mode with the body polysilicon being undoped or lightly n-doped uniformly, which avoids the process complexity of forming p-n junctions within the plug. Each plate acts as a control gate with the exception of the lowest plate which functions as the lower select gate. However, certain fabrication issues, such as polysilicon surface roughness and non-uniformity of tunnel dielectric material due to step coverage need to be resolved before BiCS can become a viable and attractive alternative in the flash technology market. Another candidate is single-crystal Si layer stacking (S³) technology [46]. In S³ technology, the Si active layers are stacked with minimum

processes and are interconnected simultaneously with the bottom cell arrays and the peripheral circuits. Also, its electrical characteristics have been improved by reducing the capacitive and resistive loading without reducing the cell current. Its high-cost process and low-throughput due to adapting the epitaxial-layer growth are the main challenges facing this technology.

In this thesis effort, we propose novel planar UTB TFT based on deposited polycrystalline silicon or germanium as the technology capable of overcoming all aforementioned problems with its better process compatibility and cost-effectiveness for 3-D integration of flash memory cells.

#### 1.5 Overview of Dissertation

From the fabrication process point of view, the memory device for 3-D integration must meet three major requirements. The first is compatibility with conventional process for cost-effective mass production. The second requirement is the floating-gate itself for reliable data retention and data endurance. The third is the dielectric integrity for control and tunneling barriers. This dissertation focuses mainly on what effects these three parts of the memory structure have on the electrical characteristics. The dissertation is organized as follows.

Chapter 1 introduces the background for this research and provides a basic description of the floating-gate memory device. Our motives for focusing on the metal nanocrystal floating gate are also discussed. The role of the tunneling barrier on the floating-gate nonvolatile memory structure is presented along with the importance of using high-k dielectric as a replacement of the conventional SiO<sub>2</sub> for the control and tunneling barriers. Also, an outline is provided in order to introduce the overall ideas of the dissertation.

Chapter 2 investigates the process characteristics of direct-deposit self-assembly metal nanocrystal formation and the physical characterization of high-k dielectric, self-aligned silicidation (SAS) and the Ge channel material. The chemical mechanical polishing for obtaining a uniform ultra-thin-body film is also studied for 3-D integration flash memory cell.

In Chapter 3, the tunneling barriers in a nanocrystal memory device are studied. The effects of the various tunneling barriers on the data retention and memory window are investigated with the experimental results. (Ti,Dy)<sub>x</sub>O<sub>y</sub> and Al<sub>2</sub>O<sub>3</sub> high-k dielectrics are proposed for the tunneling barrier as a means to prolong the data retention and enhance the memory window simultaneously. Chapter 3 also describes double layer metal nanocrystal floating gate memories as a means to further improve retention time and charge storage capacity.

Chapter 4 presents the fabrication of self-aligned silicidation (SAS) for the reduction of contact resistance near source and drain regions for UTB TFT. Both structural analysis and electrical characterization are performed.

The Ge TFT process is proposed in Chapter 5, as a replacement for the conventional polysilicon process for the 3-D integration nonvolatile memory device. Structural analysis and electrical characterization are presented.

Finally, chapter 6 concludes the dissertation with a summary and suggestions for future research.

#### REFERENCES

- [1] Kinam Kim, "Technology for sub-50 nm DRAM and NAND Flash Manufacturing," in *IEDM Tech. Dig.*, 2005, pp. 323-326.

- [2] International Technology Roadmap for Semiconductors. ITRS Home Page, May 2007. http://www.itrs.net.

- [3] B. Prince, Semiconductor memories, John Wiley & Sons Ltd., 1991.

- [4] H. S. Jeong, W. S. Yang, Y. S. Hwang, C. H. Cho, S. Park, S. J. Ahn, Y. S. Chun, S. H. Shin, S. H. Song, J. Y. Lee, S. M. Jang, C. H. Lee, J. H. Jeong, M.H. Cho, J. K. Lee, and K. Kim, "Highly manufacturable 4Gb DRAM using 0.11 μm DRAM technology," in *IEDM Tech. Dig.*, 2000, pp. 353-356.

- [5] N. Flaherty, "Not in a flash," *IEE Review*, pp. 50-53, Dec. 2003.

- [6] R. Bez, E. Camerlenghi, a. Modelli, and A. Visconti, "Introduction to flash memory," *Proc. IEEE*, 2003, vol. 91, no. 4, pp. 489-502, 2003.

- [7] D. Kim, W. Shin, J. Lee, J. Shin, J. Lee, S. Hur, I. Baik, Y. Shin, C. Lee, J. Yoon, H. Lee, K. Jo, S. Choi, B. You, J. Choi, D. Park, and K. Kim, "A 2Gb NAND flash memory with 0.044 mm<sup>2</sup> cell size using 90 nm flash technology," in *IEDM Tech. Dig.*, 2002, pp. 919-922.

- [8] K. Uchino, "Ferroelectric devices," New York: Marcel Dekker, Inc., 2000.

- [9] E. M. Philofsky, "FRAM-The ultimate memory," in *Int. Nonvolatile Memory Tech. Conf.*, 1996, pp. 99-104.

- [10] H. P. McAdams, R. Acklin, T. Blake, X. Du, J. Eliason, J. Fong, W. F. Kraus, D. Liu, S. Madan, T. Moise, S. Natarajan, N. Qian, Y. Qiu, K. A. Remack, J. Rodriguez, J. Roscher, A. Seshadri, and S. R. Summerfelt, "A 64-Mb embedded FRAM utilizing a 130-nm 5LM Cu/FSG logic process," *IEEE J. Solid-State circuits*, vol. 39, no. 4, pp. 667-677, 2004.

- [11] W. Kraus, L. Lehman, D. Wilson, T. Yamazaki, C. Ohno, E. Nagai, H. Yamazaki, H. Suzuki, "A 42.5mm<sup>2</sup> 1Mb nonvolatile ferroelectric memory utilizing advanced architecture for enhanced reliability," in *Symp. VLSI Tech. Dig.*, 1998, pp. 242-245.

- [12] S. Y. Lee and K. Kim, "Future 1T1C FRAM technologies for highly reliable, high density FRAM," in *IEDM Tech. Dig.*, 2002, pp. 547-550.

- [13] A. L. Kholkin, E. L. Colla, A. K. Tagantsev, D. V. Taylor, and N. Setter, "Fatigue of piezoelectric properties in Pb(Zr,Ti)O<sub>3</sub> films," *Appl. Phys. Lett.*, vol. 68, pp. 2577-2579, 1996.

- [14] W. L. Warren, D. Dimos, G. E. Pike, B. A. Tuttle, M. V. Raymond, R. Ramesh, and J. T. Evans, Jr., "Voltage shifts and imprint in ferroelectric capacitors," *Appl. Phys. Lett.*, vol. 67, pp. 866-868, 1995.

- [15] W. J. Gallagher, S. S. P. Parkin, Y. Lu, X. P. Brian, A. Marley, K. P. Roche, R. A. Altman, S. A. Rishton, C. Jahnes, T. M. Shaw, and G. Xiao, "Microstructured magnetic tunnel junctions," *J. Appl. Phys.*, vol. 81, no. 8, pp. 3741-3746, 1997.

- [17] S. Tehrani, J. M. Slaughter, E. Chen, M. Durlam, J. Shi, and M. DeHerrera, "Progress and outlook for MRAM technology," *IEEE Trans. Magnetics*, vol. 35, no. 5, pp. 2814-2819, 1999.

- [18] S. Tehrani, B. Engel, J. M. Slaughter, E. Chen, M. DeHerrera, M. Durlam, P. Naji, R. Whig, J. Janesky, and J. Calder, "Recent developments in magnetic tunnel junction MRAM," *IEEE Trans. Magnetics*, vol. 36, no. 5, pp. 2752-2757, 2000.

- [19] M. Durlam, P. J. Naji, A. Omair, M. Deherrera, J. Calder, J. M. Slaughter, B. N. Engel, N. D. Rizzo, G. Grynkewich, B. Butcher, C. Tracy, K. Smith, K. W. Kyler, J. J. Ren, J. A. Molla, W. A. Feil, R. G. Williams, and S. Tehrani, "A 1-Mbit MRAM based on 1T1MTJ bit cell integrated with copper interconnects," *IEEE J. Solid-state circuits*, vol. 38, no. 5, pp. 769-773, 2003.

- [20] H. J. Kim, W. C. Jeong, K. H. Koh, G. T. Jeong, J. H. Park, S. Y. Lee, J. H. Oh, I. H. Song, H. S. Jeong, and K. Kim, "A process integration of high performance 64-kb MRAM," *IEEE Trans. Magnetics*, vol. 39, no. 5, pp. 2851-2853, 2003.

- [21] S. Tehrani, J. M. Slaughter, M. DeHerrera, B. N. Engel, N. D. Rizzo, J. Salter, M. Durlam, R. W. Dave, J. Janesky, B. Butcher, K. Smith, and G. Grynkewich, "Magnetoresistive random access memory using magnetic tunnel junctions," *Proc. IEEE*, vol. 91, no. 5, pp. 703-714, 2003.

- [22] L. Geppert, "The new indelible memories," *IEEE Spectrum*, pp. 49-54, 2003.

- [23] S. Lai and T. Lowrey, "OUM-a 180 nm nonvolatile memory cell element technology for stand alone and embedded applications," in *IEDM Tech. Dig.*, 2001, pp. 803-806.

- [24] J. Maimon, E. Spall, R. Quinn, and S. Schnur, "Chalcogenide-based non-volatile memory technology," in *Proc. IEEE Aerospace Conf.*, 2001, pp. 2289-2292.

- [25] S. Lai, "Current status of the phase change memory and its future," in *IEDM Tech*. *Dig.*, 2003, pp. 255-258.

- [26] Y. H. Ha, J. H. Yi, H. Horii, J. H. Park, S. H. Joo, S. O. Park, U-In Chung, and J. T. Moon, "An edge contact type cell for phase change RAM featuring very low power consumption," in *Symp. VLSI Tech. Dig.*, 2003, pp. 175-176.

- [27] A. Pirovano, A. L. Lacaita, A. Benvenuti, F. Pellizzer, S. Hudgens, and R. Bez, "Scaling analysis of phase-change memory technology," in *IEDM Tech. Dig.*, 2003, pp. 699-702.

- [28] D. Kahng and S. M. Sze, "A floating gate and its application to memory devices," *Bell Syst.* Tech. *J.*, vol. 46, p. 1288-12, 1967.

- [29] D. A. Muller, T. Sorsch, S. Moccio, F. H. Baumann, K. Evans-Lutterodt, and G. Timp, "The electronic structure at the atomic scale of ultrathin gate oxide," *Nature*,

- vol. 399, pp. 758-761, 1999.

- [30] Xin Guo, Xienwen Wang, Zhijiong Luo, T.P. Ma and Tamagawa, "High quality ultra-thin (1.5 nm) TiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> gate dielectric for deep submicron CMOS technology," in *IEDM Tech. Dig.*, 1999, pp. 137-140.

- [31] B. H. Lee, L. G. Kang, W. J. Qi, R. Nieh, Y. J. Jeon, K. Onishi and Jack Lee, "Ultra thin hafnium oxide with low leakage and excellent reliability for alternative gate dielectric application", in *IEDM Tech. Dig.*, 1999, pp. 133-136.

- [32] Zengtao Liu, Chungho Lee, Venkat Narayanan, Gen Pei, and Edwin Chihchuan Kan, "Metal nanocrystal memories-part 1: Device design and fabrication," *IEEE Trans. Elec. Dev.*, vol. 49, pp. 1606-1613, 2002.

- [33] P. Zurcher, C. J. Tracy, R. E. Jr. Jones, P. Alluri, P. Y. Chu, B. Jiang, M. Kim, B. M. Melnick, M. V. Raymond, D. Roberts, T. P. Remmel, T. L. Tsai, B. E. White, S. Zafar, S. J. Gillespie, "Barium strontium titanate capacitors for embedded DRAM," in *Mater. Res. Soc. Symp.*, *Proc*, 1999, pp.11-22.

- [34] A. Grill, "Electrode structures for integration of ferroelectric or high dielectric constant films in semiconductor devices," in *Mater. Res. Soc. Symp. Proc.*, 1999, pp. 89-99.

- [35] H. J. Hubbard and D. G. Schlom, "Thermodynamic stability of binary oxides in contact with silicon," *J. Mat. Res.*, vol. 11, no. 11, pp. 2757-2776, 1996.

- [36] L. I. Maissel and R. Glang, *Handbook of Thin Film Technology*. New York: McGraw-Hill, 1970.

- [37] R. B. van Dover, L. F. Schneemeyer, and R. M. Fleming, "Discovery of a useful thin-film dielectric using a composition-spread approach," *Nature 392*, pp. 162-164, 1998.

- [38] John Robertson, "Band offsets of wide-band-gap oxides and implications for

- future electronic devices," J. Vac. Sci. Tech., vol.18, no.3, pp.1785-1791, 2000.

- [39] K. Mistry, C. Allen, C. Auth, B. Beattie, D. Bergstrom, M. Bost, M. Brazier, M. Buehler, A. Cappellani, R. Chau, C.-H. Choi, G. Ding, K. Fischer, T. Ghani, R. Grover, W. Han, D. Hanken, M. Hattendorf, J. He, J. Hicks, R. Huessner, D. Ingerly, P. Jain, R. James, L. Jong, S. Joshi, C. Kenyon, K. Kuhn, K. Lee, H. Liu, J. Maiz, B. McIntyre, P. Moon, J. Neirynck, S. Pae, C. Parker, D. Parsons, C. Prasad, L. Pipes, M. Prince, P. Ranade, T. Reynolds, J. Sandford, L. Shifren, J. Sebastian, J. Seiple, D. Simon, S. Sivakumar, P. Smith, C. Thomas, T. Troeger, P. Vandervoorn, S. Williams, and K. Zawadzki, "A 45nm logic technology with high-k metal gate transistors, strained silicon, 9 Cu interconnect layers, 193 nm dry patterning, and 100 percent pb free packaging," in *IEDM Tech. Dig.*, 2007, pp. 247-250.

- [40] Milton Ohring. "Materials science of thin films: Deposition and structure," Academic Press, San Diego, second edition, 2002.

- [41] Clemens J. FÄorst, Christopher R. Ashman, Karlheinz Schwarz, and Peter E. BlÄochl, "The interface between silicon and a high-k oxide," June 2008. http://info.tuwien.ac.at/theochem/si-srtio3 interface/si-srtio3.html.

- [42] Colin H. L. Goodman and Markus V. Pessa, "Atomic layer epitaxy," *J. Appl. Phys.*, vol. 60, no. 3, pp. 65-81, 1986.

- [43] S. M. George, O. Sneh, A. C. Dillon, M. L. Wise, A. W. Ott, L. A. Okada, and J. D. Way, "Atomic layer controlled deposition of SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> using binary reaction sequence chemistry," *Applied Surface Science*, vol. 82, no. 1, pp. 460-467, 1994.

- [44] Brett W. Busch, Olivier Pluchery, Yves J. Chabal, David A. Muller, Robert L. Opila, J. Raynien Kwo, and Eric Garfunkel. "Materials characterization of alternative gate dielectrics," *MRS Bulletin*, pp. 206-211, March 2002.

- [45] H. F. Luan, S. J. Lee and C. H. Lee, S. C. Song, Y. L. Mao, Y. Senzaki, D.

Roberts and D. L. Kwong, "High Quality  $Ta_2O_5$  Gate Dielectrics with  $T_{ox,eq}$  <10Å," in *IEDM Tech. Dig.*, 1999, pp. 141-144.

[46] S-M Jung, J. Jang, W. Cho, H. Cho, J. Jeong, Y. Chang, J. Kim, Y. Rah, Y. Son, J. Park, M-S Song, K-H Kim, J.S. Lim, and Kinam Kim, "Three dimensionally stacked NAND flash memory technology using stacking single crystal Si layers on ILD and TANOS structure for beyond 30nm node," in *IEDM Tech. Dig.*, 2006, pp. 37-40.

[47] Y. Fukuzumi, Y. Matsuoka, M. Kito, M. Kido, M. Sato, H. Tanaka, Y. Nagata, Y. Iwata, H. Aochi, A. Nitayama, "Optimal integration and characteristics of vertical array devices for ultra-high density, bit-cost scalable flash memory," in *IEDM Tech*. *Dig.*, 2007, pp. 449-452.

## CHAPTER 2

#### 3-D INTEGRATION FLASH MEMORY CELL

## 2.1 Planar Polysilicon UTB TFT Cell

#### 2.1.1 Motivation

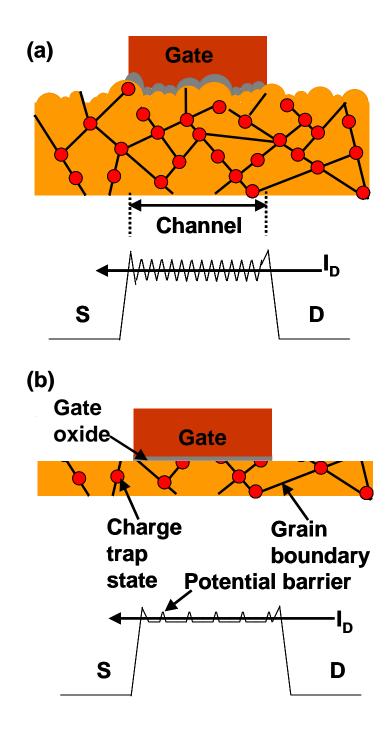

The continuous scaling of MOSFET technology into the deep sub-micron regime poses considerable challenge to the conventional MOSFET structure. To suppress short-channel effects such as drain induced barrier lowering (DIBL) and  $V_T$  roll-off, extremely high levels of channel doping are required, but these result in increased leakage by band-to-band tunneling and degraded mobility.

To overcome the one-layer fabrication limit for conventional bulk MOSFET structure, polysilicon TFT has been widely studied. However, due to the formation of the grain boundaries along the polysilicon channel, the characteristics of the polysilicon TFTs show much smaller transconductance and larger threshold voltage than those of bulk devices. Specifically, polysilicon TFTs show more complex electrical characteristics than single crystal devices, such as the *kink effect*, a large increase of output conductance in the saturation region due to body charge or self heating. There have been some attempts to overcome these problems [1-4].

In this context, the ultra-thin body (UTB) MOSFET is one of the most promising alternative structures that effectively suppress DIBL and other short channel effects. The channel film thickness required is typically less than 30% of the gate length. The most difficult step for the fabrication of the ultra-thin body FET is the formation of a uniform, thin channel film with efficient source/drain contacts. Oxidation and etch back have been proposed [5], but are limited by the thickness uniformity of the starting SOI (silicon on insulator) wafers and by the process-induced

variation. On the other hand, deposited films can be well-controlled and have good uniformity. Therefore, establishing processes to form highly uniform ultra-thin channel material using chemical mechanical polishing (CMP) process step can be a competitive approach.

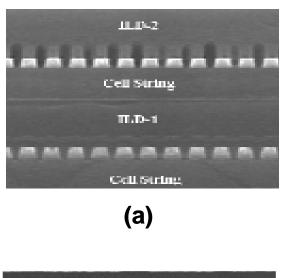

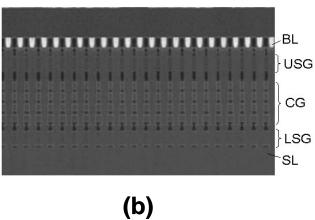

# 2.1.2. The Concept of Ultra-Thin Body TFT

Figure 2.1 shows two promising candidates for the 3-dimensional (3-D) integration of flash memory cells. The planar 3-D stacked NAND flash scheme by Samsung electronics company (SEC) as shown in Figure 2.1(a) has the advantage of being easily adapted to current technology [6]. One drawback is that it requires an additional lithography process for layer added. Alternately, in the Toshiba electronics company (TEC) scheme, the additional lithography step is not needed even though several layers are added onto the built-in structure as shown in Figure 2.1 (b) [7]. However, TEC technology has several problems such as scaling limitation of the contact opening diameter and surface roughness in the channel. To overcome these problems and easily adapt the technology for mass production, we need a new design for 3-D integration of flash memory cells. If the thickness of polysilicon is reduced, the total number of trap states and grain boundaries can be reduced as shown in Figure 2.2. This also makes the threshold voltage less sensitive to trap-density fluctuation when the flash memory cells operate. However, the TEC scheme ignores the surface roughness of the polysilicon channel in the step to adopt the vertical transistor in their flash memory cell, which made it impossible to get good surface roughness in the polysilicon channel because the CMP process cannot be adapted in the vertical structure. When the channel thickness is 100-200 nm, a few nanometers surface roughness is not critical. However, as the polysilicon channel thickness shrinks to the

proximity of tens of nanometers or even below ten nanometers, the issue of surface roughness will emerge due to surface scattering and a non-uniform electric field as shown in Figure 2.2 (a). To solve this problem, we introduce the CMP process to achieve the higher thickness and surface uniformity of polysilicon channel as shown in Figure 2.2 (b). The concept behind the UTB TFT is to reduce surface roughness and charge trap density which results in less threshold voltage fluctuation and a more uniform electric field at the interface between the tunnel barrier and the channel.

**Figure 2.1** Vertical structures (schematics of (a) Samsung and (b) Toshiba) of promising candidates for 3-D integration of flash memory cells.

**Figure 2.2** Schematics and channel potentials of (a) conventional TFT without CMP and (b) the proposed CMP processes.

## 2.1.3 CMP Process

Chemical mechanical polishing (CMP) is a useful tool for wafer-scale surface planarization in the semiconductor industry [8, 9]. The CMP process is essential to form the planarization of the interlayer dielectric, interconnection metal layers and polysilicon ultra-thin body TFT in multi-level technology.

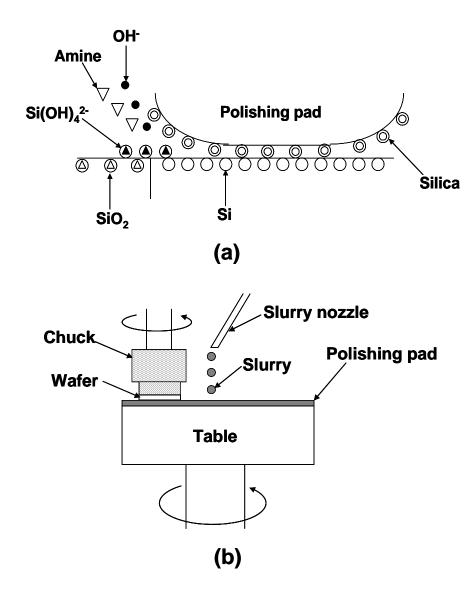

The basic concept of the CMP process is that the wafer is held on a rotating carrier (holder) while the face being polished is pressed against a polishing pad attached to a polishing platen disk. For oxide, silicon and polysilicon polishing, alkaline slurry of colloidal silica (a suspension of SiO<sub>2</sub> particles), is used as the chemical abrasive. The size of the particles varies in the literature between 0.01 µm and 3 µm. The slurry is carried to the wafer by the porosity of the polishing pad. This slurry chemically attacks the wafer surface, converting the silicon to a hydroxilated form (with the OH<sup>-</sup> radical), which is more easily removed by the mechanical abrasive.

Gross mechanical damage of the surface is prevented by the fact that the colloidal silica particles in the slurry are not harder than the oxide or silicon to be removed. Otherwise, the quality of the surface planarity would be limited by the diameter of the silica particles. CMP needs fewer steps compared to deposition/etch-back process and uses nontoxic substances. Furthermore, it has good removal selectivity and good controllability of rate. Another advantage of CMP lies in the global planarization. Since the size of the flat area on a chip becomes smaller, the quality of local planarization becomes worse. CMP process is essential in overcoming this problem in multi-stacking technology. Additional difficulties may arise for the filling of small holes in ULSI (ultra large scale integration) technology. CMP reduces the density of defects such as shorts and stringer due to residual metal [10]. Figure 2.3 shows the mechanism diagram and experimental apparatus of the CMP process.

During the ionization step, hydroxyl and aminium ions are formed. The hydroxyl ions in water then oxidize the surface of the polysilicon to form hydrous silica with the evolution of hydrogen [11].

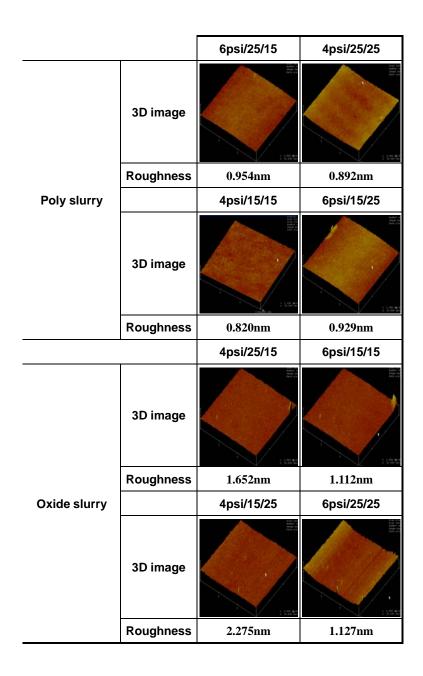

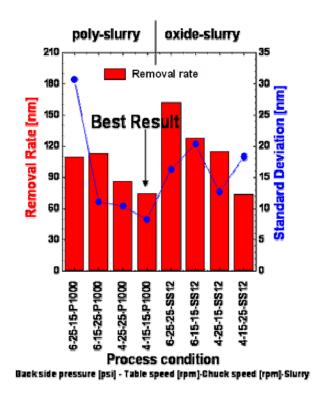

Furthermore, there are several factors that have effects on the CMP process. Generally, the main factors are down pressure, table speed, chuck speed and slurry. To get high uniformity including local and global planarization in the wafer, one should carefully consider these factors. To control the subtle nature of the process, the removal rate of polysilicon should be less than 50 nm/minute. Polysilicon thickness variation in the wafer should also be below 10 nm. Table 2.1 shows the split conditions of the main factors. Figure 2.4 shows the AFM results according to the CMP factors.

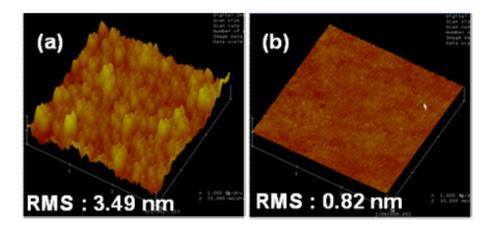

The parameters in the experiment which were considered are slurry, down pressure, chuck speed and table speed. From these results, as shown in Table 2.1, poly slurry is superior to oxide slurry and sample #3 is the best CMP condition in terms of the root mean square (RMS) value. The results of surface roughness are in agreement with the removal rate and the standard deviation.

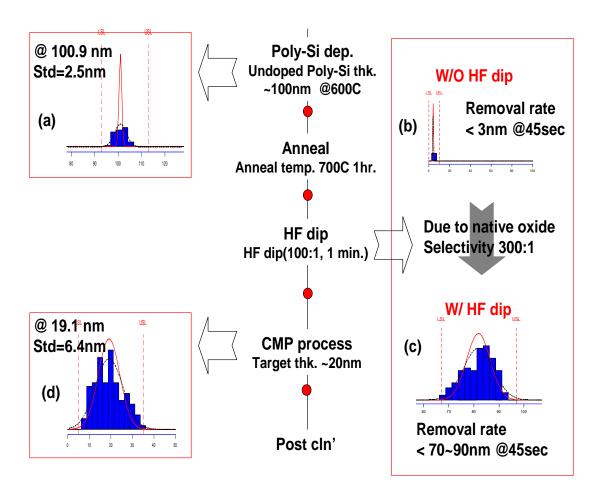

Figure 2.5 shows the schematic of the CMP process and the statistical distribution of thickness. After polysilicon deposition on the SiO<sub>2</sub>, the thickness and the standard deviation of polysilicon are 100.9 nm and 2.5 nm, respectively, as shown in Figure 2.5(a). Before the CMP process, we need to carry out a diluted HF dip process to remove the native oxide. If this HF dip process step is skipped, the removal rate is drastically decreased due to the native oxide on the surface of polysilicon. This is because the removal selectivity of oxide and polysilicon is 1 to 300 during the specific CMP process as shown in Figure 2.5(b). After the HF dip, we can obtain a stable CMP process. The removal rate was 70 nm through 90 nm for 45 sec as shown

in Figure 2.5 (c). The thickness distribution in the 4-inch full wafer shows the desired Gaussian distribution as shown in Figure 2.5 (d). After completing the polysilicon CMP under optimal conditions, the average thickness and standard deviation of polysilicon are 19.1 nm and 6.4 nm, respectively.

**Figure 2.3** (a) Schematic of chemical mechanical (CMP) process and (b) experimental apparatus of CMP process

Table 2.1 Chemical mechanical polishing condition.

| Factors Sample # | Slurry | Down pressure [psi] | Chuck rotation speed [rpm] | Table rotation speed [rpm] | Root mean square [nm] |

|------------------|--------|---------------------|----------------------------|----------------------------|-----------------------|

| 1                | Poly   | 6                   | 25                         | 15                         | 0.95                  |

| 2                | Poly   | 4                   | 25                         | 25                         | 0.89                  |

| 3                | Poly   | 4                   | 15                         | 15                         | 0.82                  |

| 4                | Poly   | 6                   | 15                         | 25                         | 0.93                  |

| 5                | Oxide  | 4                   | 25                         | 15                         | 1.65                  |

| 6                | Oxide  | 6                   | 15                         | 15                         | 1.11                  |

| 7                | Oxide  | 4                   | 15                         | 25                         | 2.28                  |

| 8                | Oxide  | 6                   | 25                         | 25                         | 1.13                  |

Figure 2.4 AFM results according to CMP factors.

**Figure 2.5** The schematic of CMP process and statistical distribution of thickness. (a) After polysilicon deposition, (b) without the HF dip process, (c) with the HF dip process and (d) after polysilicon CMP process.

#### 2.2 Ni Silicidation

#### 2.2.1 Motivation

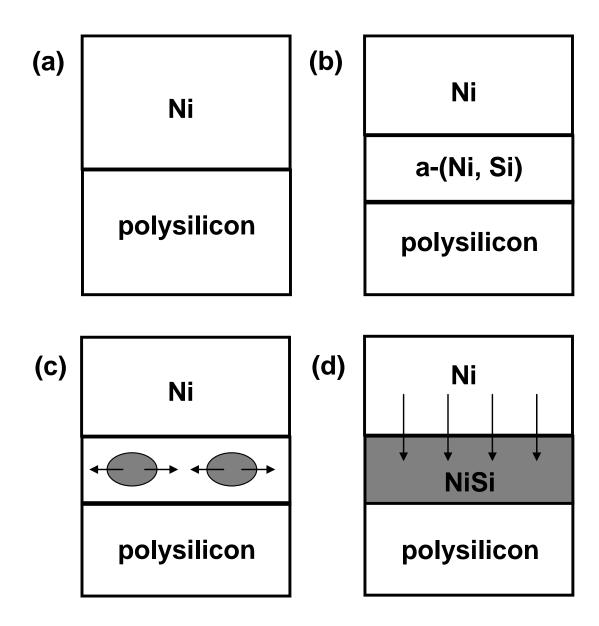

Self-aligned silicidation (SAS) technology is widely used in submicron complementary metal-oxide—semiconductor (CMOS) manufacturing to reduce sheet and contact resistance of the gate, source and drain areas [12-16]. The silicide process is essential in UTB devices with several tens of nanometer thickness where contact resistance limits their performance. Silicides can be formed in two ways. The first is via a polycide process in which metal (Ti, Co or Ni) is deposited on polysilicon and both are then patterned. Alternately, in the SAS process, the polysilicon is deposited and patterned first, and then the metal is deposited. The unreacted metal is then removed by a selective wet etch. In both case, the silicide layer is formed by thermal reaction.

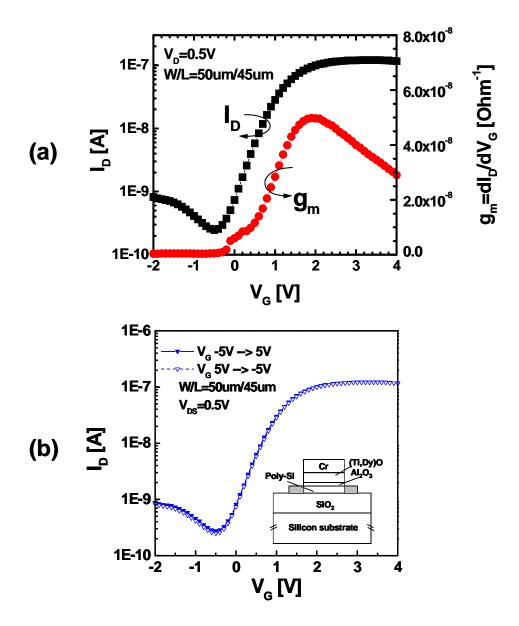

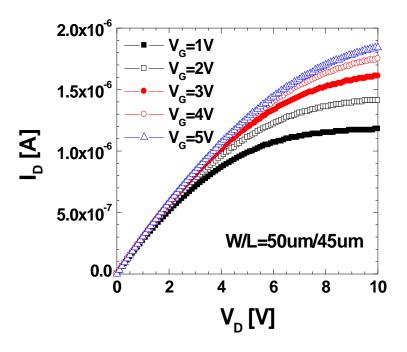

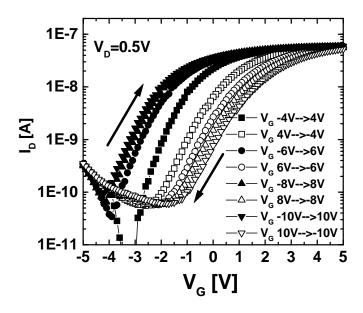

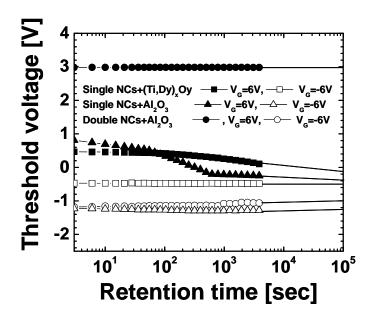

There are several metals such as Ti, Co, and Ni that can be used for SAS applications. It is very important to study various properties associated with these materials, *e.g.* process temperatures, time, resistivity, etchants, etch conditions and when the unreacted metal is removed. Some of the popular metal species that have been used for silicide processes include titanium di-silicide (TiSi<sub>2</sub>), cobalt di-silicide (CoSi<sub>2</sub>), and nickel silicide (NiSi).