# HYBRID SYNCHRONOUS / ASYNCHRONOUS DESIGN

#### A Dissertation

Presented to the Faculty of the Graduate School of Cornell University in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

by Filipp A Akopyan May 2011

© 2011 Filipp A Akopyan

ALL RIGHTS RESERVED

#### HYBRID SYNCHRONOUS / ASYNCHRONOUS DESIGN

Filipp A Akopyan, Ph.D.

#### Cornell University 2011

In this new era of high-speed and low-power VLSI circuits, the question of which circuit family is best for a given application has become much more relevant. From a designer's point of view, process technology scaling continues to reveal undesirable device behavior. Thus, a designer has to make decisions not only at the micro-architectural scale, but also at a lower, circuit-level scale. However, common circuit families are not sufficient to solve modern engineering problems in many cases.

Our goal is to provide resources that will allow designers to select the circuit family that yields the best results in terms of power, area, and performance metrics for each application, with minimal human input. Using our techniques, this choice can be made in a timely manner without in-depth knowledge of each circuit family.

We propose an improved hybrid synchronous / asynchronous toolflow that offers significant reduction in the design cycle time and we advise on how our work can be extended to various types of circuit families for any given technology node.

We describe tools that we have developed to allow designers to implement their projects using both synchronous and asynchronous circuit families. We also present the cosimulation environment that we have developed to allow designers to run complex digital and analog simulations of various circuits at different levels of abstraction with minimal setup effort. Finally, we demonstrate a highly optimized synchronous-asynchronous interface that works as a bridge in designs where part of the logic is implemented asynchronously within a globally synchronous system.

# Biographical Sketch

Filipp Akopyan was born in Moscow, Russia, where he grew up and lived until the age of 15. Filipp completed middle school in Russia and high school in the United States (at Spring Valley, NY). Filipp joined Rensselaer Polytechnic Institute (in Troy, NY) in September of 2001 and graduated number one in the School of Engineering with a Bachelor's Degree in Electrical Engineering in May of 2004. His concentrations at RPI included electronic circuit design and signal processing.

The author has been enrolled in a joint M.S. / Ph.D. program at Cornell University since September 2004. At Cornell his main interests included high-speed VLSI circuits (including 3-D integrated circuits and neuromorphic systems) that operate under extreme conditions and withstand process variations. He has also developed low-power asynchronous systems for signal processing.

Filipp is a part of the Asynchronous VLSI (AVLSI) research group led by Professor Rajit Manohar. Filipp's office is located in Upson Hall, 358 in the Computer Systems Laboratory.

### Acknowledgments

First of all I would like to thank my advisor, Professor Rajit Manohar, who always offered support and encouragement even in the toughest days of my graduate career. His enormous help, ideas and willingness to discuss my (at times risky and unconventional) ideas, allowed me to think outside of the box and perform the work outlined in this thesis. I thank my close friends and colleagues at AVLSI and the entire CSL staff. Special thanks go to Carlos Tadeo Ortega Otero, Ilya Ganusov, David Fang and Virantha Ekanayake for all the valuable advices that they have offered to me during my studies. I have been lucky to have such loyal and smart friends surround me in graduate school.

My appreciation and endless love go to my family (Andrey, Galina, Seva, Alexander and Vera), especially to my mother, Yuliya, who has always been there for me and gave up everything she could in order to make my life better. I would like to thank Sergey Rakov for all of his valuable professional and personal advices throughout my life and for getting me interested in the Electrical Engineering field.

My gratitude goes to my lifetime friends: Vadim Zipunnikov, Borjan Gagoski, Peter Paliwoda, Chin-Chen Lee and Jan Kostecki for helping me deal with difficulties of graduate life. I would also like to thank Alena for her love and patience through these last few years.

This research was supported in part by National Science Foundation and IBM.

# Table of Contents

| 1 | Intr | Introduction                                       |      |  |  |  |  |  |  |

|---|------|----------------------------------------------------|------|--|--|--|--|--|--|

|   | 1.1  | Motivation                                         | . 1  |  |  |  |  |  |  |

|   | 1.2  | Background                                         |      |  |  |  |  |  |  |

|   | 1.3  | Proposed Toolflow Basics                           |      |  |  |  |  |  |  |

|   | 1.4  | Asynchronous Design Methods and Challenges         | . 6  |  |  |  |  |  |  |

|   | 1.5  | Toolflow Evaluation                                | . 7  |  |  |  |  |  |  |

|   | 1.6  | Organization of This Thesis                        | . 8  |  |  |  |  |  |  |

| 2 | Too  | lflow                                              | 10   |  |  |  |  |  |  |

|   | 2.1  | Toolflow Comparison                                | . 10 |  |  |  |  |  |  |

|   |      | 2.1.1 Conventional Toolflows                       | . 10 |  |  |  |  |  |  |

|   |      | 2.1.2 Proposed Toolflow                            | . 12 |  |  |  |  |  |  |

|   |      | 2.1.3 Proposed Simulator Chain                     | . 14 |  |  |  |  |  |  |

|   | 2.2  | Industrial Tools Used in the Flow                  | . 16 |  |  |  |  |  |  |

|   |      | 2.2.1 Synchronous Digital Simulator                | . 16 |  |  |  |  |  |  |

|   |      | 2.2.2 Transistor-Level Analog Simulator            | . 16 |  |  |  |  |  |  |

|   | 2.3  | Cornell AVLSI's Tools Overview                     | . 16 |  |  |  |  |  |  |

|   |      | 2.3.1 Asynchronous Digital Simulator (PRSIM)       | . 16 |  |  |  |  |  |  |

|   |      | 2.3.2 Verilog-to-ACT                               | . 17 |  |  |  |  |  |  |

|   |      | 2.3.3 Netlist Generator                            | . 19 |  |  |  |  |  |  |

|   |      | 2.3.4 Automatic Cosimulation Environment Generator | . 19 |  |  |  |  |  |  |

|   |      | 2.3.5 Circuit Family Libraries                     | . 20 |  |  |  |  |  |  |

| 3 | Aut  | omatic Cosimulation Environment Generator          | 22   |  |  |  |  |  |  |

|   | 3.1  | Motivation                                         | . 22 |  |  |  |  |  |  |

|   | 3.2  | Vision                                             | . 24 |  |  |  |  |  |  |

|   | 3.3  | Auto Simulation Setup                              |      |  |  |  |  |  |  |

|   | 3.4  | Overview                                           |      |  |  |  |  |  |  |

|   | 3.5  | Functionality                                      |      |  |  |  |  |  |  |

|   | 3.6  | Common Setup Parameters                            |      |  |  |  |  |  |  |

|   | 3.7  | Sources and Sinks Library for Testing Environment  |      |  |  |  |  |  |  |

|   | 3.8  | Global Connections                                 |      |  |  |  |  |  |  |

|   | 3.9  | Output Files                                       |      |  |  |  |  |  |  |

| 4  | Toolflow Evaluation                    |                                                         |     |  |  |  |  |  |

|----|----------------------------------------|---------------------------------------------------------|-----|--|--|--|--|--|

|    | 4.1                                    | 1 Benchmark Considerations                              |     |  |  |  |  |  |

|    | 4.2                                    |                                                         |     |  |  |  |  |  |

|    | 4.3                                    | Process Variations                                      | 58  |  |  |  |  |  |

|    | 4.4                                    | Power Analysis                                          |     |  |  |  |  |  |

|    | 4.5                                    | Design Space Analysis                                   |     |  |  |  |  |  |

|    | 4.6                                    | Designer Guidelines                                     |     |  |  |  |  |  |

| 5  | Asy                                    | nchronous-to-Synchronous Interface with Discrete Timing | 67  |  |  |  |  |  |

|    | 5.1                                    | Motivation and Background                               | 67  |  |  |  |  |  |

|    |                                        | 5.1.1 Synchronous-to-Asynchronous Boundary              | 68  |  |  |  |  |  |

|    |                                        | 5.1.2 Asynchronous-to-Synchronous Boundary              | 71  |  |  |  |  |  |

|    | 5.2                                    |                                                         |     |  |  |  |  |  |

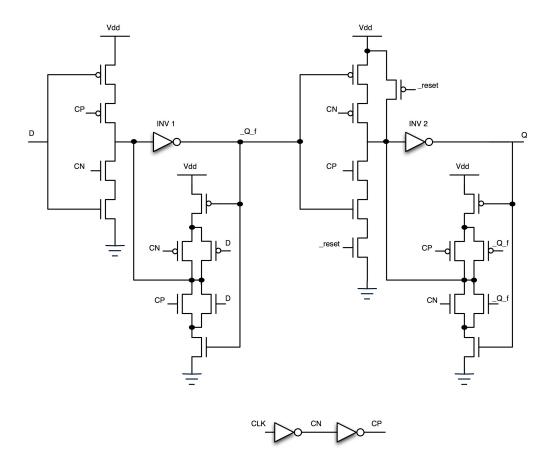

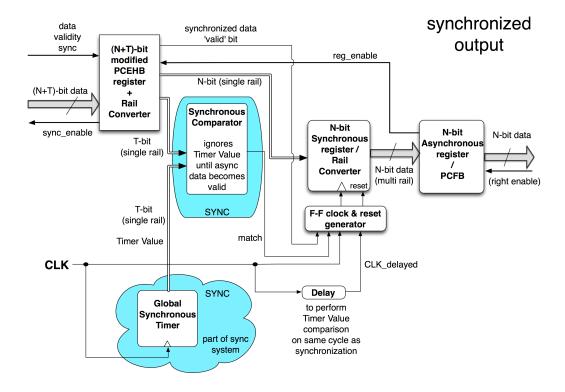

|    | 5.3                                    | 5.3 Proposed Interface Overview                         |     |  |  |  |  |  |

|    | 5.4                                    | Proposed Interface Detailed Description                 | 76  |  |  |  |  |  |

|    |                                        | 5.4.1 Input Stage of the Synchronizer                   | 78  |  |  |  |  |  |

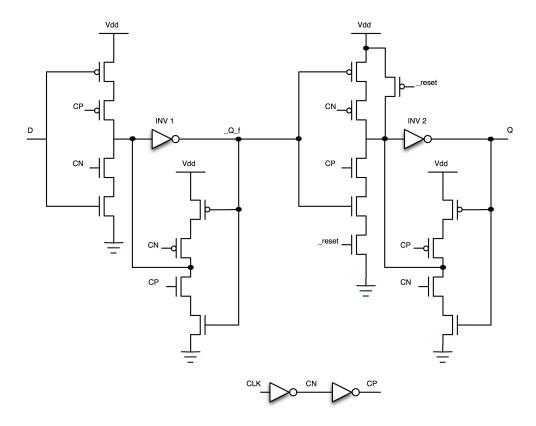

|    |                                        | 5.4.2 Flip-Flop Implementation Details                  |     |  |  |  |  |  |

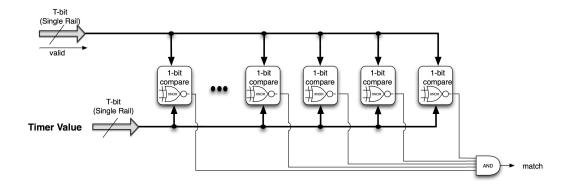

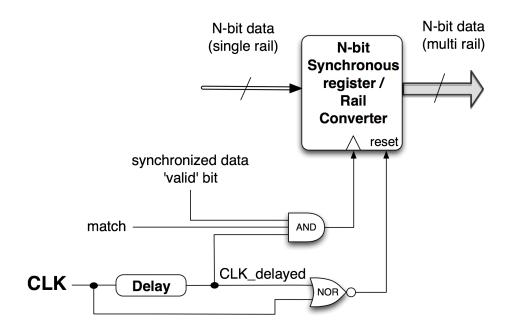

|    |                                        | 5.4.3 Synchronous Circuitry                             |     |  |  |  |  |  |

|    |                                        | 5.4.4 Synchronous Register Implementation               |     |  |  |  |  |  |

|    |                                        | 5.4.5 Synchronizer Output Stage                         | 92  |  |  |  |  |  |

| 6  | $\mathbf{Ad}$                          | itional Related Research                                | 94  |  |  |  |  |  |

| 7  | 7 Suggestions for Further Improvements |                                                         |     |  |  |  |  |  |

| 8  | 3 Conclusion                           |                                                         |     |  |  |  |  |  |

| Bi | ibliog                                 | raphy                                                   | 101 |  |  |  |  |  |

# List of Figures

| 1.1                                                                 | Synchronous and Asynchronous Time Domains                                                                                                                                                                                                                                                            | 4                                                        |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5                                     |                                                                                                                                                                                                                                                                                                      | 11<br>12<br>13<br>15<br>18                               |

| 2.6                                                                 | Verilog-to-ACT Synchronous to Asynchronous Transformation                                                                                                                                                                                                                                            | 18                                                       |

| 3.1                                                                 | Overview of COSIM's Functionality                                                                                                                                                                                                                                                                    | 31                                                       |

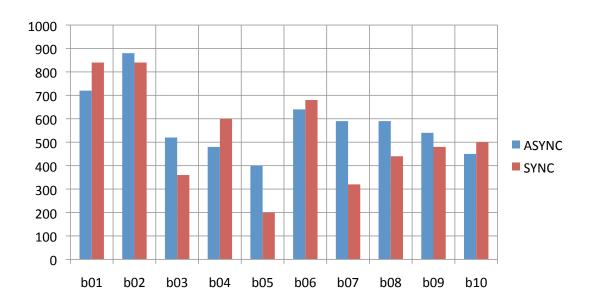

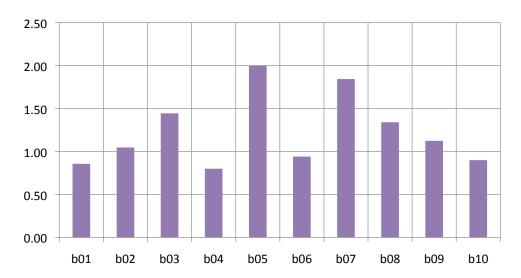

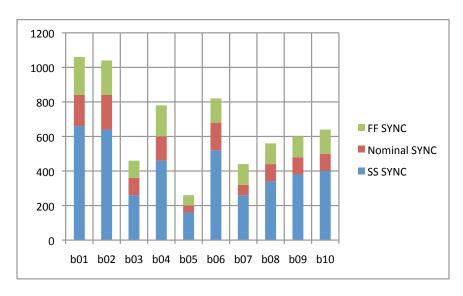

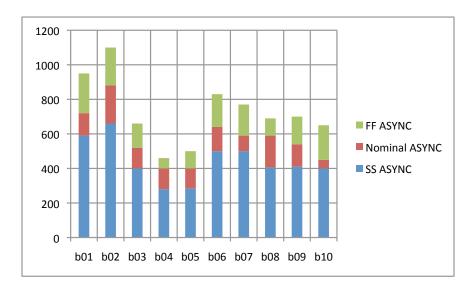

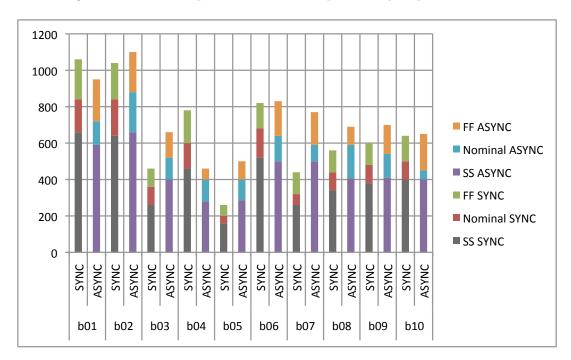

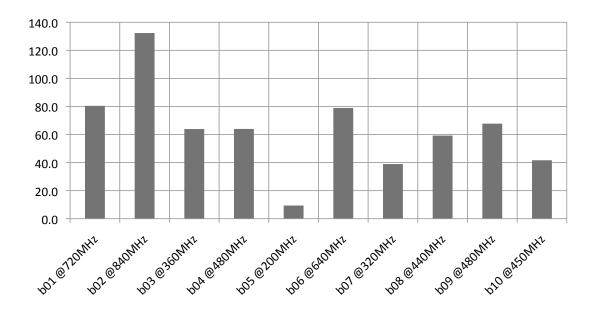

| 4.1<br>4.2<br>4.3                                                   | ITC-99 Benchmarks: Synchronous and Asynchronous Implementa-                                                                                                                                                                                                                                          | 55<br>55                                                 |

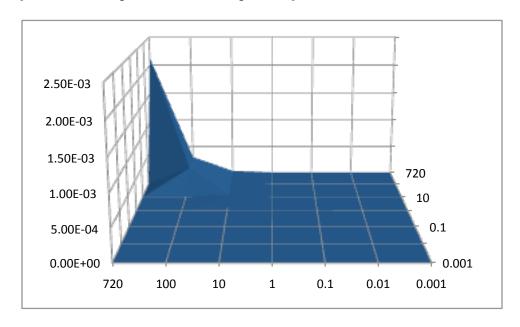

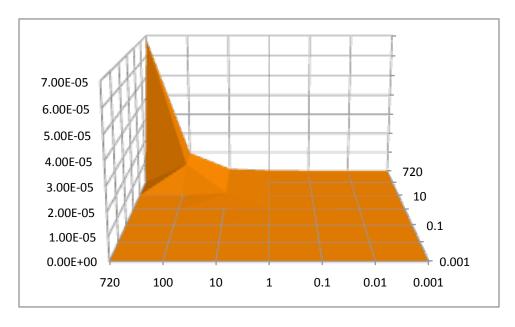

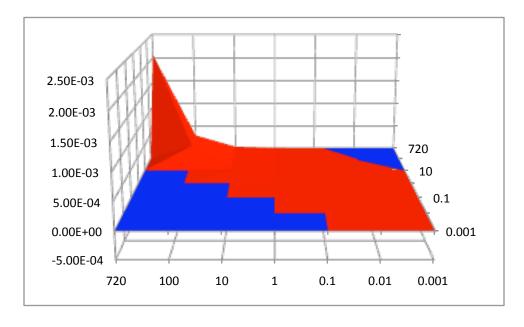

| 4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11              | Power for b01 in Watts: Asynchronous Implementation                                                                                                                                                                                                                                                  | 57<br>57<br>58<br>58<br>59<br>61<br>63<br>64             |

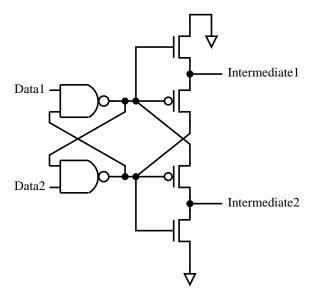

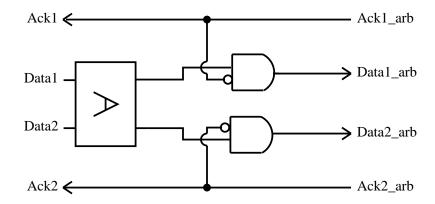

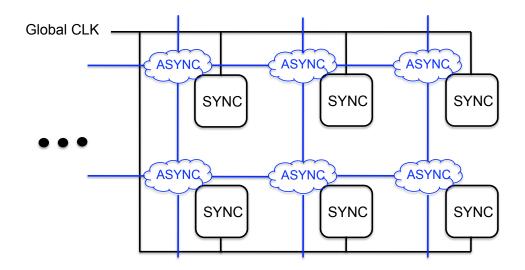

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10 | Mutual Exclusion Element with QDI handshake  On-chip Globally Synchronous Network  Synchronizer Overall Diagram  Synchronizer Detailed Diagram  Input Stage of the Synchronizer  Modified PCEHB Element  C²MOS flip-flop with conditional feedback  C²MOS flip-flop with full combinational feedback | 69<br>70<br>74<br>75<br>77<br>78<br>80<br>84<br>85<br>86 |

| 5.11                                                                |                                                                                                                                                                                                                                                                                                      | 88                                                       |

| 5.12 | Synchronous | Register | / Flip-Flop | Control Signals |  |  |  |  | 90 |

|------|-------------|----------|-------------|-----------------|--|--|--|--|----|

### List of Abbreviations

ACT Cornell's Asynchronous Circuit Toolkit

CHP Communicating Hardware Processes, hardware description language

CMOS Complementary Metal-Oxide Semiconductor

EDA Electronic Design Automation

GND Ground Power Supply Node

Netlist circuit description at some level of abstraction

HSE Handshaking Expansion

NFET n-diffusion Field Effect Transistor

PFET p-diffusion Field Effect Transistor

PRS Production Rule Set, transistor pull-up and pull-down description

QDI Quasi-Delay Insensitive

Sink data token consumer

Source data token generator

SPICE transistor-level circuit description

TSMC Taiwan Semiconductor Manufacturing Company

VDD Positive Power Supply Node

Verilog Hardware Description Language for electronic system modeling

VLSI Very Large Scale Integration

# Chapter 1

### Introduction

#### 1.1 Motivation

Complexity of modern integrated circuits continues to increase with shrinking feature size. As a result of that, timing closure, power management and undesirable transistor behavior at high operating speeds have become increasingly important and challenging to deal with [34].

The main purpose of Computer-Aided Design (CAD) tools is to help designers combat these issues. Contemporary industrial design flow is well understood, documented, and constantly being updated and improved by large-scale CAD corporations. However, the limitations of current design flow are also well-understood [6], especially in the current era of low-power/high speed VLSI, where technology scaling leads to more parasitic analog effects that are only revealed during low-level simulations at the "end" of the design cycle.

Consequently, VLSI design is becoming more complex and more time consuming. One of the primary reasons for this is a lack of *fast and accurate* low-level circuit modeling tools. Presently, if a designer wants to perform gate-level opti-

mizations, he is forced to perform slow, transistor-level simulations that can take several days to complete for a reasonable size VLSI design. Furthermore, these simulations are often infeasible, since most current designs are standard-cell based and foundries do not reveal the exact structure of their gates to the designers due to confidential intellectual property agreements. Thus, designers are forced to perform most of their optimizations only at a high-level circuit description, where no notion of transistors or even gates exists. This type of decision-making process renders crucial low-level design space optimizations unavailable. In addition, mixed high- and low-level modeling is underdeveloped and cannot be performed with all known circuit families.

Moreover, if a designer attempts to perform low-level optimizations, he is required to have in-depth knowledge of circuit implementations and circuit families. It is extremely difficult to predict which circuit family will be ideal for a given design in a particular environment. Different optimization criteria exist for different applications, design constraints, and environments.

Ideally, a designer should have the freedom of describing a design using a high level language, such as Verilog or VHDL. The tools should then aid the designer with synthesizing this behavioral description into a lower-level description (possibly a gate-level netlist). Ideally, at that point the designer should already have some guidelines about which circuit families he should consider and which he should dismiss immediately due to the synthesized circuit structure. After a subset of circuit families is selected based on the guidelines, the full design or subset of the design (depending on size and complexity) can then be automatically synthesized into transistor-level netlists for selected types of circuit families, which can then be accurately simulated at the transistor-level. At this point, the designer should have enough data to make an educated decision as to which circuit family is best

suited for their design, given their set of requirements and guidelines.

#### 1.2 Background

When selecting a circuit family, the designer has many choices. Synchronous families include static CMOS, domino logic, differential signaling, etc. However, many low-activity/high-speed applications may benefit from self-timed (asynchronous) circuit families, which offer tradeoffs in terms of throughput and/or power consumption in comparison to synchronous circuits [9]. Some potential benefits include data-driven switching activity and absence of clock circuitry, but these advantages come with the overhead of additional acknowledgement signals and potentially more complex data encoding (dual-rail signals, etc.).

Some application where asynchronous circuits have a clear advantage over conventional synchronous circuits are audio/speech processing [5] and neurobiological applications. A wide class of such designs has the property that the input signals don't change continuously; they are idle for some time, then change their value and return back to idle state. Consequently, a lot of power, if implemented in typical synchronous circuits, is wasted, because many samples of the input have the same values for a long period of time. For the purpose of eliminating the circuit power consumption when the input is stable, designers may use asynchronous design to implement signal processing operations. Asynchronous circuits are appealing for this task, since they don't have a global clock that forces periodic sampling. Unlike all the conventional synchronous circuits, an asynchronous system shuts down automatically, if the input is constant (i.e. the system is event-driven). In the applications of signal processing and neurobiological circuits, asynchronous circuits in many cases have several advantages in terms of energy consumption and complexity reductions.

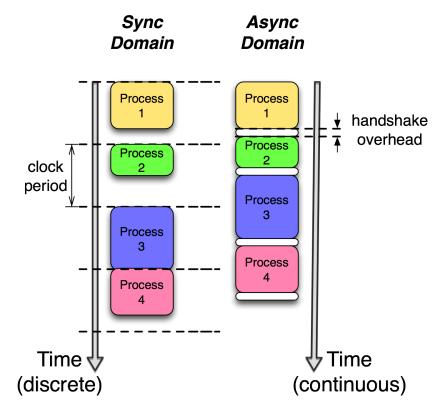

Asynchronous circuits operate without a global clock, and use handshakes to transmit and control the flow of data as shown in Figure 1.1. The data-driven nature of asynchronous circuits allows a circuit to idle without switching activity when there is no work to be done. In addition, asynchronous circuits are capable of correct operation in the presence of continuous and dynamic changes in delays [24]. Sources of local delay variations may include temperature, supply voltage fluctuations, process variations, noise, radiation and other transient phenomena.

Figure 1.1: Synchronous and Asynchronous Time Domains

We believe that asynchronous circuits are a promising area in research because many design parameters can be improved, in comparison to the well-known synchronous circuits. A brief comparison of synchronous and asynchronous circuit characteristics is presented in the table below.

|                       | Synchronous Ckts          | Asynchronous Ckts   |  |  |  |

|-----------------------|---------------------------|---------------------|--|--|--|

| Activity              | Clock-Driven              | Input-Driven        |  |  |  |

| Power Consumption     | Continuous                | Activity-Dependent  |  |  |  |

| Logical Correctness   | Delay Sensitive           | Delay Insensitive   |  |  |  |

| Temperature Variation | Breaks Circuits           | Immune              |  |  |  |

| Radiation Immunity    | Hard to Achieve           | Achieved with Minor |  |  |  |

|                       |                           | Modifications       |  |  |  |

| Fault Tolerance       | Requires Complex Circuits | Easily Achievable   |  |  |  |

#### 1.3 Proposed Toolflow Basics

In order to allow the designer to make better-informed choices with regard to circuit families, we have developed a toolflow for automatic synthesis of a given logic block into synchronous and asynchronous logic families. This automatic synthesis enables a fair and systematic comparison between different circuit family implementations. After compilation of a given digital logic block into synchronous and asynchronous implementations, we can measure power, performance, and delay characteristics. Using our flow, the designer can evaluate various circuit types and quantitatively determine under which conditions an asynchronous circuit would result in reduced delay and/or power consumption compared to its synchronous counterpart or vice versa. In this fashion, the designer can quickly obtain the cost of each implementation in terms of power, performance, and area (transistor count), at which point he can decide which implementation should be used without going through the entire synthesis/layout of all blocks.

Our toolflow also provides highly optimized, pre-compiled cell libraries for dif-

ferent logic families, both synchronous and asynchronous, which eliminates the designer's requirement of thorough knowledge of all circuit families. All our tools are also compatible with industrial standard cell libraries. Such compatibility gives the designer another degree of freedom to pick the factory supplied standard cells if they are sufficient or beneficial for a given design, or to decide that another circuit family should be considered.

#### 1.4 Asynchronous Design Methods and Challenges

For the majority of our asynchronous digital experiments, we have selected the quasi-delay-insensitive (QDI) style [24]. The advantage of this family is that the resulting circuits are robust and insensitive to process, voltage, and delay variations. Electromagnetic emissions are also minimized as compared to synchronous circuits due to the absence of a high-frequency clock signal throughout the circuit. A sample conventional asynchronous compilation method is described in Alain Martin's communicating process compilation technique [23]. It is based on a synthesis method that translates a high-level design description to circuits through handshaking expansions, and production rules. This technique facilitates physical circuit realization, where some of the decomposition in Martin's approach can be generated automatically.

The issue with all the current asynchronous toolflows is that they are not easily combined with their synchronous counterparts. One cannot easily interchange synchronous and asynchronous circuits within a design. No unified tools that could handle both circuit families exist according to the author's knowledge. In general, the lack of EDA (Electronic Design Automation) tools for asynchronous flows limits their usage in contemporary electronic systems. Most of the synthesis and simulation of asynchronous circuits is presently performed by hand, which puts

a large burden on the designer and requires in depth knowledge of the asynchronous circuit theory. In addition, methods of combining synchronous and asynchronous circuits are limited and sometimes do not satisfy the requirements of the more complex systems.

Our goal is to solve these problems and introduce a new hybrid synchronous / asynchronous toolflow that allow designers to easily build not only synchronous, but also asynchronous systems and to have an efficient way of combining these two circuit families.

#### 1.5 Toolflow Evaluation

Transistor models will inevitably deviate from the actual manufactured integrated circuits. All the results presented in this thesis are based on the theoretical models, simulations and manufacturing data from previous test-chips/test-runs. However, QDI asynchronous circuits tolerate variations between models and physical devices due to the conservative design methodology [20]. Conversely, for some aggressive synchronous circuits, more timing-closure analysis should be performed by designers using the parasitic extractions obtained after the complete place-and-route step, which is well covered in the industrial flows and is not presented in this work. For the majority of measurements and tool calibration presented in this thesis we have used the Nangate 45nm Open Cell Process/Libraries [1], commonly used for testing and exploring modern circuits and EDA flows.

For the toolflow evaluation purposes we have designed various prototypes of integrated circuits. While developing the presented toolflow, we utilized many of our own tools, described in this thesis; as well as several industrial tool packages. The following industrial tools have been extensively studied and used in our experiments; for layout: Cadence IC 6.13, Cadence Encounter, Micromagic MAX;

for high-level simulations: Synopsys VCS, Synopsys Design Compiler; for analog simulations: Synopsys HSIM, Synopsys Hspice. These software tools allow us to perform pre-layout simulations, Verilog- and VHDL- type synthesis, post-layout analysis, and verification of different digital and analog circuits.

#### 1.6 Organization of This Thesis

This thesis is divided into four major parts.

In the first part we will discuss our innovations in toolflow development. We will demonstrate a hybrid synchronous/asynchronous toolflow that uses identical mechanisms for synthesizing a given design into both synchronous and asynchronous circuits. This toolflow gives designers the flexibility of obtaining accurate power/throughput/area estimates early in the design cycle using different circuit families.

Second part of this thesis will focus on the COSIMulation tool that we have developed in order to allow designers to simulate their designs at various levels of abstraction. This tool unifies various industrial and our own digital and analog simulators to give designers an opportunity to test their designs. This tool handles both synchronous and asynchronous circuit families and has the ability of automatically connecting different types of input and output environments to the design to provide logical and timing correctness checks.

Third part demonstrates the effectiveness of our toolflow. We evaluate our gatelevel conversion methods on a set of ITC-99 benchmarks, compiling them into a highly efficient static CMOS industrial library and into our own QDI asynchronous library. We present throughput and power consumption trade-offs in relation to circuit input signal activity. We also perform a design space study based on power consumption, input activity factor and maximum supported frequency. The last part focuses on a highly efficient asynchronous-synchronous interface. This interface is most useful in globally synchronous systems, where part of the computation needs to be implemented asynchronously due to some targeted metric or design characteristic. Our interface guarantees deterministic timing of the overall system due to the implemented synchronization protocol.

# Chapter 2

### Toolflow

#### 2.1 Toolflow Comparison

#### 2.1.1 Conventional Toolflows

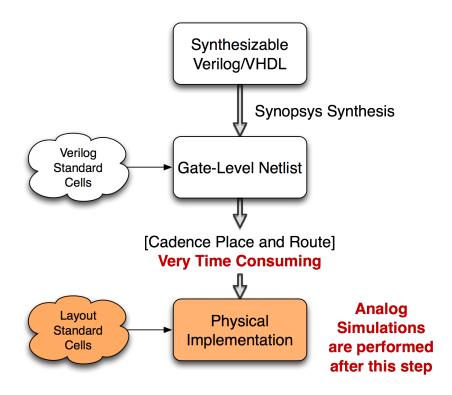

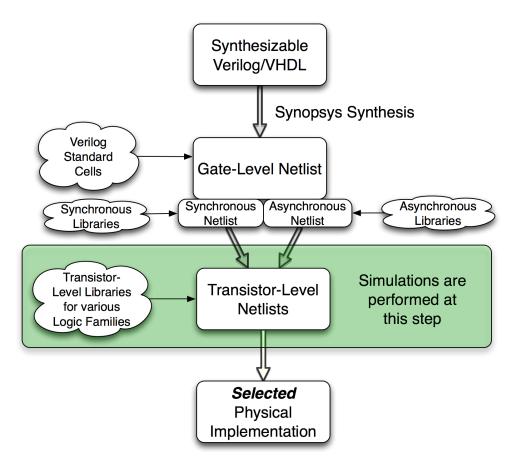

The toolflow used by the majority of companies in industry is presented in Figure 2.1. First, the designer creates a high-level Verilog/VHDL description of the circuits. Second, this description is synthesized into a gate-level netlist using a specific set of standard cells with pre-layout timing estimates supplied by the foundry. Third, the designer works with automatic place and route tools to obtain a physical (layout) implementation of the circuit – in practice, this step is not fully automatic and requires a significant amount of manual effort. At this point the layout can be extracted, but the contents of the standard cells are not revealed by the foundry. Only after these steps are completed can the designer perform analog-level simulations with the estimated parasitic elements from the layout – for the first time since the beginning of the design cycle.

The place and route step takes a large portion of the design cycle time and

Figure 2.1: Industrial Toolflow

needs to be partially or completely repeated after every modification to the design. It also takes the designer a long time to get to the first set of analog-level simulations, where many common problems, such as cross coupling, charge sharing, signal swing issues are revealed.

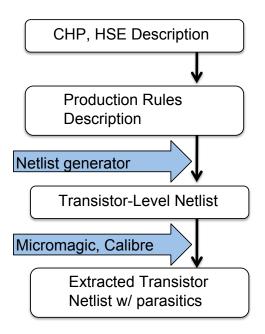

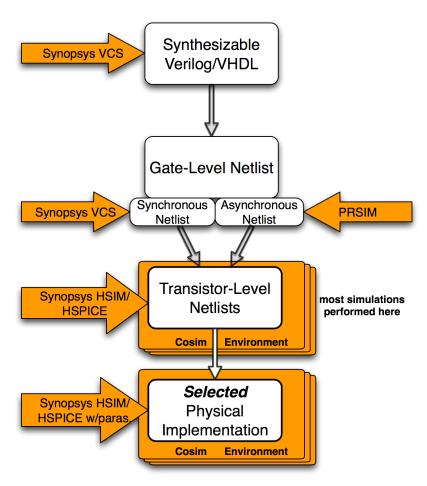

As for the asynchronous toolflow, different design teams around the world have their own toolflows. Various tools have been developed to support asynchronous circuits, however, a large portion of the design process still requires designer's intervention for synthesis and analysis. A toolflow used by Cornell's AVLSI research group is presented in Figure 2.2.

Some of the tools shown in Figure 2.2 will be briefly described later in this thesis. From the comparison of the two flows, it is obvious that synchronous and asynchronous toolflows use completely different description languages and tools. No parts of these flows may be interchanged and, thus, evaluation of synchronous

Figure 2.2: Asynchronous Toolflow

and asynchronous circuits conventionally requires a lot of work and a full understanding of asynchronous circuit operation to perform some of the manual synthesis.

### 2.1.2 Proposed Toolflow

Our proposed toolflow, shown in Figure 2.3, provides full support of both synchronous and asynchronous circuit families. It uses same exact tools to generate both synchronous and asynchronous netlists. It also allows easy modifications/adjustments for parts of the design. This toolflow eliminates all the manual labor previously required from the designer to perform asynchronous circuit synthesis.

Our toolflow also removes the necessity for the place and route step for all the preliminary design decisions and measurements. Once the design is finalized and satisfies all the metrics, the place and route step is performed only once with some minor post-layout adjustments to account for cross-talk, transmission line effects, etc.

Figure 2.3: Proposed Toolflow

In order to minimize design time and allow the designer to test various types of circuit families for a given design, we augment the industrial toolflow in the following manner. Similar to the current industrial flow, the designer creates a high-level Verilog/VHDL description of the circuits, which is then synthesized into a gate-level netlist using a specific set of supplied standard cells. At this point the designer, instead of using the "black-box" industrial cells, has a choice of using cells from various different circuit family cell libraries. For example, if the selected circuit family is synchronous, the synthesized netlist is used directly with transistor-level libraries of various synchronous families. However, if the selected

family is asynchronous or data-driven, we perform several netlist transformations, described in the next section, to obtain a logically equivalent asynchronous gate-level netlist. In this case, asynchronous libraries are attached to the obtained gate-level netlist. Presently, our tools perform the transformation of synchronous gate-level netlists into Quasi-Delay Insensitive (QDI) [24] asynchronous netlists, but it is relatively simple to perform a similar set of transformations to obtain a bundled-data asynchronous netlist, for example. The designer need **not** have an in-depth understanding of the operation of asynchronous circuits, because our tools automatically perform correct netlist transformations and attach the corresponding libraries of asynchronous components.

The advantage of our flow is that, at this early point in the design cycle, designers can perform analog simulations using industrial simulators that take into consideration most of the parasitic effects of the given design. To enable this, we estimate and annotate wiring capacitance associated with each gate's output node. Once the designer is satisfied with the simulation results, the physical implementation or layout step is performed only once using the circuit family that gave the best results for the specified metrics.

### 2.1.3 Proposed Simulator Chain

In the toolflow that we have presented, the designer has much more flexibility simulating the circuit at various pre-layout levels of development, as shown in Figure 2.4. As in the industrial flow, the Verilog/VHDL behavioral code may be simulated with an industrial level simulator, such as Synopsys VCS [4]. After compilation into gate-level description, the synchronous gate-level netlist may be simulated with the same high-level simulator, whereas in the asynchronous case we use our digital simulator PRSIM, which we describe in the next section. We

have also developed an interface to allow the cosimulation of synchronous and asynchronous circuits simultaneously at various levels of abstraction.

After our netlist transformations are performed, from a gate-level description we produce a transistor-level synchronous or asynchronous netlist that can be simulated using any of the industrial analog simulators, prior to the layout step. After the physical implementation is performed, the same analog simulator may be used again for final evaluation of the design.

Figure 2.4: Sample Simulator Chain

#### 2.2 Industrial Tools Used in the Flow

### 2.2.1 Synchronous Digital Simulator

For all behavioral level simulations, as well as for gate-level synchronous netlist simulations we have used Synopsys VCS. The advantage of such a simulator is that we can compare results obtained from circuit descriptions before and after we invoke Synopsys's synthesis tools.

### 2.2.2 Transistor-Level Analog Simulator

For all of our transistor-level simulations we have used Synopsys HSIM for larger circuits and Synopsys HSPICE for more accurate smaller circuit simulations. Our tools generate netlists that account for gate and parasitic output capacitances, as well as estimated average-case wiring capacitance to accurately represent delay and switching energy.

#### 2.3 Cornell AVLSI's Tools Overview

### 2.3.1 Asynchronous Digital Simulator (PRSIM)

The simulator we use for our experiments with asynchronous circuits is an event-driven digital simulator. It has been extended to evaluate the transient effects of temperature and supply voltage on delay if so desired. The input to the simulator is a simplified transistor-level netlist (automatically generated) in the form of event rules describing the logic. PRSIM has the advantage of performing fast digital simulations, while simultaneously testing for correct asynchronous circuit behavior.

#### 2.3.2 Verilog-to-ACT

The Verilog-to-ACT tool converts a synthesized Verilog netlist into an equivalent intermediate format gate-level netlist that hierarchically describes pull-up and pull-down transistor stacks of each gate used in the design. This tool can be used to automatically generate either a synchronous netlist or an asynchronous netlist.

The transformation from a Verilog gate-level netlist to synchronous transistor stack-level netlist is straightforward. Only the semantics of the netlist are altered to transfer Verilog-level description to an intermediate ACT description. At this stage, an appropriate transistor-level library is attached to the circuit description—various synchronous families may be used.

If an asynchronous QDI netlist is selected, the tool produces an asynchronous gate-level netlist, by performing gate level transformations based on the initial synchronous gate-level netlist. Asynchrony is completely transparent to all the previous parts of the toolflow, since prior to this step the circuit looks and behaves completely synchronous. This kind of transformation preserves the circuit structure. It replaces synchronous gates with their asynchronous counterparts, as well as inserts asynchronous-specific circuit modules, as described further.

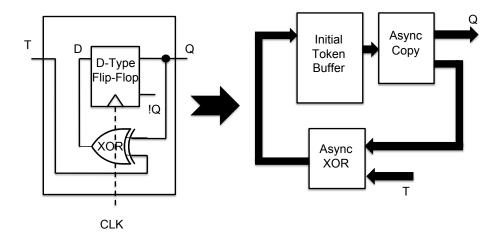

Verilog-to-ACT converts every boolean channel into a delay insensitive channel and automatically inserts copy processes for high fan-out signals and token sources for constant-value inputs. In addition, during the asynchronous transformation, all flip-flops are replaced with asynchronous initial token buffers. The performed transformations are outlined in Figure 2.5.

An example of a Verilog-to-ACT transformation, where the asynchronous netlist is produced from a synchronous netlist is demonstrated in Figure 2.6. In this figure, a synchronous netlists consist of a toggle flip-flop (T flip-flop), which is implemented by using a D-type flip-flop with it's output going to an XOR gate, along

| Synchronous Netlist    | Asynchronous Netlist    |

|------------------------|-------------------------|

| Booleans               | Asynchronous Channels   |

| Synchronous CMOS gates | Asynchronous CMOS Gates |

| VDD and GND inputs     | 1- and 0- Data Sources  |

| Dangling nodes         | Data Consumers          |

| Gate Output Fanout     | Copy Process            |

| Synchronous Flip-Flops | Initial Token Buffers   |

Figure 2.5: Verilog-to-ACT Conversion Table

with the T flip-flop's input; the output of the XOR gate is connected to the input of the D flip-flop. This is a standard way of implementing a toggle flip-flop. After the synchronous-to-asynchronous transformation takes place, the asynchronous netlist looks like the right part of Figure 2.6. D flip-flop is substituted with an initial token buffer, fan-out of two is replaced by a two-way copy process, and the XOR gate is implemented in an asynchronous manner.

Figure 2.6: Verilog-to-ACT Synchronous to Asynchronous Transformation

After the transformation is completed, the obtained asynchronous circuit emulates synchronous circuit's behavior. All the clock actions are replaced with asynchronous handshakes, but the sequencing and structure of event occurrences in the system remain untouched.

These types of transformations are suitable for small and medium sized circuits. This technique is not as efficient for large scale designs, since many asynchronous-specific design optimizations are not performed due to preservation of the synchronous circuit structure.

Eventually, for more efficient conversion, we would like to perform the synchronous-to-asynchronous transformation at a higher-level behavioral description, but that would require a complex compiler. Therefore, at this time we have decided to stay with the gate-level transformations. Once the high level transformation is implemented, we can use methods such as automated concurrent pipeline synthesis, as described by Teifel [35], to perform the asynchronous synthesis function.

#### 2.3.3 Netlist Generator

The Netlist Generator tool is used to automatically generate a hierarchical spice netlist from a previously described ACT netlist, generated by our Verilog-to-ACT tool (the pull-up and pull-down transistor description for a given circuit family's library). Values that control process-specific parameters such as gate input and output capacitances, approximated wiring loads, minimum p- and n- transistor sizing, source/drain area and perimeter, and spacing between two FET-s in the same diffusion stack are specified to allow the Netlist Generator to calculate parasitic capacitances.

#### 2.3.4 Automatic Cosimulation Environment Generator

We have created Automatic Cosimulation Environment Generator (COSIM) to allow co-simulations of an arbitrary mix of synchronous and asynchronous circuitfamilies at various levels of abstraction. The environment generator automatically creates an interface between the Verilog simulator VCS, the PRSIM asynchronous simulator, and the HSIM transistor-level simulator. This tool allows the designer to test mixed synchronous-asynchronous circuits while implementing the actual circuits using different families and different levels of abstraction. One can cosimulate a high-level Verilog/VHDL synchronous circuit description together with an asynchronous pull-up/pull-down circuit description, as well as with a transistor-level description that includes all the transistor parasitic effects and wire-load estimates. The tool can also automatically create an appropriate test-bench for a given circuit with both input and output environments. COSIM will be described in more detail in Section 3.

#### 2.3.5 Circuit Family Libraries

We have created transistor-level libraries for various circuit families that give us the capability to synthesize our circuits into their corresponding transistor-level netlists using different synchronous and asynchronous families. Post synthesis (pre-layout) analysis allows us to pick the best circuit family depending on a targeted metric such as power consumption, area, throughput, latency, etc.

Delays and capacitances are based on the logical effort model and are calibrated against a realistic technology node in all our simulations. Please note that it is straightforward to calibrate the libraries for a different/new technology node. The only parameters that are changed with a new process are the circuit properties and transistor descriptions – minimum size, parasitic parameters, mobility values, etc. – used for the Netlist Generator configuration.

For the asynchronous library style we have implemented the QDI circuit family [18] due to its robustness to delay, temperature, and process variations as described in the Introduction section of this paper. We have implemented our standard cells

using PCEHB type handshake reshufflings [16]. Other asynchronous logic families such as bundled-data may be used instead with appropriate netlist transformations.

# Chapter 3

### **Automatic Cosimulation**

# **Environment Generator**

#### 3.1 Motivation

The main reason for creation of an Automatic Cosimulation Environment Generator (COSIM) is current designer's inability to perform mixed-level synchronous and asynchronous circuit simulation at various levels of abstraction. According to the knowledge of the authors, there are presently no tools that can automatically perform such synchronous/asynchronous circuit simulations, along with proper modeling of the interfaces between the two domains.

With the complexity of current chip design increasing drastically, it is becoming impossible to perform transistor-level simulations of the entire chip. We would like to have an option of performing partially transistor-level and partially high-level behavioral simulations of the circuits.

As for simulation of purely asynchronous or mixed synchronous-asynchronous

systems, another problematic part of the simulation is creating the correct testing environment. In order for an asynchronous environment to function correctly, it has to support a number of different types of channels, have the ability to properly assert data validity and enable signals in order to support various types of asynchronous handshakes. Creating a proper environment is not a trivial task. Implementing such environment at transistor-level becomes very complex and, often, the obtained environment doesn't check all the possible scenarios that can lead to a circuit malfunction. Thus, we would like to implement this environment at a higher, behavioral description level. This type of environment must not interfere with circuit operation, but at the same time must perform extensive circuit testing using various input signal patterns and using different timing situations. Also if we have such environment written at higher level of description, it will be very easy to isolate this environment into a separate circuit domain so that all our throughput, area and power measurements are not influenced by the environmental artifacts that should not be accounted for during measurements.

Presently Synopsys tools, such as HSIM and Nanosim offer some "hooks" to perform cosimulations of behavioral-level and transistor-level descriptions. Unfortunately, these hooks require a lot of manual work to setup such a cosimulation. This work has to be repeated for each circuit that is being tested and it requires thorough understanding of the circuit's operation to setup all the input and output streams correctly. Also, Synopsys provides no support for testing asynchronous circuits or mixed synchronous /asynchronous circuits, which is the major focus of our work.

As described later in this section, we invoke several modern digital and analog simulators (some of these are simulators created by the AVLSI group here at Cornell). We offer designers to invoke their circuits at various levels of abstraction, which allows trading higher accuracy of simulation for shorter simulation time and vise versa.

In the work outlined in this thesis, we go further than just cosimulations of different circuit families, but we also integrate all the synthesis and measurement tools that provide a full package in synchronous/asynchronous circuit testing and analysis. The following industrial and Cornell's tools were utilized in COSIM's development and are briefly explained in this thesis: Synopsys HSIM, Synopsys VCS, Cornell's PRSIM, Cornell's TLINT, Cornell's Netgen.

All the COSIM development illustrated in this section has been done in collaboration with my colleague *Carlos Tadeo Ortega Otero*, who is also a Ph.D. student in Cornell's AVLSI research group.

#### 3.2 Vision

Ideally, we would like to have a unified interface that could be used by designers for simulation run control, as well as all pre- and post- circuit processing, such as compilation into a spice-type netlist, power measurements, area estimates, throughput measurements. We would also like to have minimal amount of setup performed by the designer, but at the same time we don't want to take away all the functionality provided by the tools. So in most cases we create a cosimulation environment with a default set of parameters that provide a good simulation time / accuracy tradeoff. The designer may easily modify these parameters without going back to any of the Verilog/VHDL/SPICE files. All the parameters for all tools may be specified in the top-level simulation setup file, the only file that the designer has to create in order to invoke all the tools that we use. The designer never specifies any simulator setup or post-processing commands; he only specifies the necessary simulation parameters and the circuit nodes he would like to monitor. COSIM

automatically invokes he correct sequence of commands to run the appropriate tools in the correct sequence.

In order to connect Cornell's and Synopsys's simulators we use a VPI (Verilog Procedural Interface) created here at Cornell by our advisor. Synopsys's VCS natively supports VPI-type calls, which allows us to connect our own event-rule digital simulator PRSIM, VCS and HSIM. We can then guarantee proper interaction between simulators that are working with different levels of circuit abstraction. VPI for connecting VCS and HSIM is provided by Synopsys, but requires quite an amount of manual setup and compilation; we take that burden off the designer and perform all the setup automatically as well.

As mentioned previously, we would like COSIM to generate all input pattern generators (called sources) and output interfaces (called sinks or buckets). For source, the only information the designer has to provide to COSIM is an input stream file in text format, or to pick the type of input signal probability distribution he would like to use. COSIM automatically detects the types of channel that it is dealing with. It then connects appropriate sources and sinks. Sinks in COSIM can perform several functions: they can simply monitor the output; they can compare the outputted values with a set of predefined values; they also can perform handshakes at the output in case of QDI asynchronous circuits. All of this functionality is built into COSIM and the designer has to only select what type of buckets to use.

### 3.3 Auto Simulation Setup

In the process of creating COSIM, one of the major tradeoffs that we were facing was the amount of manual control that should be given to the designer during the simulations setup. More control requires more in-depth understanding of the circuit's operation, as well as better understanding of the *correct* environment behavior.

We decided to require the designer to perform as little setup as possible, with COSIM making the educated guesses as to circuit's behavior and it's interfaces with the environment. For example we have an option of automatically adding source and sinks to all the circuit's inputs and outputs. COSIM decides how to reset these sinks and sources, and what type of input pattern distribution to pick. However, the designer always has an option of specifying as much detail as he would like (for example for all the critical signals), and afterwards COSIM can perform the rest of the setup automatically.

This approach allows the designer not to have in-depth understanding of all the tools that are used in the simulation process (though such "ignorance" is not recommended). If auto-connection is used at inputs and outputs, the designer does not have to be familiar with the exact handshake reshufflings (though if non-standard reshuffling is used in the circuit, this may lead to a deadlock during the simulation), pattern setup, etc.

Majority of the simulation parameters have default values that are assigned to them. The designer may override all of these values in the unified setup file. The default values were chosen to provide, in our opinion, a reasonable degree of simulation accuracy while still keeping a practical simulation time.

COSIM automatically performs various types of checks during the simulation run. These include node capacitance calculation check, periodic excessive current check (test for shorts), dangling nodes check (nodes that are not driven), unconnected node check, non-switching node check (except global signals like power and ground), power high-impedance node check, rise/fall time check, etc.

All the feedback from COSIM and from the simulators is collected and reported

back to the designer through various report files. COSIM warns the designer about potential errors in the designer's setup; it also informs the designer about the setup that it performed automatically to make sure that it didn't make any assumptions that are not consistent with the designer's implications.

#### 3.4 Overview

COSIM is a PERL-based program that functions in the following manner. A designer creates only one unified setup file in the XML format. COSIM parses that file and sets up all the necessary simulators, interfaces between the simulators and prepares all the measurement and post-processing tools.

COSIM passes the main simulation directives to the VCS simulator that monitors the run at the top level of abstraction. COSIM creates the top-level Verilog-based wrapper that has the global parameters, such as simulation time, circuit module, global variables, all the necessary wiring connections, signal names, top-level delays, timescale, top-level circuit inputs and outputs, etc. The created Verilog wrapper also connects the selected Verilog environment (sources and sinks) to the design. Connections to PRSIM signals for asynchronous digital circuits described in ACT are also performed here.

COSIM also creates a spice wrapper, if this option is selected, for simulating transistor level netlists (including extracted circuits). The spice wrapper specifies all the necessary low level details and parameters to correctly invoke HSIM simulator. Among these parameters are supply voltage, output file format, simulator accuracy parameters, Verilog rise and fall times for interface signals, analog iteration method for initial operating point calculation. A table with some of the variables that may be optionally set in the unified interface file (and will appear in the spice wrapper) is presented later in this chapter of the thesis. Spice wrapper

also sets up all the analog voltage and current sources, global variables, connections with the transistor-level circuits, all the measurement commands, etc.

Besides the main two wrapper files for VCS and for HSIM, COSIM automatically creates various other files that are transparent to the designer under most circumstances. If designer selects an ACT-type file and specifies that he wants to simulate the circuit at transistor level, i.e. by invoking HSIM simulator; COSIM automatically runs Netgen, and generates a top-level spice, as well as all the spice subcircuit instances that were used in the original ACT description. Similar to the command-line Netgen run, COSIM reads in a Netgen configuration file, which should be either in local directory where COSIM is run, or specified as a netgen\_cf variable in the unified interface XML file.

We use a simple JAVA-based parser to determine the names of the circuit ports in all defproc-s of the ACT file in order to correctly connect these ports in the Verilog wrapper and the spice wrapper. If the designer uses "!" and "?" to indicate directionality in the top-level defproc of the ACT file, we also parse this information and later use it if the designer wants to automatically connect sources and sinks to the given module. In that case directionality only has to be indicated at the top level module. Besides determining the names and directionalities of the ports, we also use the parser to determine the types of channels that we are dealing with. With that information, the user doesn't need to specify channel type in the XML file, since this information is obtained automatically.

When running Netgen directly from COSIM, several additional files are produced, that do not appear during a command-line Netgen run. These files have to do with connection of ACT-type modules to VCS. COSIM produces a file that contains the parsed channel types and names (as mentioned previously), located in the \*.act.AUX\_PROC\_PARSE. It also produces a file with top level Verilog mod-

ule connections that specify input, output types for the Verilog wrapper, located in \*.act.v. We also produce a \*.act.v.port\_info file which contains all the channel name equivalences between Verilog and ACT. Verilog by default has no notion of channels, it only works with wires; we thus have to mangle some names for Verilog, since it does not accept some of the characters used in ACT naming. These files are transparent to the designer and will not be described in further detail here.

When setting up the VCS-HSIM mixed signal simulation, COSIM creates a file call cosim.cfg, which holds several HSIM command line arguments that are used in the cosimulation initialization. Specifically, the file contains the names of all the modules that need to be simulated in the analog (transistor-level) mode. This file also sets up several initialization arguments, like the name of the spice wrapper. This file is also transparent to the designer.

Another important file that COSIM creates automatically is nsda\_cosim.sp. This file is passed during the cosimulation initialization to the HSIM analog simulator. This file contains the top level spice module with all the port names that correspond to the appropriate names of the Verilog-type environment (sources and sinks). The main purpose of this file is to indicate to the simulators the VCS-to-HSIM and HSIM-to-VCS interface signals. PRISM connections are treated similar to VCS connections; signals from PRSIM first go to VCS and then to HSIM, if desired. Once the interface signals are identified the simulator automatically performs analog-to digital (HSIM-to-VCS) and digital-to-analog (VCS-to-HSIM) conversion of the appropriate signals to guarantee correct communication between the digital and analog simulators. nsda\_cosim.sp is essential for passing values back and forth between the two simulators. This file is also transparent to the designer.

While setting up the proper environment for the circuit that is being tested, COSIM parses all the interface channels specified by the designer in the unified interface XML file and automatically determines the channel types from the ACT file (if the top level module was described in ACT-format), as stated earlier. If some of the ports of the top-level module are not specified in the XML file, COSIM will notify the user that there are dangling ports in the module. For the input channels, the user has an option of either passing a file with a given input stream, or selecting an input probability distribution. If nothing is selected, COSIM will use a uniform input probability distribution for the channel by default. As for the output, the user specifies whether he wants to: simply watch the values of the channel, record the values, perform handshake, and/or compare the values to a predefined output pattern. By default, COSIM will simply watch and record the outputted values on every channel.

Once all the circuit interface channels have been identified, COSIM creates an environment\_used.v file which contains all the proper sources and sinks along with their options for all the input and output channels (including CLOCK source, if there is one). COSIM looks up the required sources and sinks in the environment library that we have created. This library contains various flavors of the environment elements. The description of our library will be provided in a later section. environment\_used.v contains only unique instances of each type of sinks and sources used. This file is created automatically and passed to the simulators during the VCS-HSIM cosimulation initialization.

### 3.5 Functionality

The main purpose of COSIM is to minimize the effort required by the designer to simulate his design using various levels of hardware abstraction, and using different circuit families, including mixed synchronous/asynchronous circuits. COSIM simplifies this process and allows the designer to perform circuit simulation with only

rough understanding of all the simulators and circuit implementations. COSIM also performs a task of automatically creating a testing environment for the design.

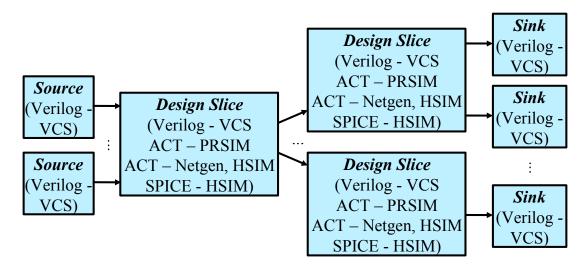

As mentioned previously, the current COSIM implementation requires the designer to create only one top-level unified interface file in the XML format. I shall refer to this file as *cosim.xml*. This file allows designers to perform connections of various circuit parts implemented in different description languages and at different levels of abstraction. An example of such a design is represented in Figure 3.1.

Figure 3.1: Overview of COSIM's Functionality

The testing environment (sources and sinks) for all the designs is created in Verilog, as shown in Figure 3.1. This allows us to perform more complex input/output value comparisons, logical correctness and timing correctness checking. In Verilog we can easily implement various functions that help designers debug their circuits.

All values originate in VCS and are then passed to PRSIM or HSIM; as for the outputs, all the values travel back to VCS, where various checks are performed (based on designer's selection in cosim.xml) to determine whether the circuit is functioning properly.

As for the actual circuit implementation (outside of the testing environment),

labeled as *Design Slice*-s in the above figure, they may be implemented in Verilog, ACT or in spice formats. If the circuit part is implemented in ACT, the designer has an option of either using PRSIM for simulation, or, alternatively, of running Netgen and generating a transistor-level description of his circuit and then simulating it using HSIM (assuming all the production rules are properly sized by the designer).

These *Design Slice*-s may be connected in cosim.xml in any arbitrary sequence, as depicted. Sequential and parallel compositions are both allowed. Any organization of Verilog, ACT and spice modules is allowed. The designer also has the option of implementing sources and sinks internally in his circuit, however, most of the time that would limit the testability of the circuit, which is why we advice designers to use our *smart* Verilog environment.

If an improper connection is performed in cosim.xml, or a violation occurs in one of the sinks or sources (timing violation, value mismatch during comparison, etc.), COSIM will inform the designer of this violation and may terminate the simulation if desired by the user.

For each top-level module (most of the time just one), the designer needs to specify some information in cosim.xml. Specifically, the designer indicates:

```

< circuit \ sim\_type = "spice" \ file = "prs/buffer.act" \ instance = "pcfb\_buf" \ file\_type = "act" \ name = "n1" > \ ...

```

</circuit>

The description of all the parameters for the circuit module is provided in the following table. Source and sinks should also be included within the above *circuit* description block, as discussed later on.

#### Module Setup

| sim_type="spice"          | determines which simulator will be invoked     |

|---------------------------|------------------------------------------------|

|                           | during simulation: spice, verilog, act         |

| file="my_filename"        | name of file with circuit description          |

| instance="top_level_name" | name of top-level instance                     |

| file_type="act"           | description language used: spice, verilog, act |

| name="my_name"            | arbitrary name for COSIM's internal purpose    |

|                           | and measurement reports                        |

| uses_blackbox="0"         | use this option only if foundry cells with no  |

|                           | transistor-level descriptions are used in cir- |

|                           | cuit module                                    |

Few examples of the simulation types follow below.

sim\_type = "spice" and file\_type="act" : run netgen and VCS/HSIM cosimulation sim\_type = "prsim" and file\_type="act" : run PRSIM/VCS cosimulation sim\_type="verilog" and file\_type="verilog" : run only VCS simulation

Instance name is used in Netgen to specify the top-level instance and is a required parameter. Channel type, does NOT need to be specified, since COSIM parses all the ACT *defproc* definitions, as mentioned previously.

Once this information is provided for top-level module(-s), designer writes directives for all the necessary module and environment connections; specifies the mandatory parameters, such as paths, tool configuration files locations; specifies the optional parameters if desired; and runs the simulation by invoking COSIM and passing cosim.xml as the only parameter. COSIM performs the rest of initialization and setup automatically.

Once the designer invokes COSIM, the cosimulation initialization begins. If there were any problems found in cosim.xml, or any other tools (like Netgen, TLINT, etc.), COSIM immediately outputs this error to the user. If the error leads to termination of any of the tools, COSIM will stop the setup and inform the designer of a terminal error. If the error was not terminal, COSIM will print it to the screen and into a log file, and keep going either until a terminal error occurs or until cosimulation finishes.

As the cosimulation proceeds, COSIM will report the time progress of the simulation, as well as any events that happen at the environment's sources and sinks. Most of the information outputted by COSIM and the simulators goes to the screen and to the log files. A brief description of all the important output files will be provided in a later section.

Once the simulation completes, COSIM will run any post-processing trace file manipulations, if the designer selected this option. For example if designer selected to run TLINT, a \*.trace and \*.names files will be produced and TLINT will be initialized once the cosimulation completes.

If the user selected to perform frequency and/or power analysis in cosim.xml, COSIM will produce a file called hsim.mt that will contain all the results from the power and throughput computations performed in HSIM. Presently, the user may select a time window of when to perform such analysis (reset time is usually omitted from such computations). The user may select to calculate node capacitance (set to all nodes calculation by default), subcircuit power calculation (static and dynamic, depending on the input signal pattern), node voltage monitoring. By default the voltage values of all nodes is calculated and recorded by HSIM into the \*.fsdb file format. This allows the designer to view waveforms of all nodes after the simulation finishes using CSCOPE waveform viewer or any other compatible viewer.

If power/frequency analysis was chosen, COSIM will setup HSIM and TLINT to output the results of all computations. Total circuit average and maximum current and power, subcircuit average and maximum current and power, subcircuit node average and maximum voltage, node capacitances will be reported by HSIM. The results of TLINT run, including slew rate violations, incomplete transitions, charge sharing problems, throughput will be reported back to the user as well.

Besides the above measurements, the user may select to perform additional checks in cosim.xml. These checks are performed in HSIM and assume that at least part of the circuit is implemented at transistor-level. These checks include bulk forward bias check, diode junction check, large current check (value, period), rise/fall time check, high impedance node check, inactive node check.

In order to run Netgen and TLINT, the user must specify the paths to Netgen's and TLINT's configuration files in the appropriate fields of cosim.xml. Also to correctly output TLINT compatible trace file, the designer must have a proper library libALINT.so in the local directory, where COSIM is run. The environment.v file with all the environment library elements must reside in the same location as cosim.pl (COSIM's executable). If the designer wants to use a cosimulation with PRSIM, appropriate vpi.o file must reside in the local directory as well.

Next few sections will go over some mandatory and optional parameters as well as how to perform environment connections and how to create interactions between various modules in cosim.xml.

### 3.6 Common Setup Parameters

As described in the previous section, COSIM is controlled through a unified interface XML-based file. In this file we specify mandatory and optional parameters that control all simulators (PRSIM, VCS, HSIM), as well as setup all the postsimulation measurements and analysis.

Mandatory parameters include settings that are essential to the VCS/HSIM/PRSIM cosimulations. These simulators will not function properly if these parameters are not specified correctly. Among these parameters are:

- location of cosim.pl, which is the PERL-based executable for COSIM;

- global Vdd value (this value **must** match the value specified in the TLINT configuration file, otherwise the simulation will fail);

- simulation time, which is used both in VCS and in HSIM setup;

- Verilog time scale, which specifies the default time unit for all the values past to Verilog and the time precision with which HSIM and VCS are run (smaller time step leads to slower, but more accurate simulation);

- location of Netgen and TLINT configuration files (as described previously);

- length of \_pReset and \_sReset, which control the asynchronous reset, \_sReset pulse should be longer than the \_pReset pulse (and should enclose \_pReset) to make sure that all asynchronous circuits are in a correct state, before they go into operating mode.

Additional parameters worth mentioning separately are the settings that have to do with the correct HSIM cosimulation setup:

- measurement start time signifies to HSIM when to start recording values for power/frequency measurements (typically after circuit reaches steady state, if applicable);

- measurement stop time signifies to HSIM when to stop recording values for power/frequency measurements (can be the end of simulation);

- device models are either passed to HSIM as a .spi file or a .lib file, depending on what kind of models are supplied by the foundry;

- device model type specifies which models should be used, i.e. TT; if this

option is provided in the model file designer can select typical, fast, slow,

etc.;

- model aliases set name equivalence classes between model names used in the library files and model names used in the spice files that were generated by Netgen or by another tool that was used

- HSIM globals, other than Vdd and GND, should be listed if more than one supply is used in the circuit, e.g. VSS;

- HSIM trace output type specifies the HSIM trace file format: fsdb is used by waveform viewers, such as CSCOPE, alint is used by TLINT post-processor;

- module inactive current specifies the current, below which HSIM may start ignoring the subcircuit in terms of transistor modeling, and assume that the subcircuit is inactive.

A full list of all important parameters, along with their brief descriptions, is presented in the tables below. For more detailed information regarding the HSIM internal variables that are not described below, please refer to the Synopsys user manuals that can be found on Synopsys Solvnet website.

# **Mandatory Parameters**

| PARAMETER                   | DEFAULT | DESCRIPTION                                |  |

|-----------------------------|---------|--------------------------------------------|--|

| cosim.pl_path               |         | path to automatic environment gen-         |  |

|                             |         | erator cosim.pl                            |  |

| vdd                         |         | global Vdd value for the circuit           |  |

| sim_time                    |         | length of your simulation                  |  |

| timescale                   |         | VCS timescale                              |  |

| $\mathrm{netgen\_cfg}$      |         | netgen configuration file name with        |  |

|                             |         | path                                       |  |

| _sReset_time                |         | sReset length in time units (ns)           |  |

| _pReset_time                |         | pReset length in time units (ns)           |  |

| measurement_start_time      |         | simulation time when designer wants        |  |

|                             |         | to start taking measurements               |  |

| measurement_stop_time       |         | simulation time when designer wants        |  |

|                             |         | to stop taking measurements for            |  |

|                             |         | power, etc.                                |  |

| insert_inverters_on_outputs | no      | yes if you wan to perform power anal-      |  |

|                             |         | ysis using 2 inverters on interface        |  |

|                             |         | channels with separate power source        |  |

| inverter_size_um            |         | takes effect only if $yes$ to previous pa- |  |

|                             |         | rameter; pmosWidth: pmosLength:            |  |

|                             |         | nmosWidth: nmosLength in microns           |  |

|                             |         | for each of the two inverters inserted     |  |

|                             |         | on every Verilog output                    |  |

# Optional Simulation Setup Parameters

| device_model_lib       |          | device model library if using a spice     |  |

|------------------------|----------|-------------------------------------------|--|

|                        |          | .lib format                               |  |

| device_model_type      |          | device model type if several are pro-     |  |

|                        |          | vided, for example TT                     |  |

| additional_spice_files |          | use this if you need to include addi-     |  |

|                        |          | tion spice files; can also be used for    |  |

|                        |          | models if the format is appropriate       |  |

| nmos_model_alias       |          | specify aliases for nmos transistors,     |  |

|                        |          | use spaces; order matters: usu-           |  |

|                        |          | ally netlist-file names first, model-file |  |

|                        |          | name last                                 |  |

| pmos_model_alias       |          | specify aliases for pmos transistors,     |  |

|                        |          | use spaces; order matters: usu-           |  |

|                        |          | ally netlist-file names first, model-file |  |

|                        |          | name last                                 |  |

| hsim_globals           | Vdd, GND | any global signals, like vcc, vsin; omit  |  |

|                        |          | Vdd and GND, as these two are de-         |  |

|                        |          | clared by default                         |  |

# Optional HSIM run Parameters

| HSIMOUTPUT    | fsdb&alint | trace file type, fsdb used for Cscope, alint used for TLINT; fsdb&alint-both |

|---------------|------------|------------------------------------------------------------------------------|

|               |            | are produced with this setting                                               |

| HSIMSPICE     | 3          | device model accuracy: 03 (3-most ac-                                        |

|               |            | curate, 0-least accurate); to speed up                                       |

|               |            | simulation, the MOSFET model can be                                          |

|               |            | simplified                                                                   |

| HSIMSPEED     | 1          | simulator speed & precision; the value                                       |

|               |            | can be any integer from 0 to 5; higher                                       |

|               |            | speed values cause faster simulation                                         |

|               |            | speed at reduced simulation precision                                        |

| HSIMANALOG    | 1          | -13, controls the complexity of analog                                       |

|               |            | simulation algorithm; the higher the                                         |

|               |            | value is, the more precise and time-                                         |

|               |            | consuming the analog simulation algo-                                        |

|               |            | rithm will be                                                                |

| HSIMALLOWEDDV | 0.1        | the time step size is dynamically ad-                                        |

|               |            | justed so that each node voltage change                                      |

|               |            | over the time step is limited by the                                         |

|               |            | value defined by HSIMALLOWEDDV                                               |

| HSIMITERMODE  | 1          | the HSIM iteration control parameter;                                        |

|               |            | can be set integer from 0 to 2; 2-highest                                    |

|               |            | accuracy, 0-lowest                                                           |

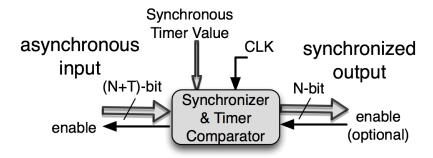

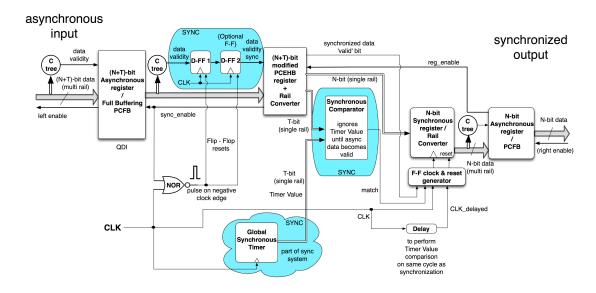

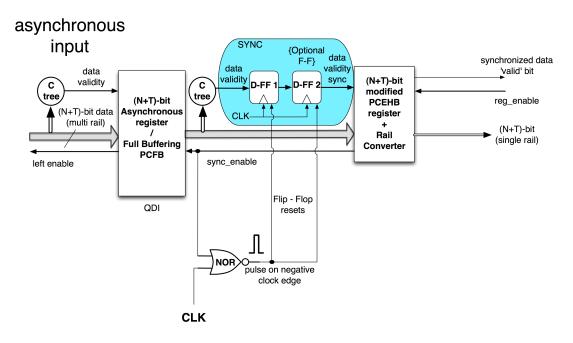

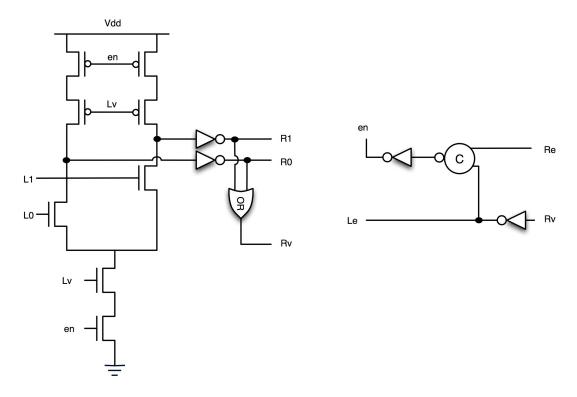

# Optional HSIM run Parameters Continued