# ULTRA NARROW SILICON FETS INTEGRATED WITH MICROFLUIDIC SYSTEM FOR SERIAL SEQUENCING OF BIOMOLECULES BASED ON LOCAL CHARGE SENSING

#### A Dissertation

Presented to the Faculty of the Graduate School

of Cornell University

In Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by Ali Gokalp Gokirmak January 2006

# ULTRA NARROW SILICON FETS INTEGRATED WITH MICROFLUIDIC SYSTEM FOR SERIAL SEQUENCING OF BIOMOLECULES BASED ON LOCAL CHARGE SENSING

## Ali Gokalp Gokirmak, Ph.D.

### Cornell University 2006

Ultra-narrow channel silicon field effect transistors (FET) with suspended gates, integrated with on-chip micro-fluidic delivery system are demonstrated. These devices are designed to be used for serial sequencing of DNA, RNA and proteins, by detecting the local charge variations along these molecules as they are passed between the gate and the channel of the FETs in an aqueous solution.

Devices are fabricated with down to 5 nm high tunnels passing between the gate and the channel of the FETs, integrated with larger scale micro-fluidic delivery system. The smallest fabricated active area width is less than 10 nm. A silicon nitride based shallow trench isolation (STI) scheme is developed in order to accommodate fabrication of the tunnels going through the FET, through removal of sacrificial silicon dioxide in HF.

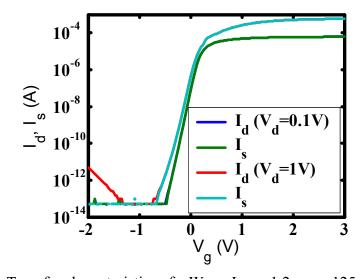

A device architecture with an independently controlled side-gate, surrounding the active area, is developed to suppress the edge related leakage currents and allow further scaling of the device width while achieving high sensitivity. The side-gated devices are fabricated as nFET prototypes using thermally grown silicon dioxide gate insulator and silicon nitride STI. The leakage currents are suppressed below 50 fA down to 70 nm gate length with the application of a negative side-gate bias.

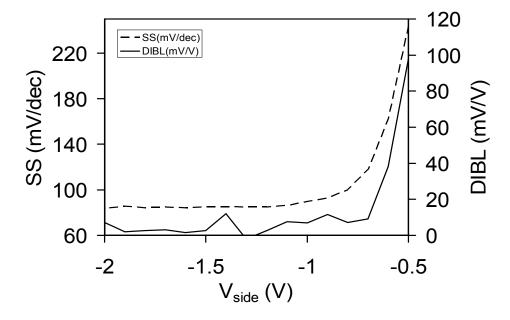

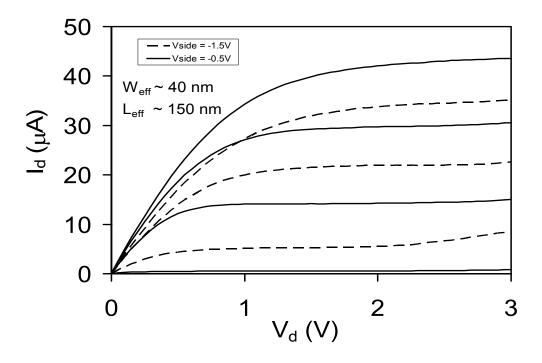

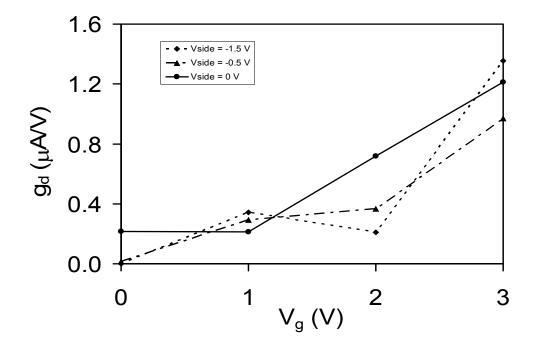

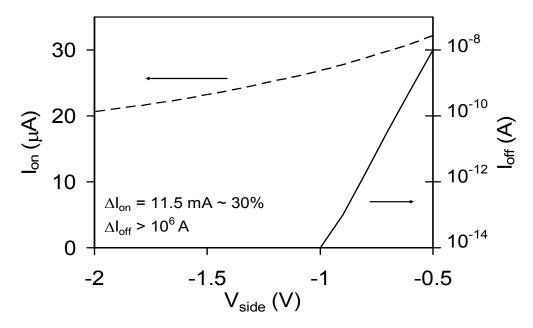

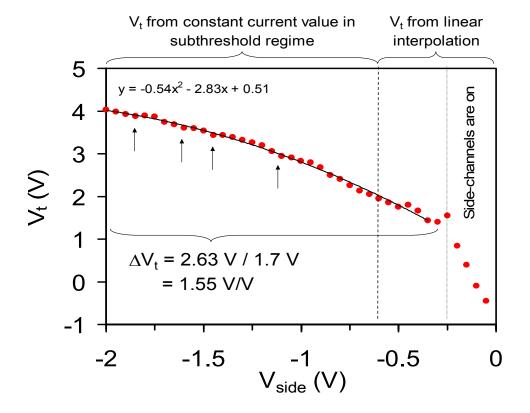

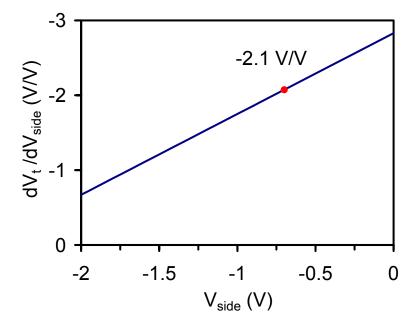

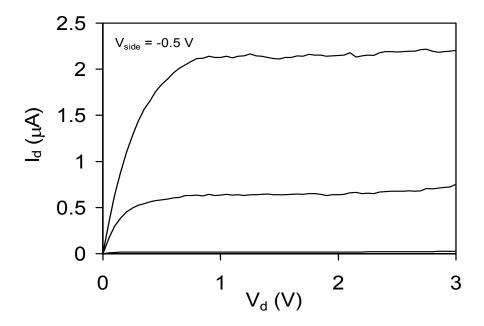

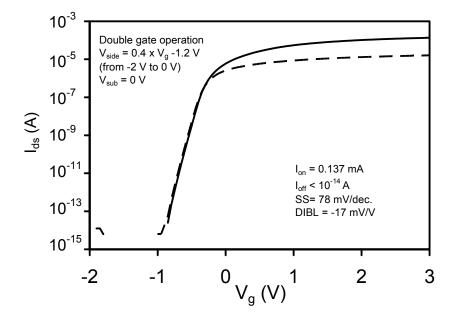

Side-gated sub-10 nm wide devices exhibit threshold voltage tunability in a range exceeding 2.5 V and with a maximum sensitivity of  $\delta V_t/\delta V_{side} > 2$  V/V. Wider channel devices with gate lengths less than 70 nm retain  $I_{on}/I_{off}$  ratios exceeding  $10^9$

and achieve drive currents exceeding 1.5 mA/µm. Narrow channel devices with 150 nm gate length show less than 5 mV/V drain induced barrier lowering. With these performance parameters, side-gated device geometry is a promising candidate for future generation low-power, and higher performance circuits. The possibility of using this device geometry as a side-trapping FLASH memory structure is also demonstrated.

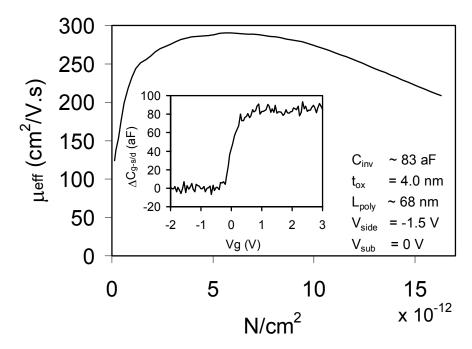

A capacitance measurement technique is developed to achieve aF resolution using an instrument with 0.1 fF resolution at 1 MHz utilizing the random fluctuations. These capacitance measurements, performed on the small scale devices, are used to extract effective device dimensions, carrier density and effective carrier mobilities.

#### BIOGRAPHICAL SKETCH

Ali Gokirmak was born in Van, Turkey. He has completed his early education in Istanbul, Turkey. After finishing his high school education at Kadikoy Anadolu Lisesi in 1994, he started his undergraduate education at University of Maryland at College Park. He received his Bachelor of Science degrees in electrical engineering and physics from University of Maryland at College Park in 1998. He joined the M.S./ Ph.D. program in Department of Electrical and Computer Engineering at Cornell University in 1998. His research interests include applications of nanostructures, nanofabrication technology, small-scale MOSFETs for sensors, logic and non-volatile memories, quantum confinement effects in restricted geometries in MOSFETs, integration of electronics with MEMS/NEMS structures for RF and non-volatile memory applications and electrical measurement techniques.

.

To my parents, Nevin and Hikmet Gokirmak

#### **ACKNOWLEDGMENTS**

I would like to primarily thank my parents who have been always supporting me during my education over the years. It would not be possible for me to continue my education without their ongoing support. I would also like to thank my brothers, Hasmet and Hakan, my sister Nimet and sister-in-law Nurcan for their support.

I would like to thank my advisor, Prof. Sandip Tiwari for his guidance and providing me with the necessary tools for the completion of this thesis and the very friendly research environment formed in our research group, and my committee members Prof. Eastman and Prof. Burhman for serving my advisory committee.

I would like to thank my wife and a member of our research group, Helena Silva for her support and company over the years. I would like to thank Jeremy Wahl for his help with Labview<sup>TM</sup> programming and processing at CNF at the very beginning of our research work. I would also like to thank Helena and Jeremy, who were the first students of Prof. Tiwari along with myself, for initiating a very friendly research environment in our research group. I would also like to thank the other group members, Arvind Kumar, Uygar Avci, Christianto Liu, Lei Xue, Hao Lin, Moon Kim, Sang (Kevin) Kim and Sudu Chae for their continuing support, fruitful discussions and friendship over the years. I would also like to thank our friends, Amit Pharakya, Venkat Narayanan, Udayan Ganguly, Kursat Araz, Serhan Ardanuc, Hazer Inaltekin and Mandy Esch in our department and CNF for keeping up the spirit and making it a welcoming environment at Cornell University.

I would like to thank IBM for supporting part of my graduate education through an IBM Research Fellowship, and my fellowship mentor Kathryn Guarini for her help. I would like to thank Arvind Kumar, Phil Oldiges, Omer Dokumaci and

Hussein Hanafi at IBM T. J. Watson research center for their guidance and help through my internship at IBM and the helpful discussions over the years.

I would also like to thank the CNF staff members who have been making it possible for me to successfully complete the fabrication process of my devices.

I would like to thank Gurbuz Gunes for his friendship, help and guidance and being a role model during the years that he was a graduate student and postdoctoral research associate at Cornell University. I would like to thank Shaffique Adam, Umar Syed, Khaled Albanaa, Halit Ozkan and Prof. Toorawah for interesting discussions and friendship over the years.

## TABLE OF CONTENTS

| 1  | Introdu                                            | ction                                                                                                                                                                                              | 1                                |

|----|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|    | 1.1                                                | Background on bio-molecules                                                                                                                                                                        | 3                                |

|    | 1.2                                                | Method of detection                                                                                                                                                                                | 6                                |

|    | 1.3                                                | Integration of micro/nano-fluidic structures with an air-gap FET.                                                                                                                                  | 14                               |

|    | 1.4                                                | MOSFET prototypes using silicon nitride STI process                                                                                                                                                | 15                               |

|    | 1.4.1                                              | Structural problems                                                                                                                                                                                | 16                               |

|    | 1.4.2                                              | Electrical problems                                                                                                                                                                                | 16                               |

|    | 1.5                                                | Side-gated FET                                                                                                                                                                                     | 18                               |

|    | 1.5.1                                              | High performance FETs                                                                                                                                                                              | 19                               |

|    | 1.5.2                                              | Ultra-narrow width planar FETs                                                                                                                                                                     | 20                               |

|    | 1.6                                                | aF resolution C-V characterization of nanoscale FETs                                                                                                                                               | 20                               |

| 2  | Monolit                                            | hic Integration of Micro/nano-fluidic tunnels with FET based                                                                                                                                       |                                  |

| ch | nemical sen                                        | sors                                                                                                                                                                                               | 22                               |

|    |                                                    |                                                                                                                                                                                                    |                                  |

|    | 2.1                                                | Introduction                                                                                                                                                                                       | 22                               |

|    | <ul><li>2.1</li><li>2.2</li></ul>                  | Introduction                                                                                                                                                                                       |                                  |

|    |                                                    |                                                                                                                                                                                                    | 23                               |

|    | 2.2                                                | Fabrication process                                                                                                                                                                                | 23                               |

|    | 2.2.1                                              | Fabrication process                                                                                                                                                                                | 23<br>23                         |

|    | 2.2<br>2.2.1<br>2.2.2                              | Fabrication process  Alignment marks  Active area definition                                                                                                                                       | 23<br>23<br>24                   |

|    | 2.2.1<br>2.2.2<br>2.2.3                            | Fabrication process                                                                                                                                                                                | 23<br>24<br>27                   |

|    | 2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4            | Fabrication process  Alignment marks  Active area definition  Substrate dopant enhancement  Shallow trench isolation                                                                               | 23<br>24<br>27<br>28             |

|    | 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5          | Fabrication process  Alignment marks  Active area definition  Substrate dopant enhancement  Shallow trench isolation  Gate stack deposition and definition                                         | 23<br>24<br>27<br>28<br>31       |

|    | 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6 | Fabrication process  Alignment marks  Active area definition  Substrate dopant enhancement  Shallow trench isolation  Gate stack deposition and definition  Self-aligned source/drain implantation | 23<br>24<br>27<br>28<br>31<br>32 |

|    | 2.2.9.     | 1 Sacrificial oxide definition                                | 34     |

|----|------------|---------------------------------------------------------------|--------|

|    | 2.2.9.     | 2 Irrigation holes and vias for metal contacts                | 36     |

|    | 2.2.9.     | 3 Removal of sacrificial oxide                                | 37     |

|    | 2.2.10     | Gate oxide regrowth                                           | 38     |

|    | 2.2.11     | Metallization                                                 | 38     |

|    | 2.2.12     | Substrate contact                                             | 40     |

|    | 2.3        | Testing                                                       | 40     |

|    | 2.3.1      | Structural testing                                            | 40     |

|    | 2.3.2      | Electrical testing                                            | 42     |

|    | 2.4        | Sensitivity                                                   | 45     |

|    | 2.5        | Conclusion                                                    | 48     |

| 3  | Back-en    | nd-of-line Integration of Micrometer Scale Silicon Dioxide To | unnels |

| f( | or On-chip | Fluidic Sample Delivery to Nanometer-scale Chemical Senso     | ors51  |

|    | 3.1        | Overview                                                      | 51     |

|    | 3.2        | Fabrication process                                           | 53     |

|    | 3.3        | Conclusion                                                    | 58     |

| 4  | Side-gat   | ted MOSFET                                                    | 60     |

|    | 4.1        | Power concerns in VLSI devices                                | 61     |

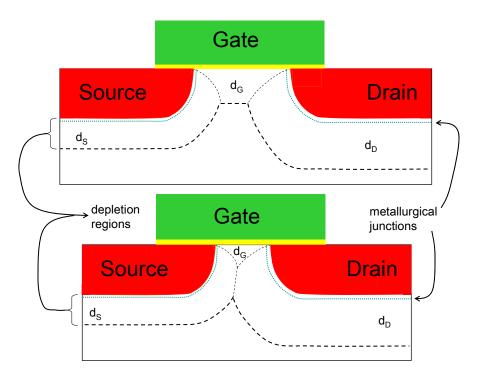

|    | 4.2        | Device design                                                 | 62     |

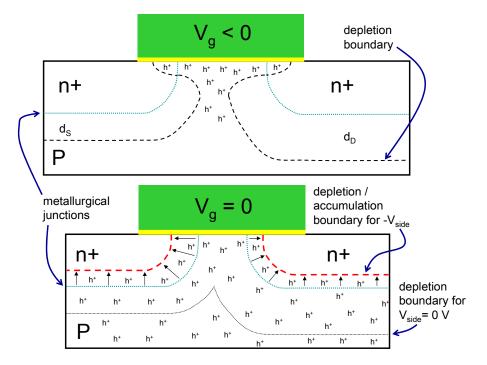

|    | 4.2.1      | Side-gate control over body potential in planar geometry      | 64     |

|    | 4.2.2      | Side-gate control over body potential in tri-gate geometry    | 68     |

|    | 4.3        | Fabrication                                                   | 71     |

|    | 4.3.1      | Side-gate deposition and patterning                           | 71     |

|    | 4.3.2      | Shallow Trench Isolation                                      | 72     |

|    | 4.3.3      | Gate stack                                                    | 73     |

|    | 4.3.4      | Self-aligned source/drain formation                           | 74     |

| 4.3.5       | Passivation & vias                                      | 75          |

|-------------|---------------------------------------------------------|-------------|

| 4.3.6       | Metallization & anneal                                  | 75          |

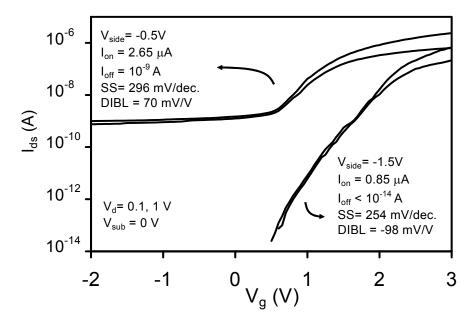

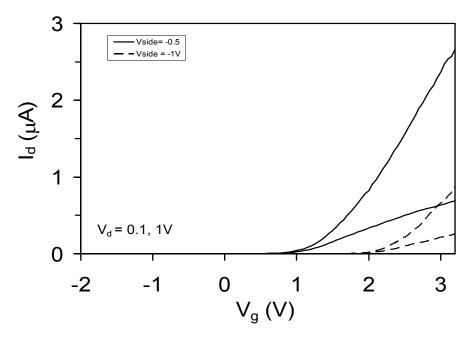

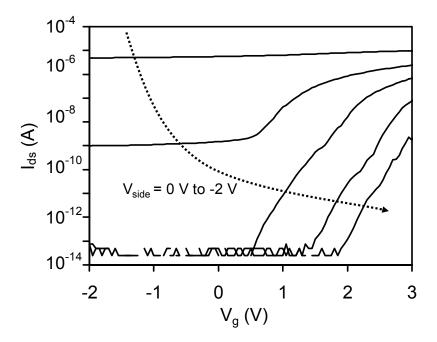

| 4.4         | Electrical Characteristics                              | 75          |

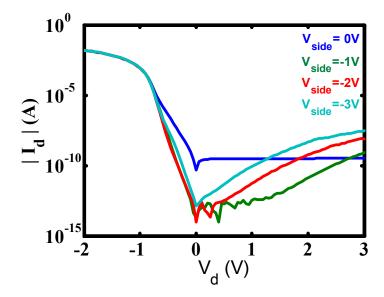

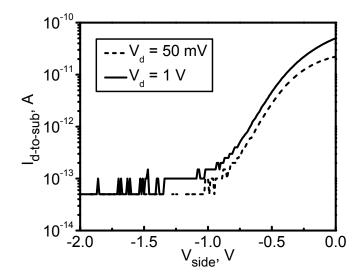

| 4.4.1       | Drain-to substrate diode                                | 76          |

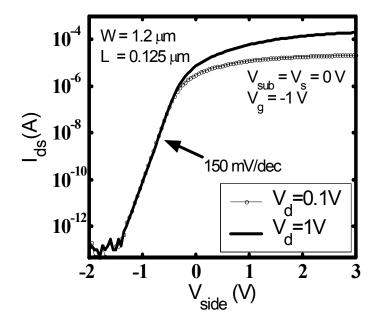

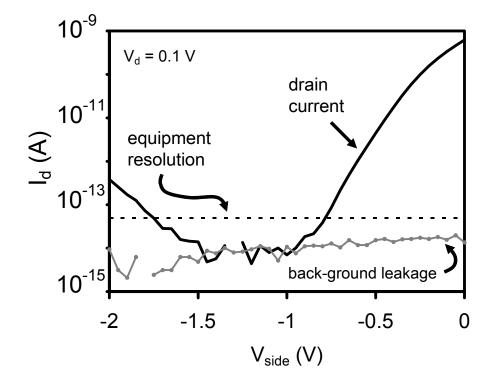

| 4.4.2       | Drain to source leakage                                 | 79          |

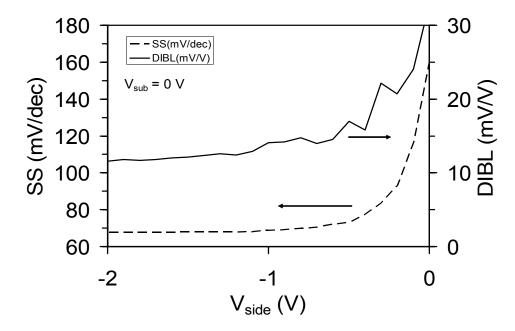

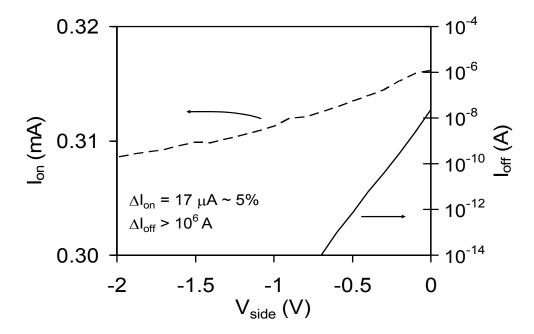

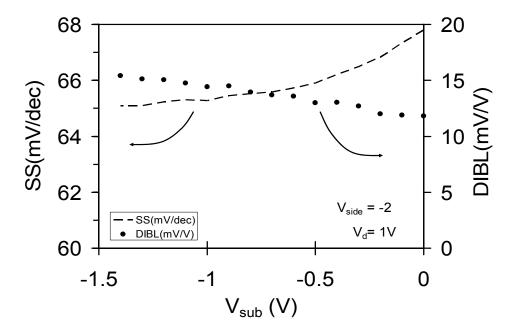

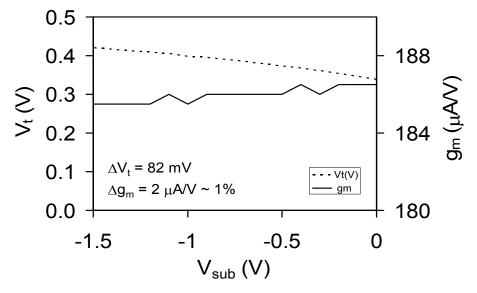

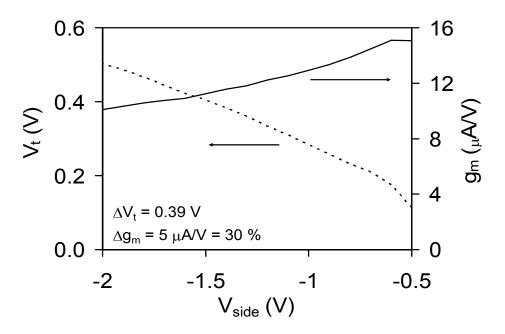

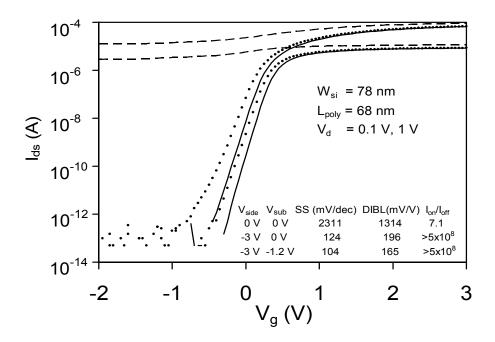

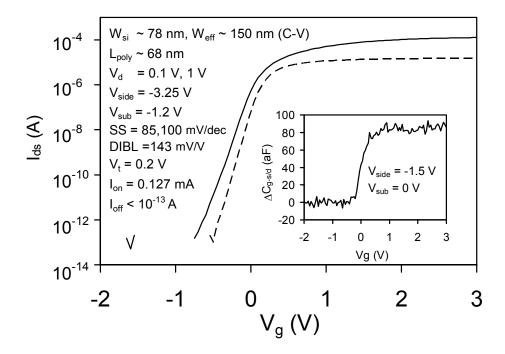

| 4.4.3       | Side-gated tri-gate MOSFET                              | 80          |

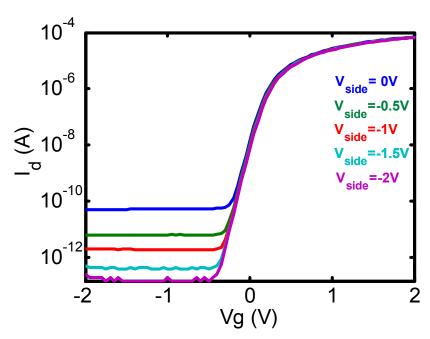

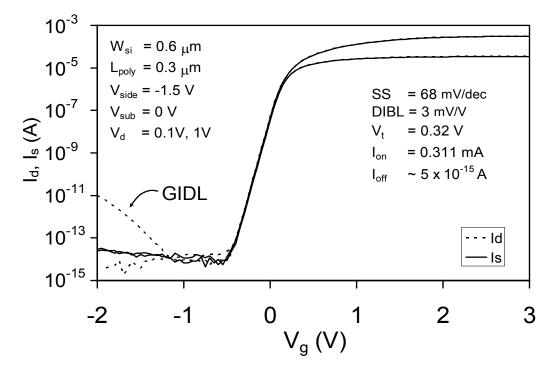

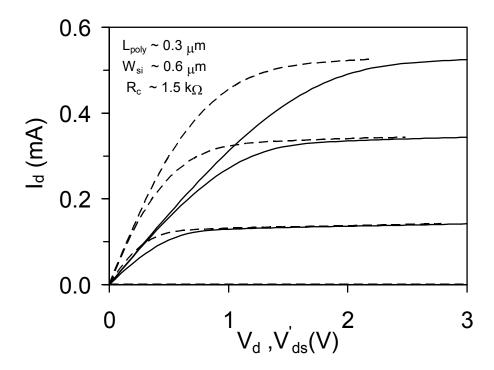

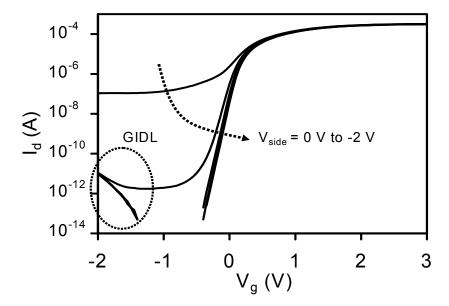

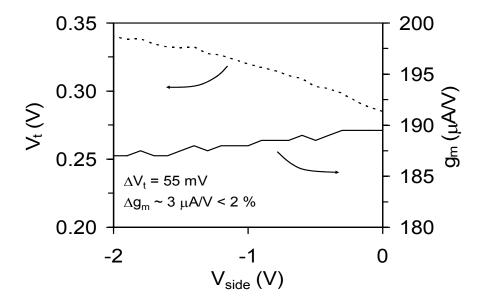

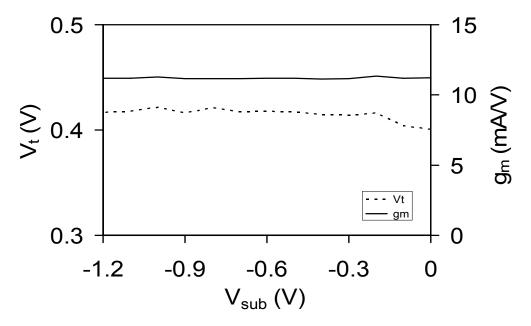

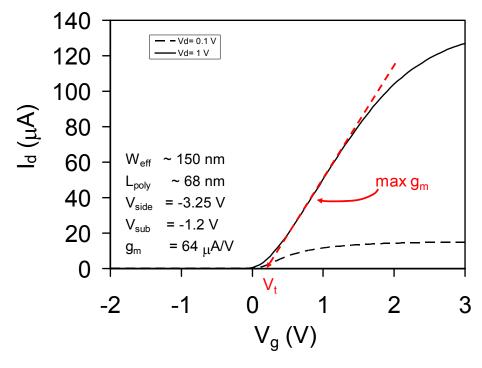

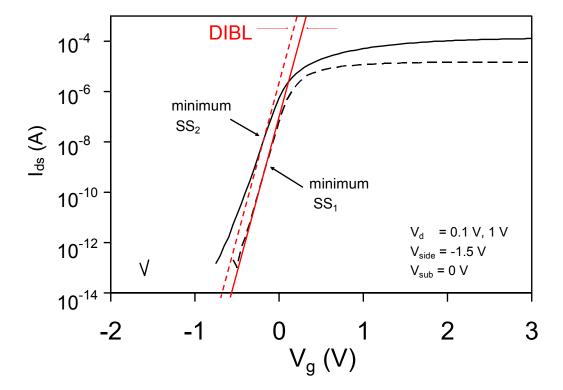

| 4.4.4       | Side-gated wide MOSFET                                  | 81          |

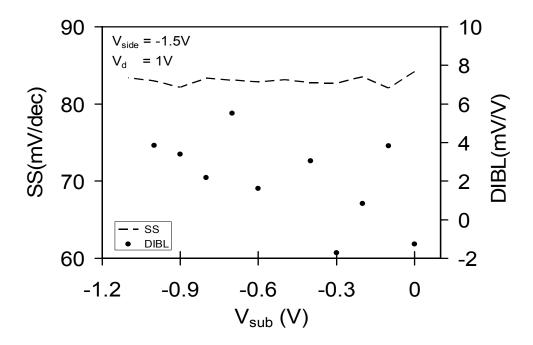

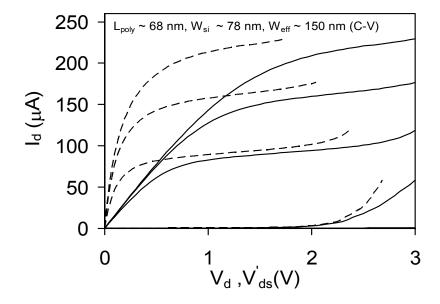

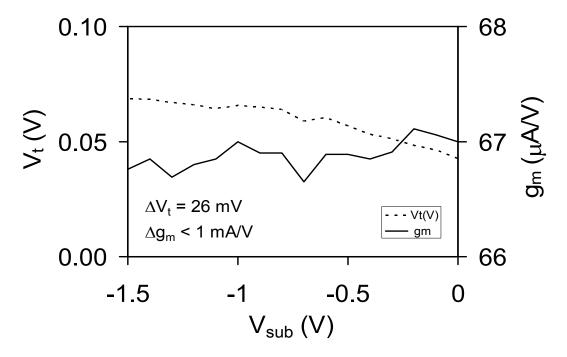

| 4.4.5       | Side-gated narrow channel MOSFET                        | 87          |

| 4.4.6       | Side-gated short-channel MOSFET                         | 96          |

| 4.4.7       | Ultra-narrow width side-gated MOSFET                    | 108         |

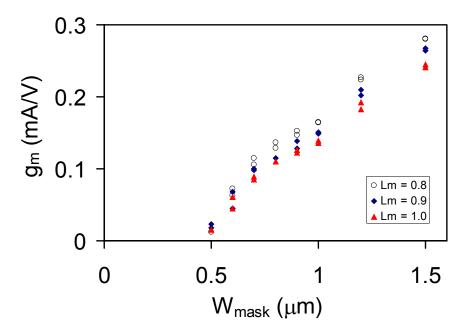

| 4.5         | Mobility                                                | 119         |

| 4.6         | Capacitance penalty                                     | 121         |

| 4.7         | Channel optimization for sensor application             | 123         |

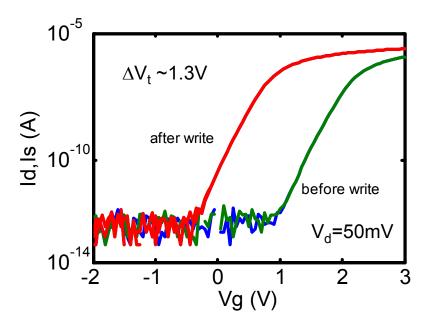

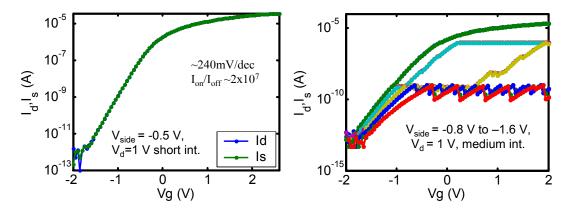

| 4.8         | Side-trapping non-volatile memory                       | 125         |

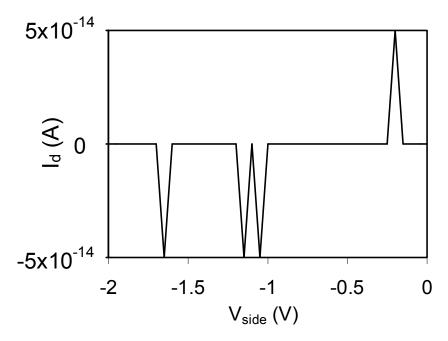

| 4.9         | An instrumentation anomaly                              | 127         |

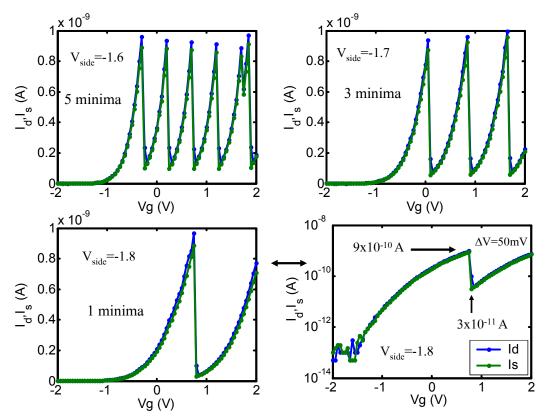

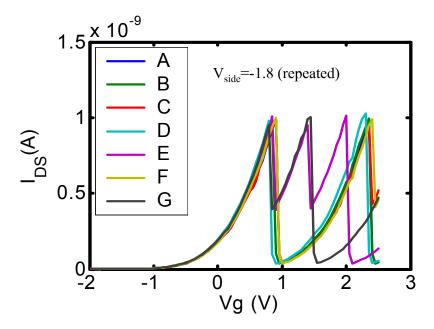

| 4.10        | Transconductance oscillations                           | 132         |

| 4.11        | Low-power resonant gate AC Write/Erase DC read nor      | n-volatile  |

| memory f    | For RF-ID applications and RF imaging schemes           | 136         |

| 4.11.1      | Non-volatile memory                                     | 136         |

| 4.11.2      | Microwave imaging                                       | 140         |

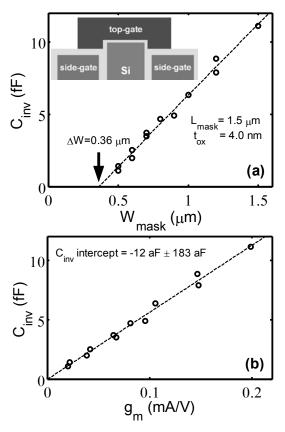

| 5 aF Res    | olution Split C-V Characterization of Nanoscale FETs us | sing Random |

| Fluctuation | s                                                       | 141         |

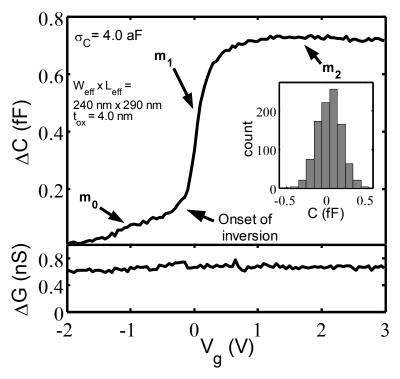

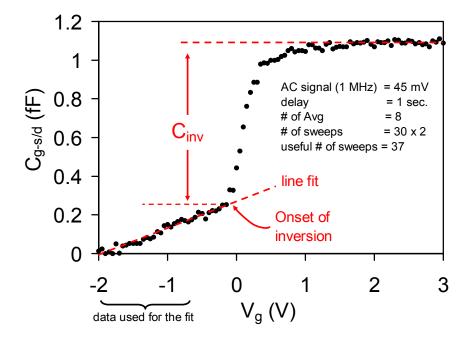

| 5.1         | Introduction                                            | 141         |

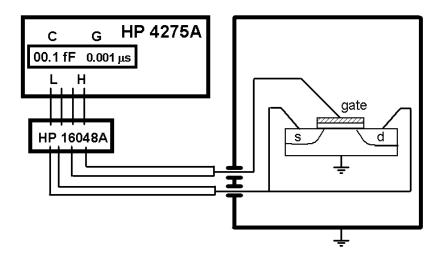

| 5.2         | Experimental details                                    | 142         |

| 5.3         | Analysis                                                | 145         |

|   | 5.4          | Application of this technique for fA resolution current measurements |

|---|--------------|----------------------------------------------------------------------|

|   |              |                                                                      |

|   | 5.5          | Conclusion                                                           |

|   | 5.6          | Acknowledgment149                                                    |

| 6 | Conclusi     | ions                                                                 |

| 7 | Appendi      | x154                                                                 |

|   | 7.1          | Details of fabrication process                                       |

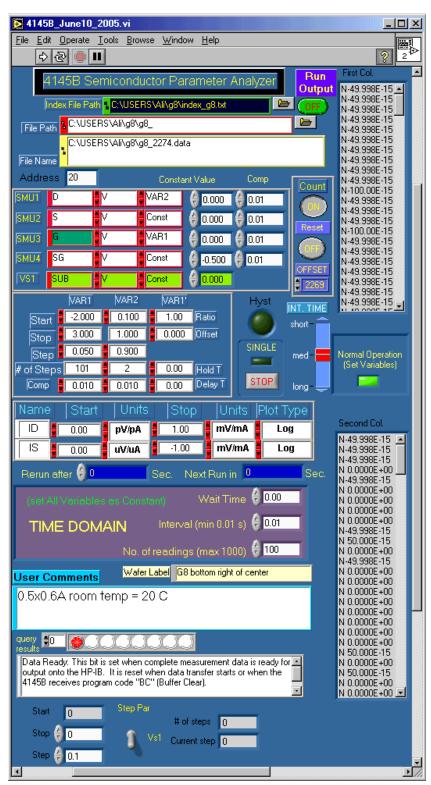

|   | 7.2          | Software tools developed for instrument control for electrical       |

|   | characteriza | ntion                                                                |

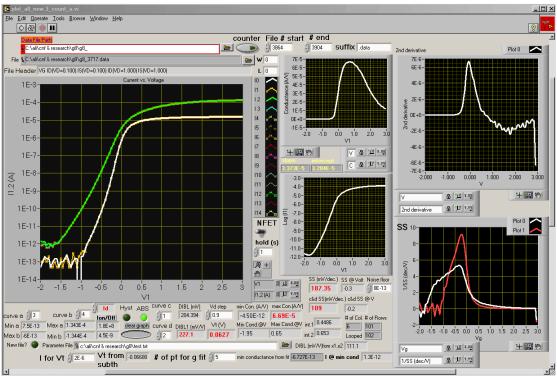

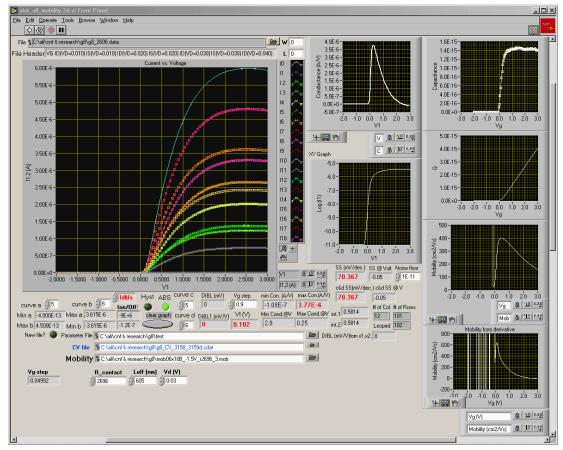

|   | 7.2.1        | Parameter Analyzer                                                   |

|   | 7.2.2        | Software tool developed for analysis and algorithms used for MOSFET  |

|   | paramete     | r extraction166                                                      |

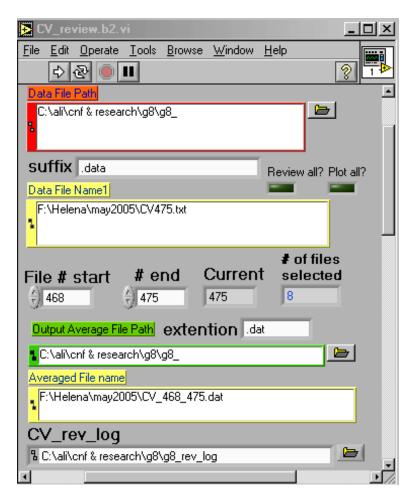

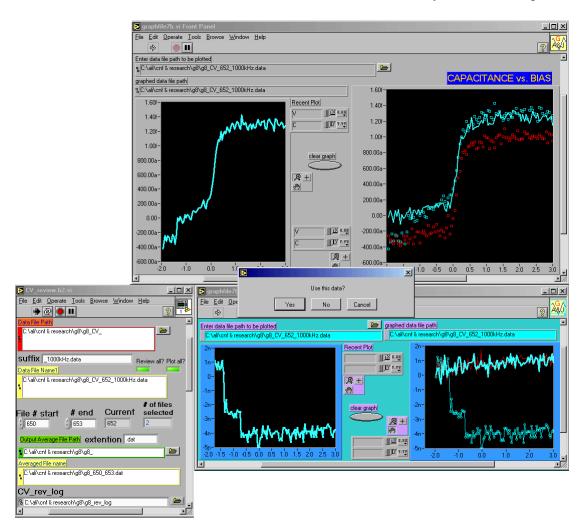

|   | 7.2.2.1      | Data File Selection                                                  |

|   | 7.2.2.2      | Data Selection167                                                    |

|   | 7.2.2.3      | Calculated Parameters                                                |

|   | 7.2.2.4      | Extremum                                                             |

|   | 7.2.2.5      | Conductance                                                          |

|   | 7.2.2.6      | Threshold Voltage169                                                 |

|   | 7.2.2.7      | Subthreshold Slope170                                                |

|   | 7.2.2.8      | Drain Induced Barrier Lowering                                       |

|   | 7.2.2.9      | Parameter File172                                                    |

|   | 7.2.2.1      | 0 NFET / PFET Switch                                                 |

|   | 7.2.2.1      | 1 Slope & Intercept                                                  |

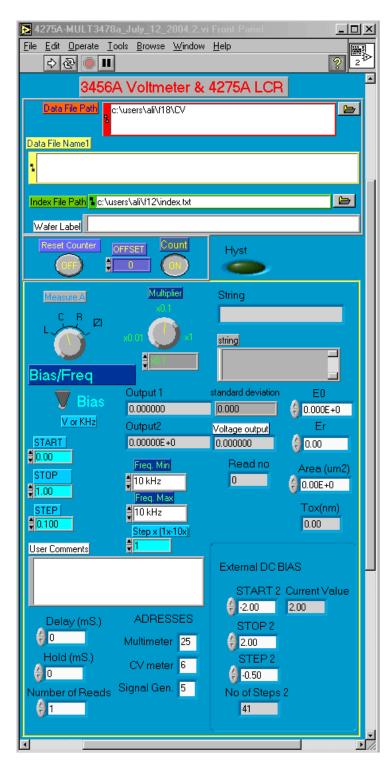

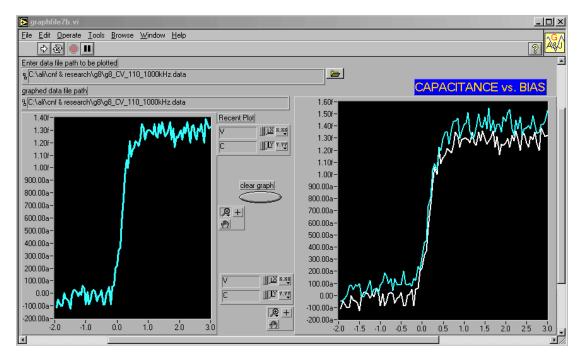

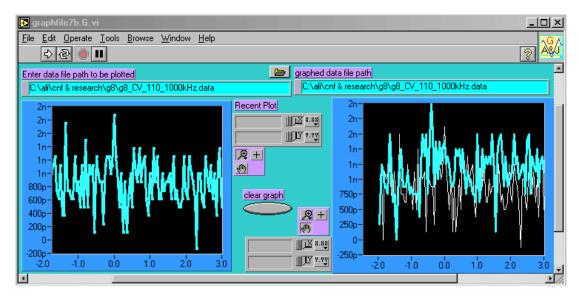

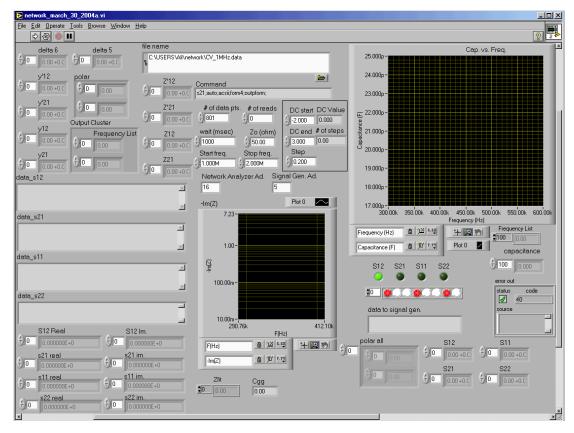

|   | 7.2.3        | Software tool developed for C-V measurements through LCR meter 173   |

|   | 7.2.4        | Plotting                                                             |

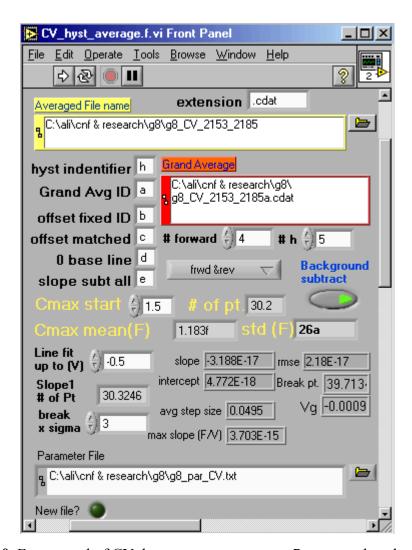

|   | 7.2.5        | C-V Analysis                                                         |

|   |              |                                                                      |

| 8 | Referen | ces                                                            | 196    |

|---|---------|----------------------------------------------------------------|--------|

|   | 7.6.1   | Software Tool for Carrier Mobility Extraction                  | 194    |

|   | 7.6     | Carrier Mobility Extraction                                    | 192    |

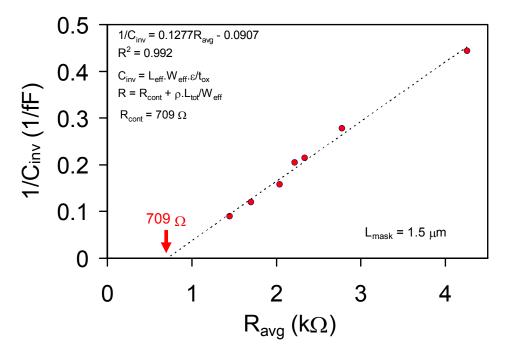

|   | 7.5     | Contact resistance extraction from electrical measurements     | 189    |

|   |         |                                                                | 187    |

|   | 7.4     | Effective device dimension extraction from electrical measures | ments. |

|   | 7.3     | C-V extraction through RF measurements                         | 185    |

|   | 7.2.5.3 | 3 CV hysteresis average                                        | 181    |

|   | 7.2.5.2 | 2 Data file selection criteria                                 | 180    |

|   | 7.2.5.  | 1 CV Review                                                    | 179    |

# LIST OF FIGURES

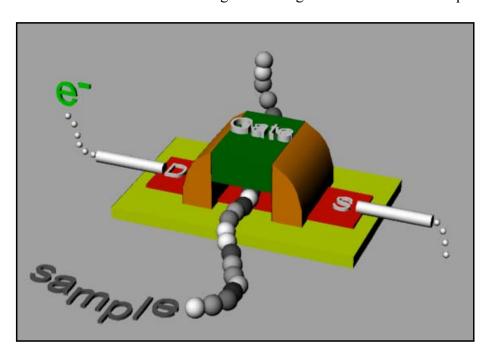

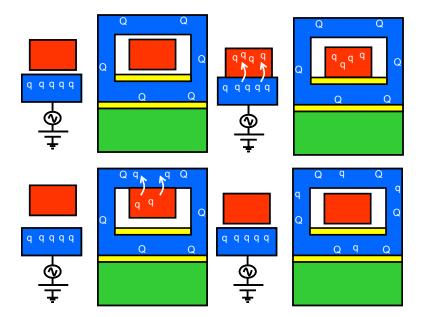

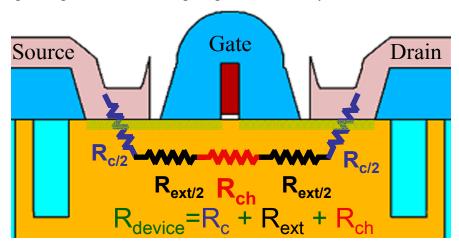

| Figure 1.1 3D schematics of the device structure. The source-drain current is           |

|-----------------------------------------------------------------------------------------|

| monitored as the sample is passed perpendicular to the channel of the transistor.       |

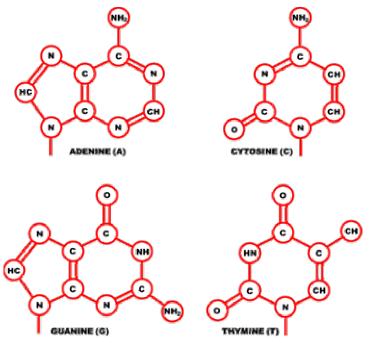

| Figure 1.2 Molecular structure of the four nucleotides found in DNA molecules. The      |

| unsatisfied bon on N binds to the sugar-phosphate backbone to form a strand             |

| Figure 1.3 Schematics of double stranded DNA structure. The DNA strands are             |

| bonded together through hydrogen bonds between the complimentary pairs [15].5           |

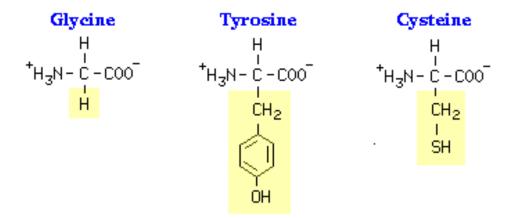

| Figure 1.4 Three examples of naturally occurring amino acids. Amino or the acid         |

| group can get activated at certain pH values [18].                                      |

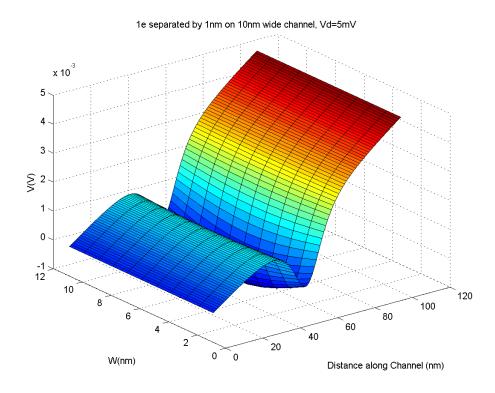

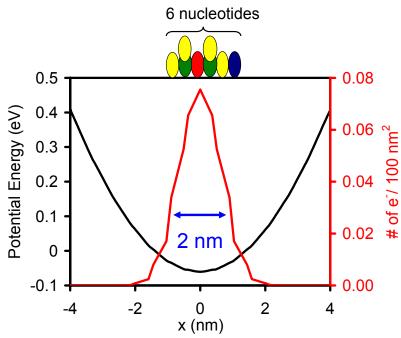

| Figure 1.5 Potential perturbation caused by a dipole over the channel of a 10 nm wide   |

| FET in the subthreshold regime.                                                         |

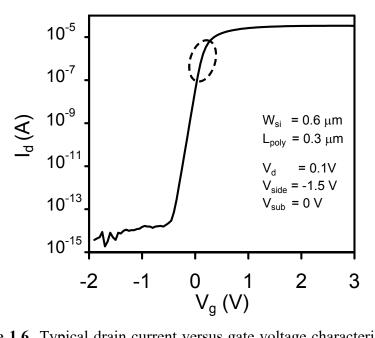

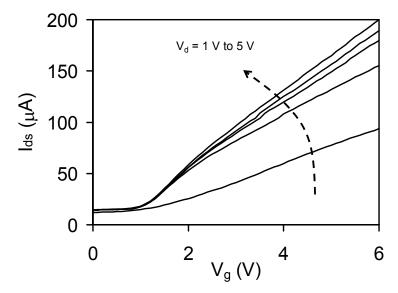

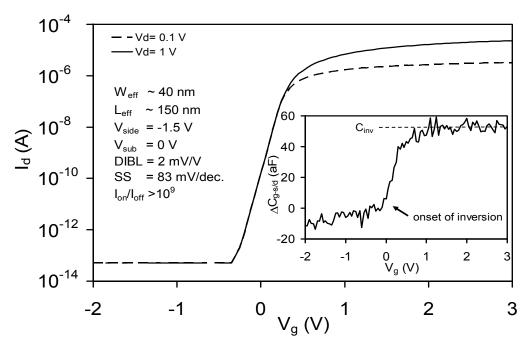

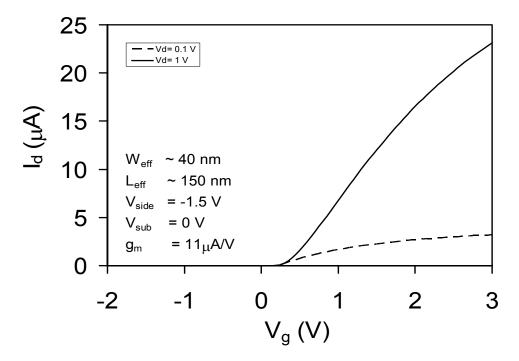

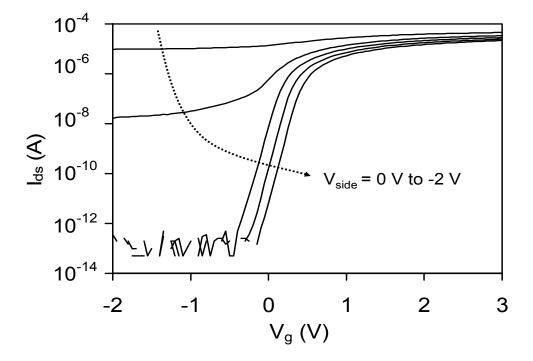

| Figure 1.6 Typical drain current versus gate voltage characteristics of a field effect  |

| transistor. The optimum sensitivity is expected to be achieved slightly below           |

| onset of inversion (circled regime)                                                     |

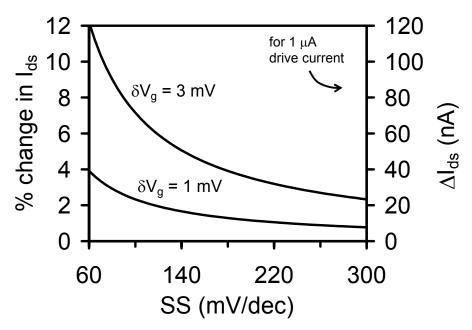

| Figure 1.7 Sensitivity of the FET as a function of the subthreshold slope. Left axis    |

| shows the percentage change in drain to source current and right axis is showing        |

| the magnitude of the change for bias condition resulting in 1 $\mu A$ of drive current. |

| 9                                                                                       |

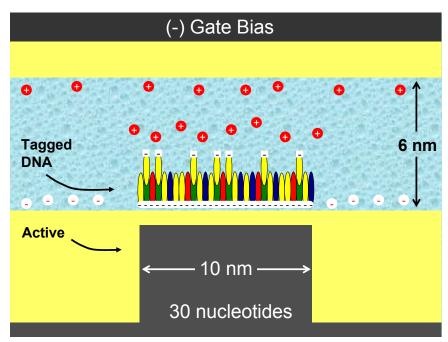

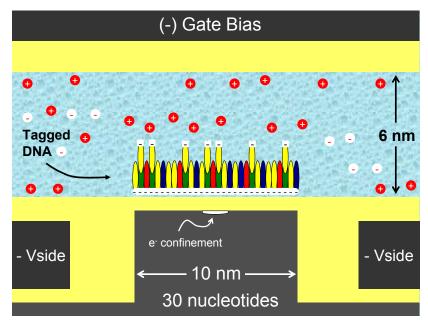

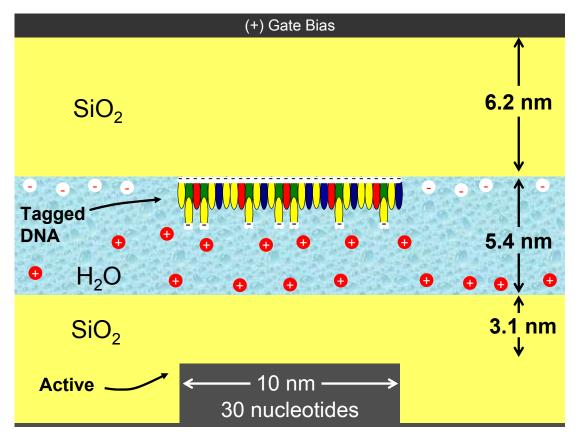

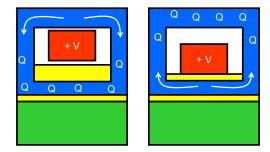

| Figure 1.8 Cross-section schematics of an FET sensor with 10 nm wide electrical         |

| channel and 6 nm high nanofluidic tunnel passing under the gate. Orientation of         |

| DNA molecule and ion distribution is shown for the case of a negative gate              |

| potential11                                                                             |

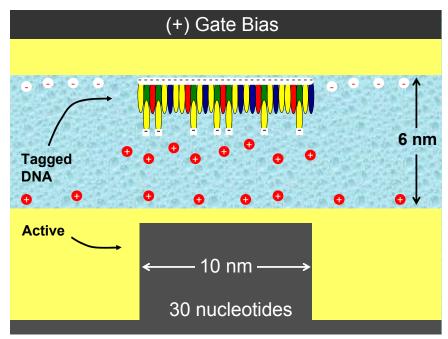

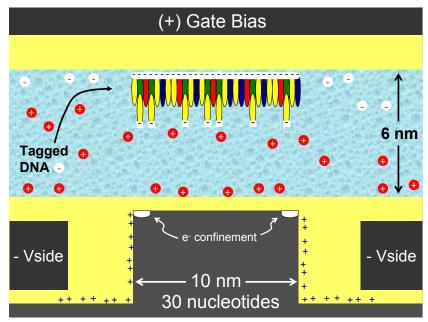

| Figure 1.9 Cross-section schematics of an FET sensor with 10 nm wide electrical         |

| channel and 6 nm high nanofluidic tunnel passing under the gate. Orientation of         |

| DNA molecule and ion distribution is shown for the case of a positive gate               | 1 1 |

|------------------------------------------------------------------------------------------|-----|

| potential.                                                                               |     |

| Figure 1.10 Electron confinement to the central region in a 8 nm wide channel with       | 1   |

| parabolic potential profile simulated by using classical electrostatics. It is           |     |

| possible to confine electrons into a 2 nm wide nanowire for low electron                 |     |

| concentrations                                                                           | 12  |

| Figure 1.11 Cross-section schematics of the sensor structure with electrons confined     |     |

| to the central portion of the channel with the aid of additional side-gates. The         |     |

| confinement can be achieved by either applying a negative or positive bias on the        | ıe  |

| top-gate depending on the side-gate bias conditions and the body doping level.           | 13  |

| Figure 1.12 Cross-section schematics of the sensor structure with electrons confined     |     |

| to the two edges of the active area with the aid of interface fixed charges and          |     |

| additional side-gates. Current confinement to the top surface at the edges can           |     |

| only be achieved by application of positive top-gate bias                                | 13  |

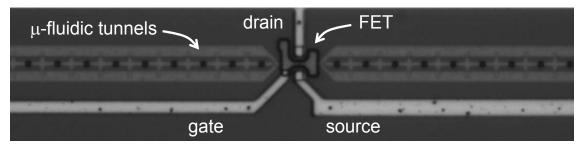

| Figure 1.13 Air-gap FET monolithically integrated with microfluidic sample deliver       | y   |

| tunnels using silicon nitride isolation process.                                         | 15  |

| Figure 1.14 Drain current versus gate voltage characteristics of a field effect transist | or  |

| build using low stress silicon nitride as STI material, with 10 nm deposited oxid        | e.  |

|                                                                                          | 16  |

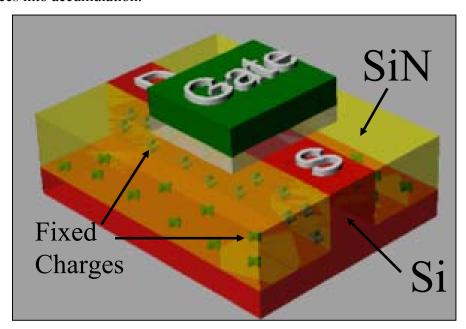

| Figure 1.15 3D schematics of an FET using silicon nitride as field isolation. There is   | a   |

| high density of fixed charges and defects at the interfaces.                             | 17  |

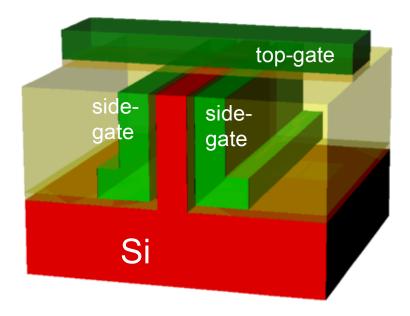

| Figure 1.16 3D schematics of side-gated FET utilizing silicon nitride field isolation    | ,   |

| The two side-gates are connected together and the top gate is operated                   |     |

| independently.                                                                           | 19  |

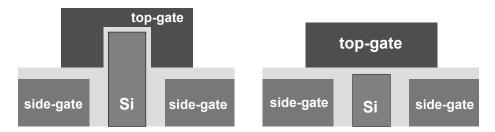

| Figure 1.17 Cross section schematics of devices with recessed side-gates (left) and      |     |

| nlanar ton-gate geometry                                                                 | 20  |

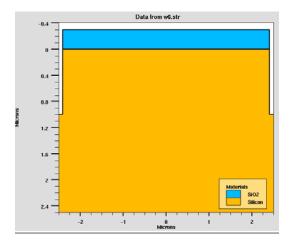

| Figure 2.1 Cross section view after the alignment mark RIE                                                |

|-----------------------------------------------------------------------------------------------------------|

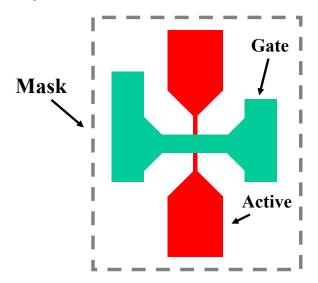

| Figure 2.2 Schematics of mask layout showing the active, gate and mask layers 24                          |

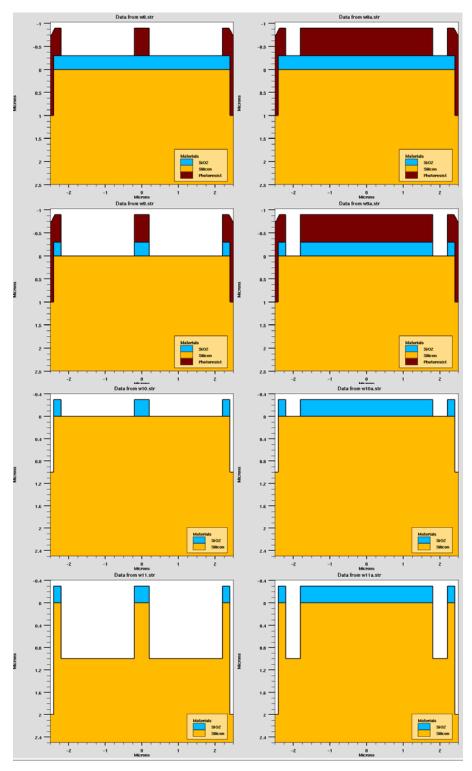

| Figure 2.3 Cross section view along the width (left) and length of the device (right)                     |

| after resist spin, lithography, mask oxide etch in RIE and active area RIE25                              |

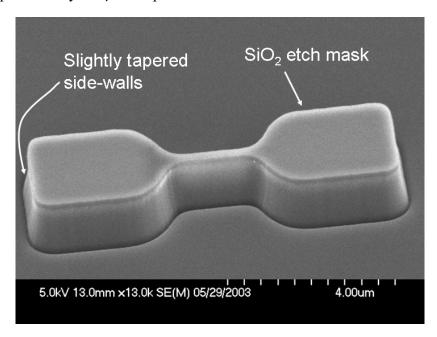

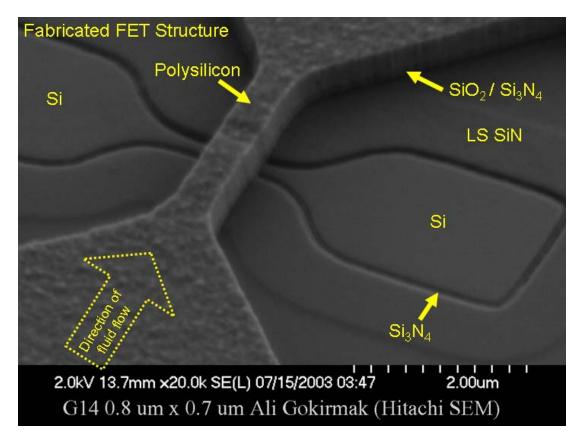

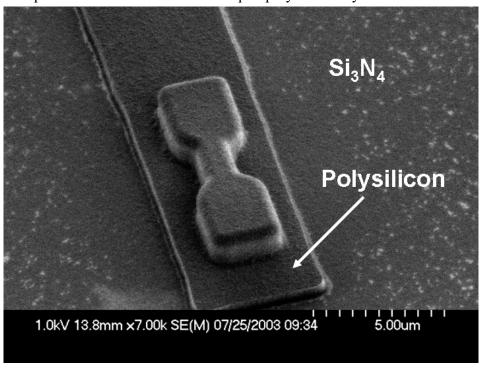

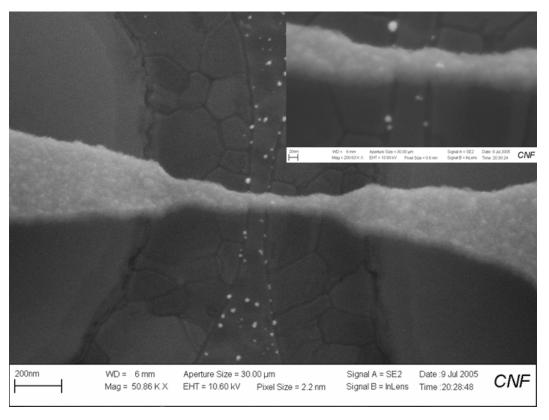

| Figure 2.4 SEM micrograph of the active area, imaged at 45° tilt. The ripple visible                      |

| on the sidewalls are significantly reduced as the device is sized down through                            |

| oxidation during the process sequence for dopant enhancement and width sizing.                            |

|                                                                                                           |

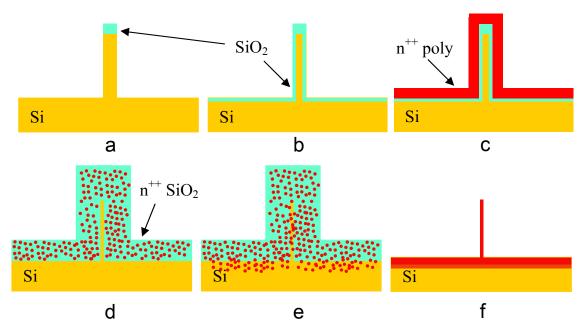

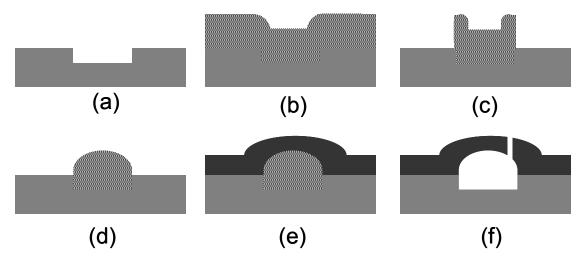

| Figure 2.5 Cross sectional schematics showing the processes to enhance the body                           |

| doping and sizing down the device width. Active area RIE (a), thermal oxide                               |

| growth (b), doped polysilicon deposition (c), oxidation of doped polysilicon and                          |

| active Si (d), dopant diffusion (e) and removal of oxide resulting in doped                               |

| interfaces with reduced channel width (f)                                                                 |

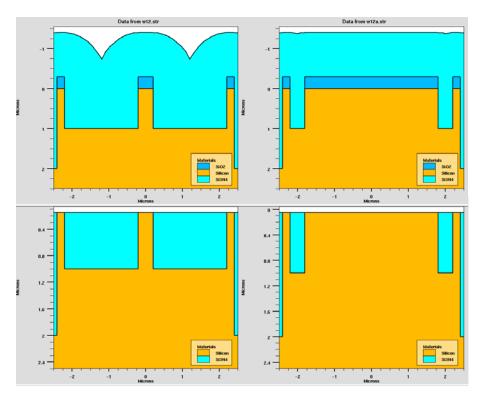

| Figure 2.6 Cross sectional schematics after silicon nitride deposition (top) and                          |

| planarization (bottom)                                                                                    |

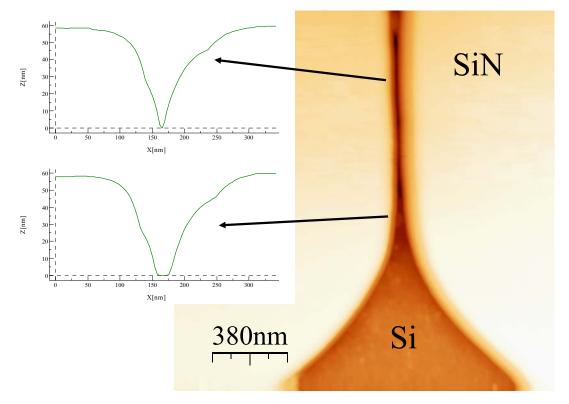

| Figure 2.7 AFM image of an ultra-narrow channel transistor (right) and two cross                          |

| sections (left). The silicon surfaces are recessed below the nitride field by                             |

| approximately 60 nm. The measurable width in the narrow region is limited by                              |

| the AFM tip (~10 nm) [35]29                                                                               |

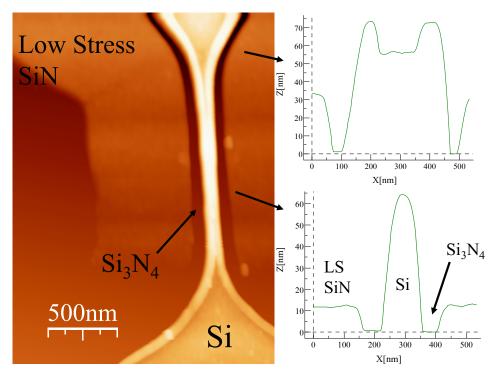

| Figure 2.8 AFM image of an over-polished active area. The edges of the Si active                          |

| form rims around the recessed planar areas. The surface is imaged after recessing                         |

| the field nitride through 21 min. of HF etch. Si <sub>3</sub> N <sub>4</sub> areas are recessed more than |

| the silicon rich silicon nitride field [35]                                                               |

| Figure 2.9 SEM image of the FET structure after gate stack definition and etch 31                         |

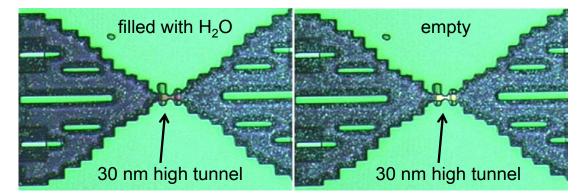

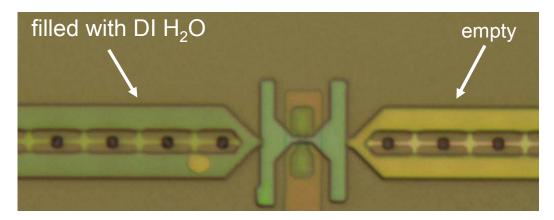

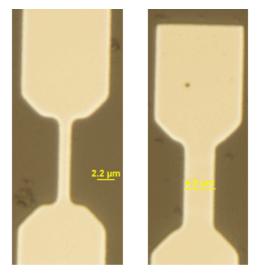

| Figure 2.10 Optical microscope images of shallow test tunnels made out of silicon      |

|----------------------------------------------------------------------------------------|

| nitride with (left) and without (right) water. Shallow tunnel height is                |

| approximately 30 nm and are attached to larger delivery tunnels34                      |

| Figure 2.11 SEM image of a patterned sacrificial oxide leading to an FET structure.    |

| The oxide layer for delivery tunnels is higher than the shallow tunnels which will     |

| be used for irrigation                                                                 |

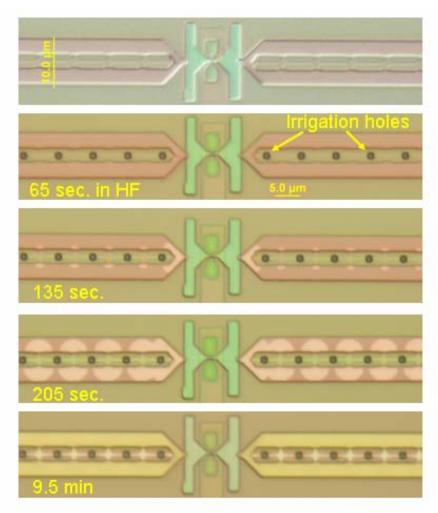

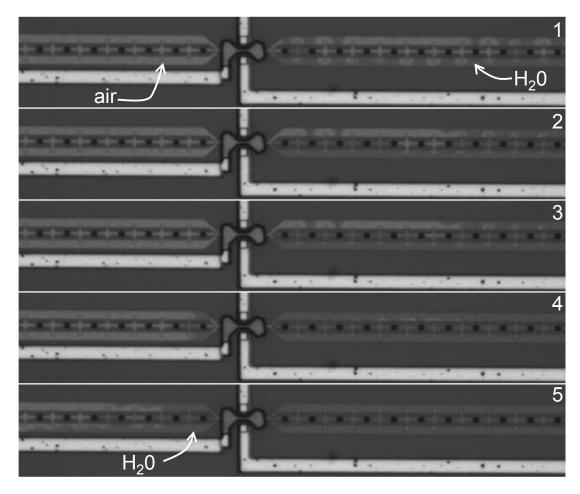

| Figure 2.12 Optical images depicting the sequence of sacrificial oxide removal from    |

| the sample delivery tunnels                                                            |

| Figure 2.13 Schematics of metal lift-off process using a bi-layer resist process38     |

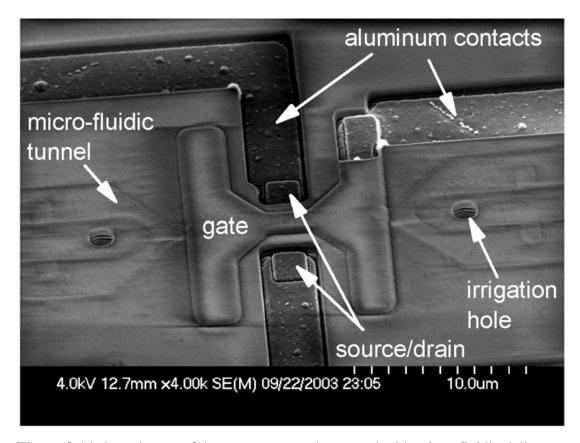

| Figure 2.14 SEM image of the FET structure integrated with micro-fluidic delivery      |

| tunnels after metallization                                                            |

| Figure 2.15 Optical image of a device structure with microfluidic delivery system.     |

| The DI water is applied onto the tunnels a few mm left of the device41                 |

| Figure 2.16 Optical snap-shots of a device structure with microfluidic delivery system |

| after application of a droplet of DI water on the tunnel system a few mm away          |

| from the device on the right side41                                                    |

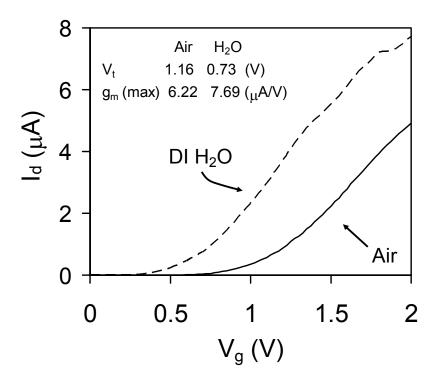

| Figure 2.17 Transfer characteristics with Air and DI water in linear scale42           |

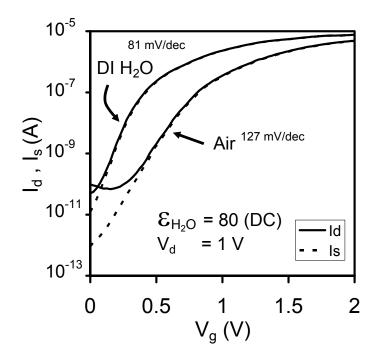

| Figure 2.18 Transfer characteristics of a narrow channel FET with air gap and with     |

| DI water filled into the tunnel between the gate and the channel. DI water is          |

| applied on the delivery tunnel system and the capillary forces drive DI water into     |

| the FET resulting in significant change in the device characteristics                  |

| Figure 2.19 Schematics of the device structure and DNA molecule drawn to scale for     |

| the estimated device dimensions                                                        |

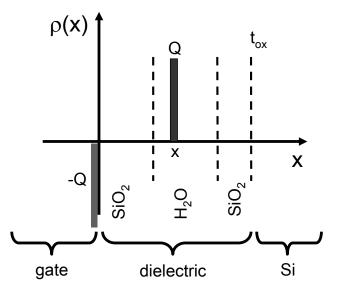

| Figure 2.20 Schematics of charge distribution in an FET gate stack. Q is the           |

| additional fixed charge density due to the molecules in the solution47                 |

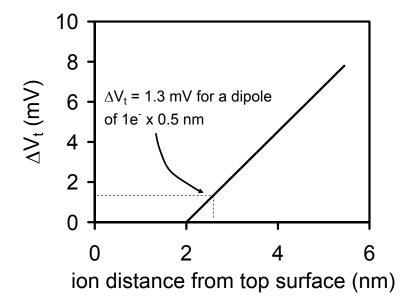

| Figure 2.21 Expected change in the threshold voltage as a function of distance of the       |

|---------------------------------------------------------------------------------------------|

| shielding ionic charge in the solution1e <sup>-</sup> ionic charge is taken to be screening |

| +1e <sup>-</sup> charge on the tag                                                          |

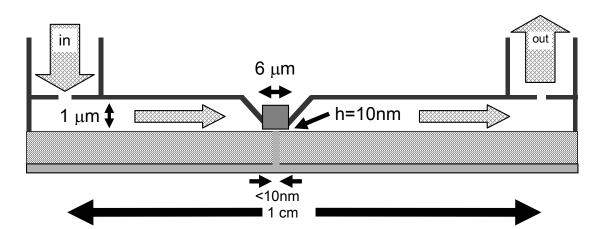

| Figure 3.1. Fluid delivery into nano-fluidic chemical sensors from off chip reservoir.      |

| Sensors < 10 nm in width can be fabricated with a suspended gate51                          |

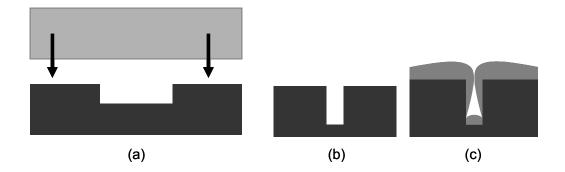

| Figure 3.2. (a) Wafer bonding and (b-c) deposition over trenches                            |

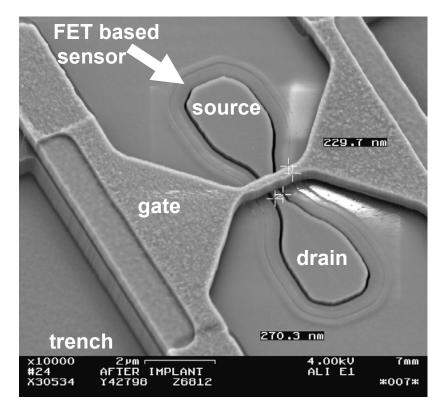

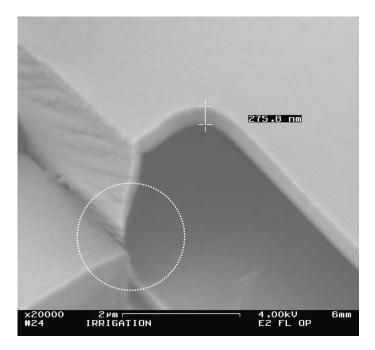

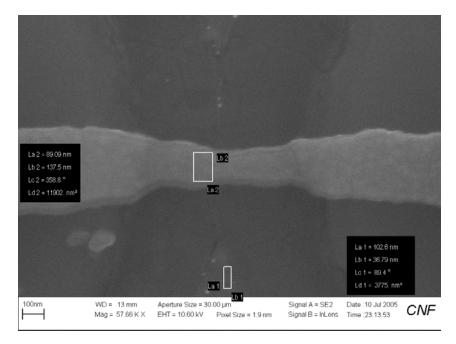

| Figure 3.3. Scanning electron micrograph (SEM) of a FET based chemical sensor               |

| after trench formation                                                                      |

| Figure 3.4. Tunnel fabrication process using sacrificial resist: (a) Etch trenches using    |

| RIE, (b) spin resist, (c) pattern resist, (d) smooth resist profile, (e) deposit cap        |

| oxide, (f) open irrigation holes & dissolve resist                                          |

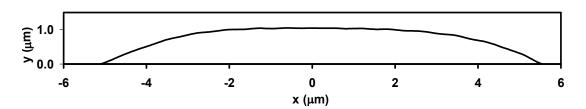

| Figure 3.5. Sacrificial resist profile after heated oxygen plasma treatment and oven        |

| bake                                                                                        |

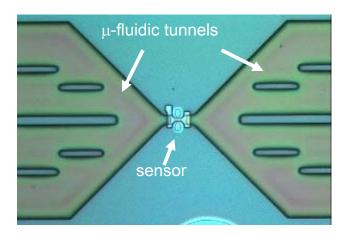

| Figure 3.6. Optical image of the sensor and the microfluidic tunnels for sample             |

| delivery after oxide sputter deposition                                                     |

| Figure 3.7 RF sputter deposited oxide tunnel structures. The sputtered oxide is             |

| significantly thinner at the bottom portion of the side-walls                               |

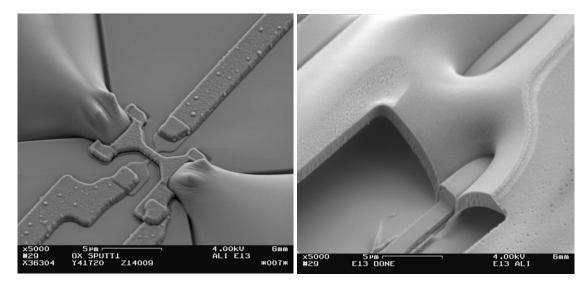

| Figure 3.8. SEM image of resist filled tunnels after oxide RF sputter deposition (left)     |

| and sidewalls of the oxide structure after PECVD oxide deposition and resist                |

| removal (right)                                                                             |

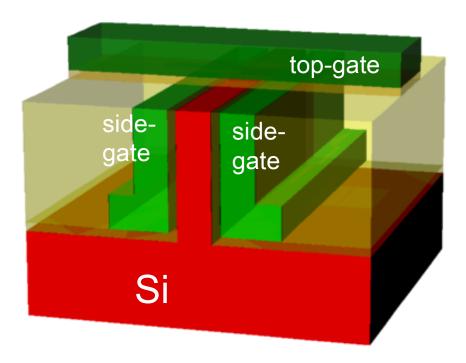

| Figure 4.1 3D schematics of side-gated FET utilizing silicon nitride field isolation.       |

| The two side-gates are connected together and the top gate is operated                      |

| independently60                                                                             |

|                                                                                             |

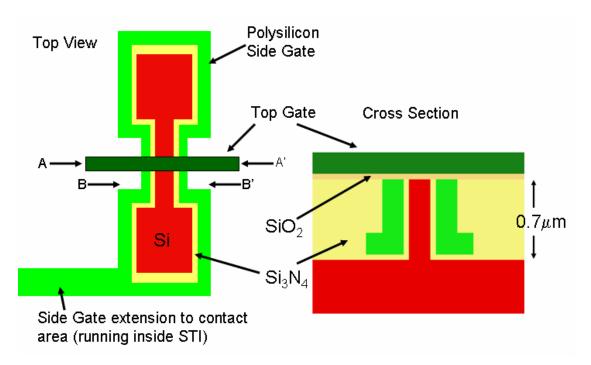

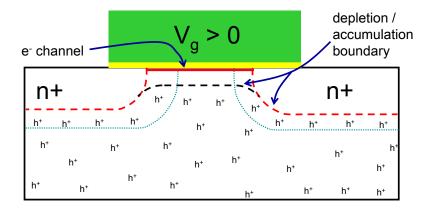

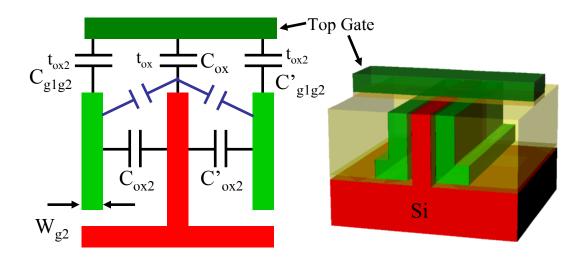

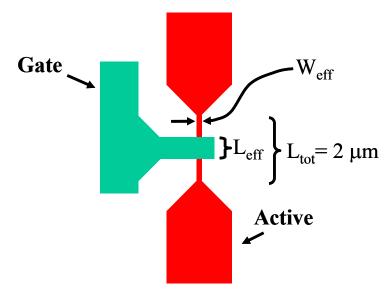

| Figure 4.2 Top (left) and cross sectional schematics of the side-gated FET63                |

| Figure 4.2 Top (left) and cross sectional schematics of the side-gated FET                  |

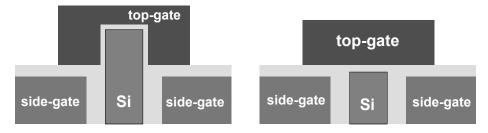

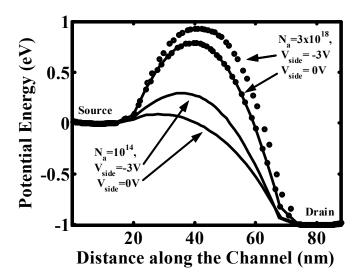

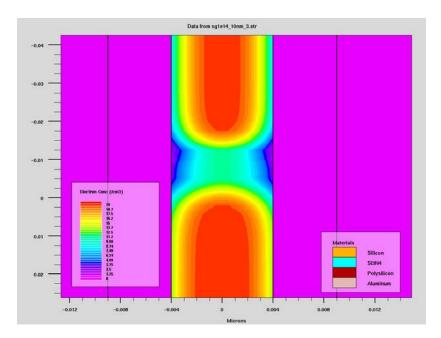

| Figure 4.4 Simulated potential barrier for a W x $L = 50$ nm x 40 nm device with side-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gate for intrinsic channel and $N_{sub} = 3x10^{18}$ cm <sup>-3</sup> at the device center. $t_{side} = 15$ nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| (Si <sub>3</sub> N <sub>4</sub> ), $Q_{interface} = 3x10^{10} cm^{-2}$ 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

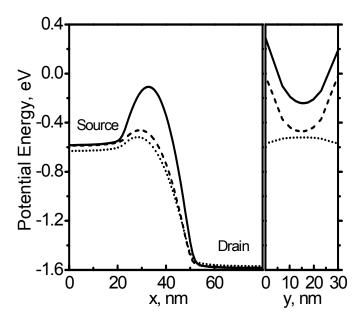

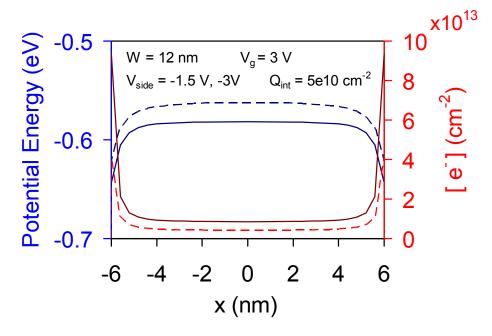

| Figure 4.5 Simulated potential profiles for a 30 nm x 30 nm side-gated device, $t_{side} =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 19 nm (Si <sub>3</sub> N <sub>4</sub> ) along the channel (left) and across the channel (right) for $N_{sub}$ =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $3x10^{18}$ cm <sup>-3</sup> (solid), $N_{sub} = 1x10^{14}$ cm <sup>-3</sup> (dashes) and a conventional bulk device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| with $N_{\text{sub}} = 3x10^{18} \text{ cm}^{-3}$ (dots). Interface charge density $Q_{\text{int}} = 3x10^{10} \text{ cm}^{-2}$ 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 4.6 2D simulated electron concentration profile of a W x L = $8 \text{ nm x } 10 \text{ nm}$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $t_{\rm side}$ = 5nm (Si <sub>3</sub> N <sub>4</sub> ), intrinsic channel device. The electrons are confined to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| approximately 5 nm in the central section of the channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

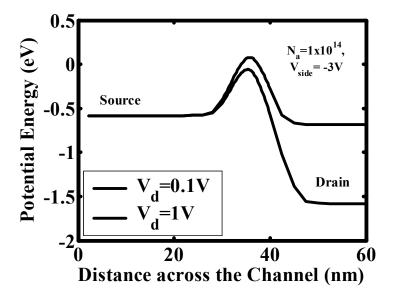

| Figure 4.7 Simulated potential barrier for a W x L= $8$ nm x $10$ nm, $t_{side} = 5$ nm (Si <sub>3</sub> N <sub>4</sub> ),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| intrinsic channel device with side-gate for two drain biases, $V_{\text{side}} = -3 \text{ V}$ . A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| potential barrier higher than 0.5 eV is observed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

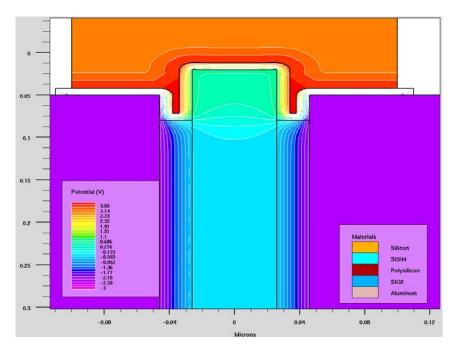

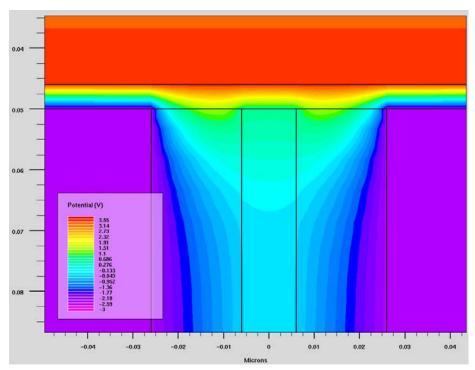

| Figure 4.8 Simulated potential profile of a 50 nm wide tri-gate structure with 50 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| side recess. $V_{\text{side}} = -3 \text{ V}, V_g = 3.5 \text{ V}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

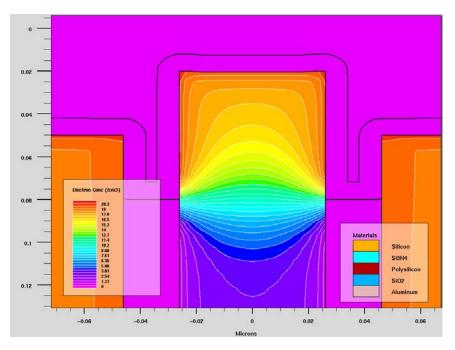

| Figure 4.9 Simulated electron concentration profile of a 50 nm wide tri-gate structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

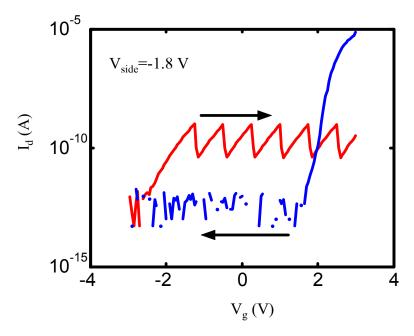

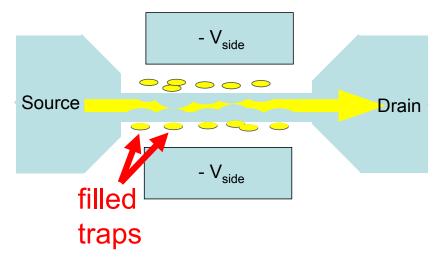

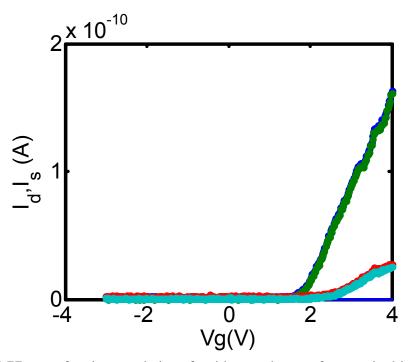

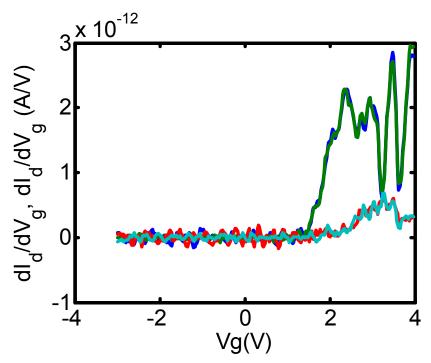

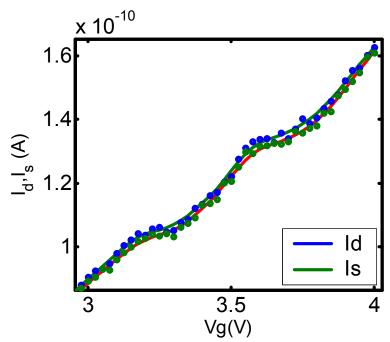

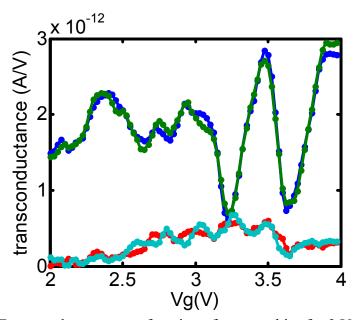

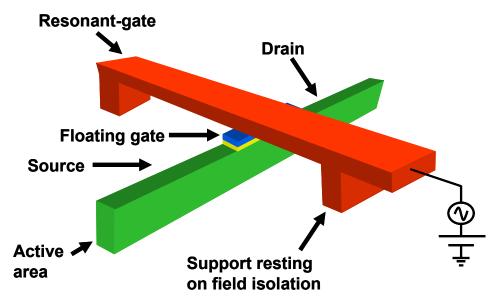

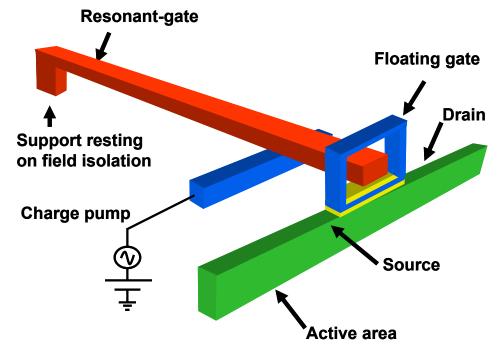

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |